目录

1. 软件链接

2. 为什么要使用Modelsim

3. Modelsim仿真工程由几部分组成?

4. 上手实例

4.1. 新建文件夹

4.2. 指定目录

4.3. 新建工程

4.4. 新建设计文件(Design Files)

4.5. 新建测试平台文件(Testbench Files)

4.6. 更改文件的默认打开方式

4.7. 编写设计文件

4.8. 编写测试平台文件

4.9. 编译仿真文件

4.10. 配置仿真环境

4.11. 开始仿真

1. 软件链接

链接:https://pan.baidu.com/s/12EX1wT0NshjRE4aa6_e83w

提取码:lny1

2. 为什么要使用Modelsim

验证设计逻辑:在将设计下载到FPGA之前,需要确保逻辑设计是正确的。ModelSim等仿 真软件可以模拟FPGA硬件的行为,允许设计者在实际硬件实现之前检查和验证HDL(硬件 描述语言)代码的功能正确性。

调试方便: 在FPGA开发过程中,调试是一个复杂且耗时的过程。使用ModelSim可以在仿真环境中进行调试,通过波形查看和分析信号的变化,更容易找到问题所在,而不必依赖于物理硬件的限制。

节省成本: 如果直接在硬件上进行调试,可能会因为设计错误而损坏硬件,特别是在高频率操作或电源管理不当的情况下。在仿真环境中验证设计可以避免这种风险,从而节省成本。

加速开发过程: 仿真可以并行于硬件的准备和生产过程,这样可以在硬件还未准备好的时候就开始软件的开发和测试,加快整体的开发流程。

支持复杂测试场景: 在ModelSim等仿真工具中,可以构造复杂的测试场景来验证设计在各种条件下的表现,这些场景在实际硬件上可能难以实现或者需要大量的时间和资源来构建。

性能分析: 通过仿真可以对设计的性能进行预测和分析,如时序分析、功耗估计等,帮助设计者优化设计。

支持自动化测试: ModelSim等仿真工具通常支持自动化测试脚本,可以大量减少手动测试的工作量,提高测试的覆盖率和效率。

支持多级别仿真: ModelSim支持从单个模块到整个系统的不同级别的仿真,设计者可以逐步扩展测试范围,逐步验证整个设计。

总结来说,ModelSim仿真工具在FPGA开发中的使用,主要是为了提高设计的可靠性、调试的效率和降低开发的风险和成本。通过在软件层面上对设计进行充分的验证和测试,可以确保将设计下载到硬件上时能够正常工作,从而提高整个项目的成功率。

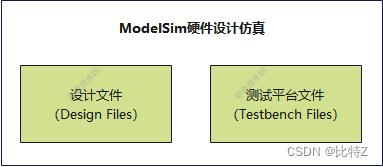

3. Modelsim仿真工程由几部分组成?

在使用ModelSim进行硬件设计仿真时,通常会涉及两类主要的文件:设计文件(Design Files)和测试平台文件(Testbench Files)。

设计文件(Design Files): 这些文件包含了硬件设计的实际代码,通常是用硬件描述语言(HDL)如VHDL或Verilog编写的。设计文件定义了电路的结构和行为,包括模块、寄存器、逻辑门等。在设计文件中,描述硬件应该如何响应不同的输入信号。

测试平台文件(Testbench Files): 测试平台文件是用于验证设计文件是否正确的环境。它们也是用HDL编写的,但与设计文件不同,测试平台不会在最终的硬件产品中实现。测试平台的目的是生成一系列测试信号(输入给设计文件),并观察输出是否符合预期。测试平台通常包含模拟输入信号的代码,可能还包括用于检查输出并报告测试结果的断言和检查点。

在ModelSim中进行仿真时,通常会先编译设计文件和测试平台文件,然后在仿真环境中加载测试平台,最后运行仿真以观察并验证设计的行为。通过这种方式,可以在实际制造硬件之前,检测并修复设计中的错误。

4. 上手实例

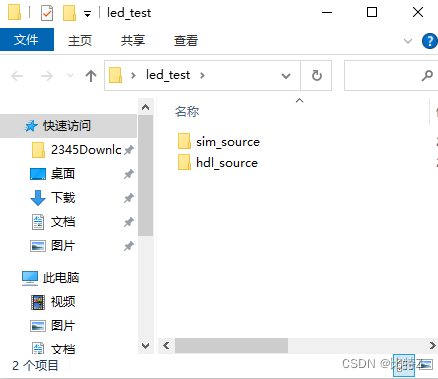

4.1. 新建文件夹

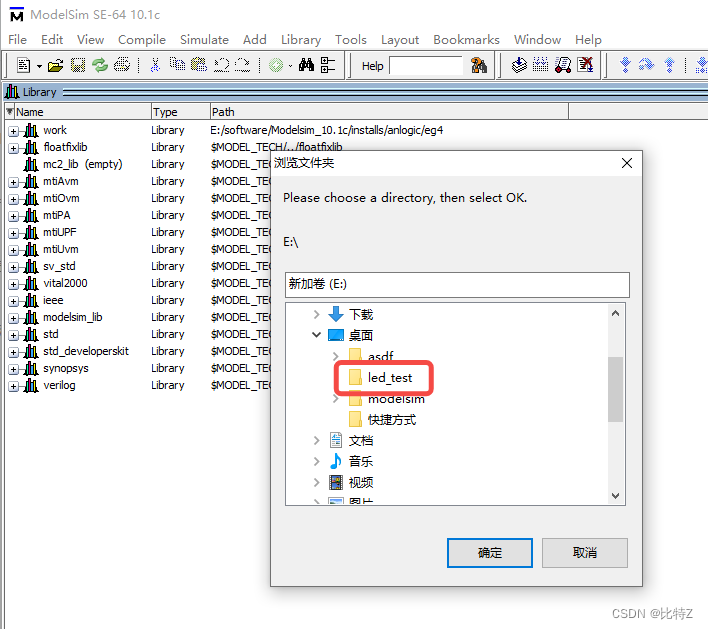

指定一个路径新建一个文件夹,用来存放将要仿真的文件。这里我在桌面新建了一个名为led_test的文件夹,并建立hal_source和sim_source两个子文件;

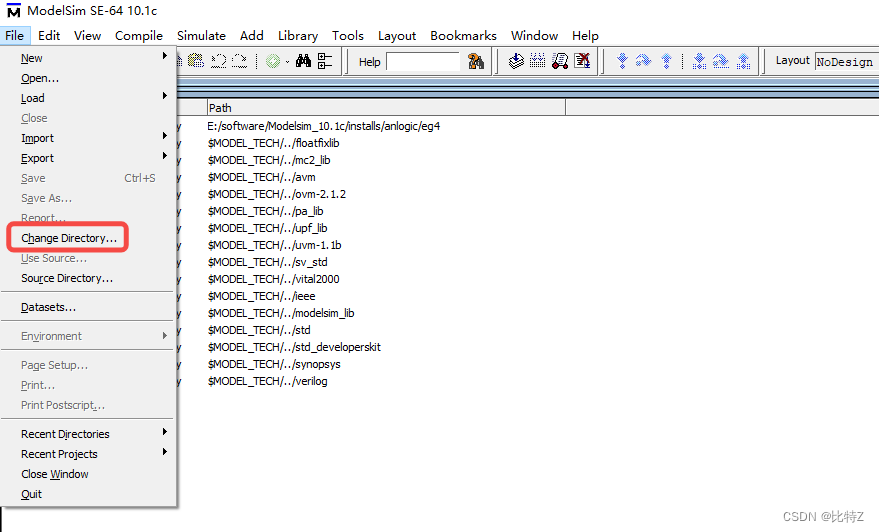

4.2. 指定目录

在编译和仿真过程中,ModelSim需要找到源代码文件和其他相关文件。如果没有正确设置工作目录,ModelSim可能找不到这些文件,导致编译或仿真失败。

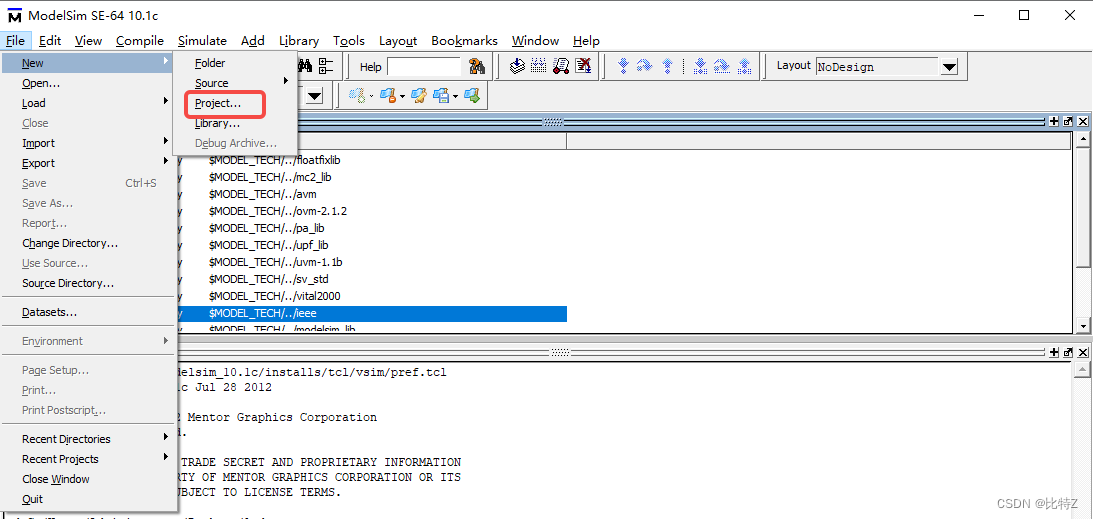

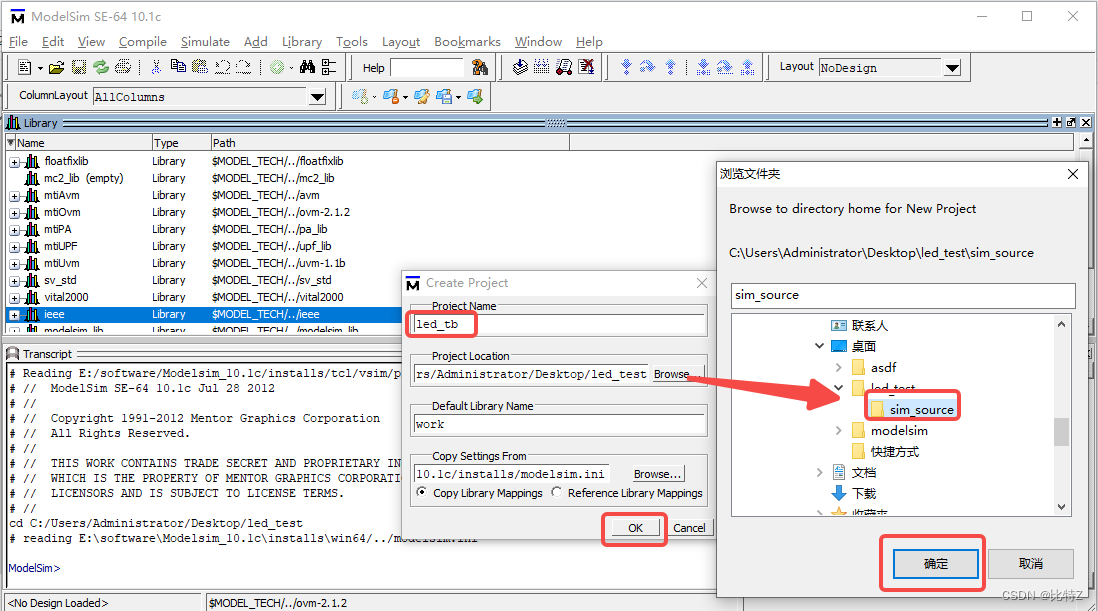

4.3. 新建工程

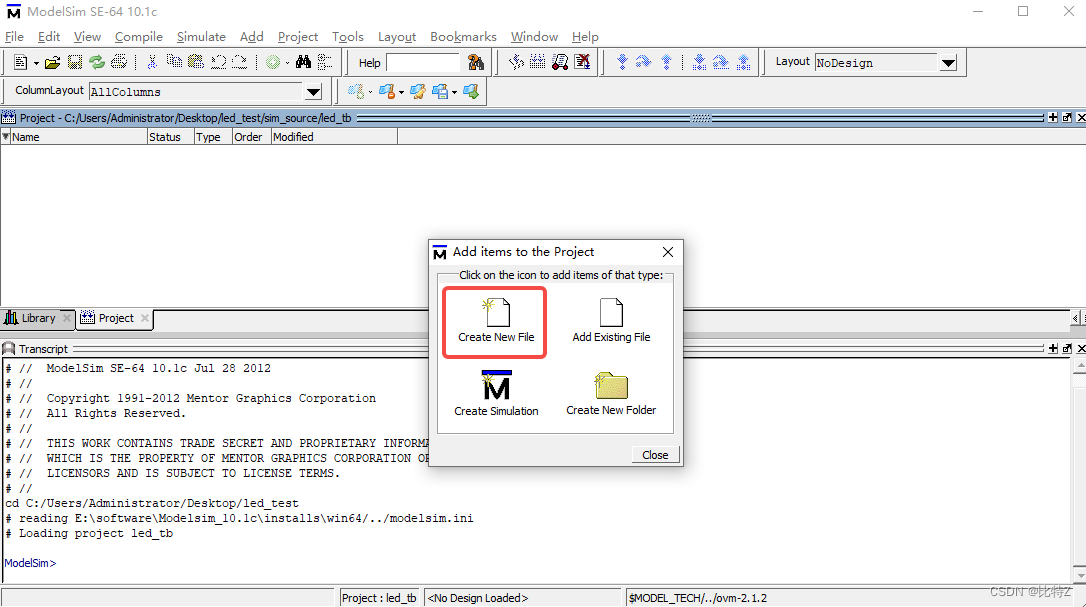

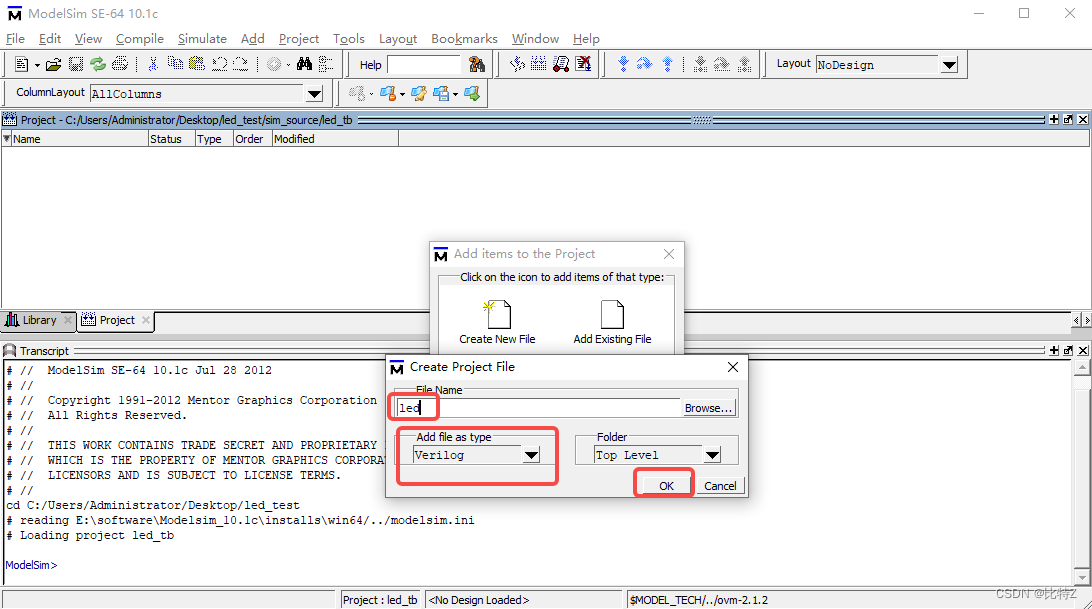

4.4. 新建设计文件(Design Files)

上面章节点击完OK后会弹出如下界面,选择Creat new file,并保存在led_test/hdl_source文件夹下。

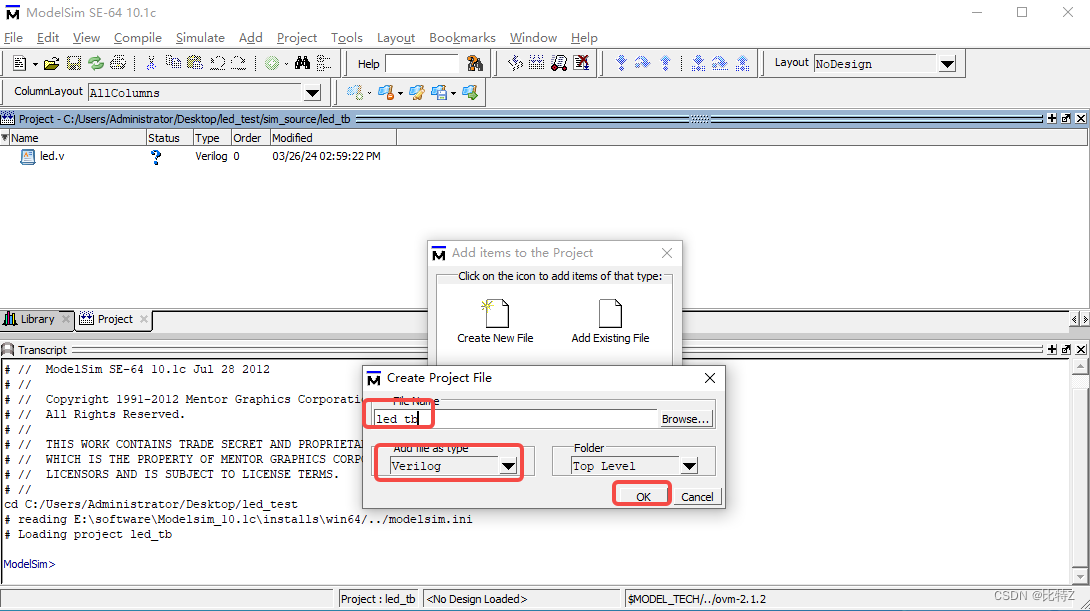

4.5. 新建测试平台文件(Testbench Files)

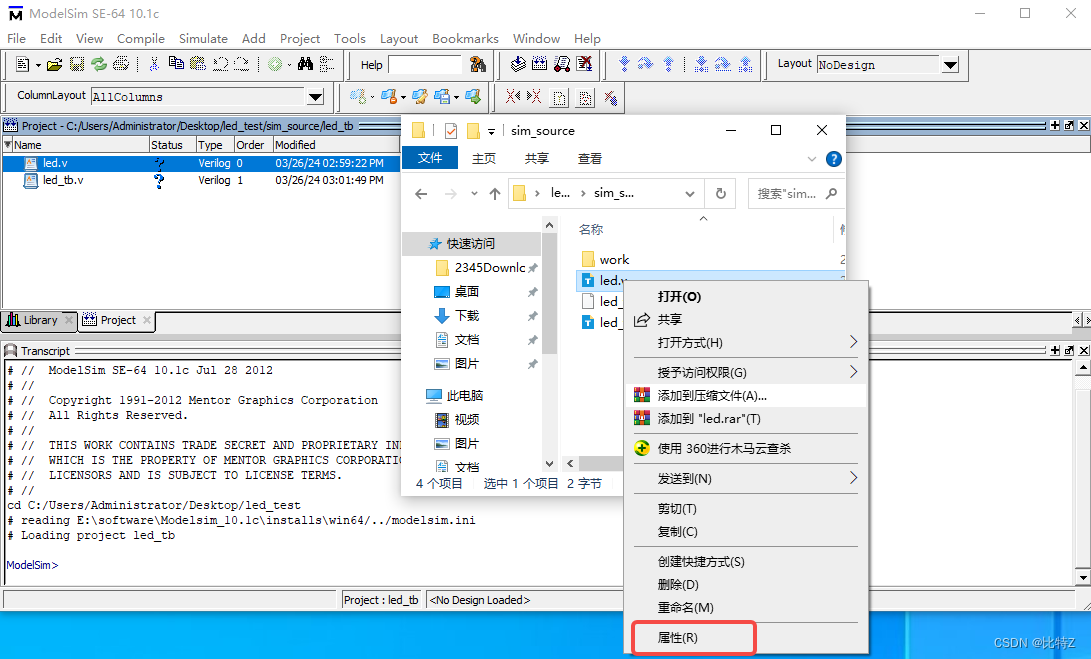

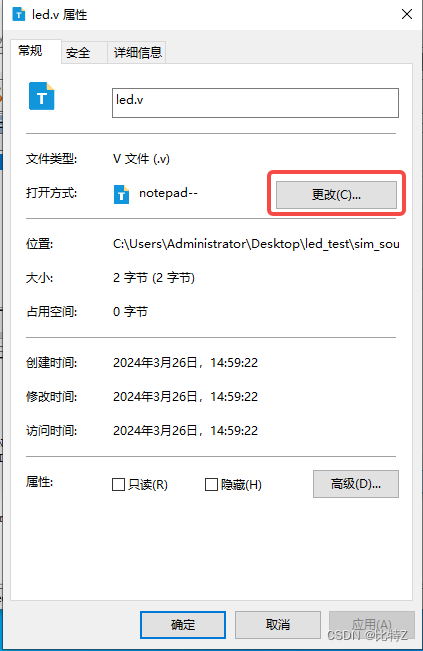

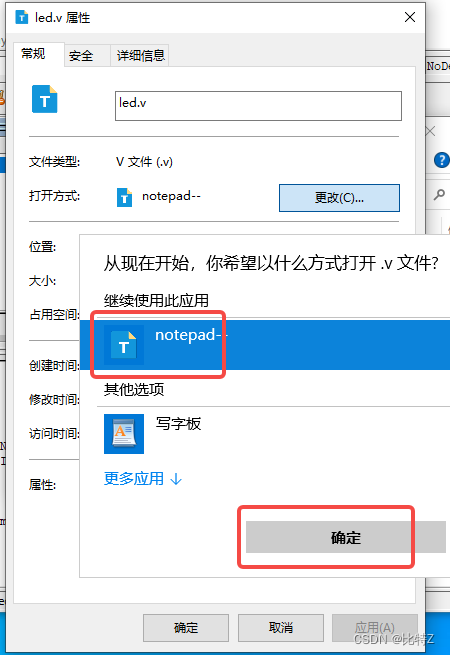

4.6. 更改文件的默认打开方式

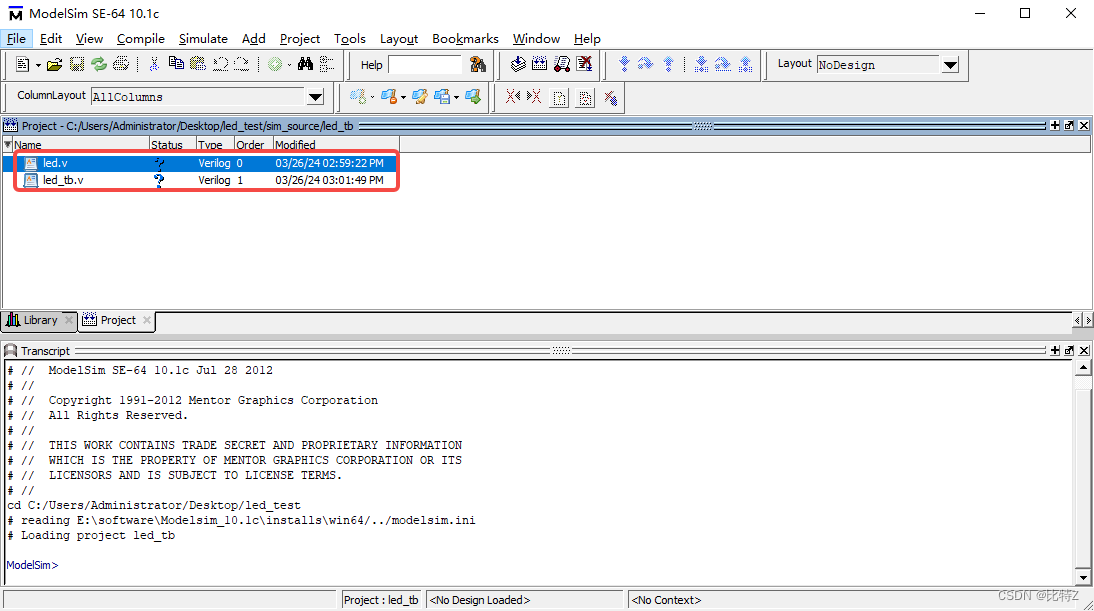

完成4.4和4.5后,软件界面会出现如下两个文件。

通常情况下,在此界面双击会默认使用笔记本工具打开。为了良好的编辑体验,这里更改为notepadd。下面介绍默认打开软件的设置方式。(前提:已安装notepad)

4.7. 编写设计文件

在modelsim界面双击打开led.v文件并插入以下代码

module flow_led(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output reg [3:0] led //4个LED灯

);//reg define

reg [23:0] counter;//*****************************************************

//计数器对系统时钟计数,计时0.2秒

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

counter <= 24'd0;

else if (counter < 24'd10)

counter <= counter + 1'b1;

else

counter <= 24'd0;

end//通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

always @(posedge sys_clk or negedge sys_rst_n) begin

if (!sys_rst_n)

led <= 4'b0001;

else if(counter == 24'd10)

led[3:0] <= {led[2:0],led[3]};

else

led <= led;

endendmodule

4.8. 编写测试平台文件

在modelsim界面双击打开led_tb.v文件并插入以下代码

`timescale 1ns/1ns // 定义仿真时间单位1ns和仿真时间精度为1ns

module flow_led_tb; // 测试模块

//parameter define

parameter T = 20; // 时钟周期为20ns

//reg define

reg sys_clk; // 时钟信号

reg sys_rst_n; // 复位信号

//wire define

wire [3:0] led;

//*****************************************************

//** main code

//*****************************************************

//给输入信号初始值

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0; // 复位

#(T+1) sys_rst_n = 1'b1; // 在第21ns的时候复位信号信号拉高

end

//50Mhz的时钟,周期则为1/50Mhz=20ns,所以每10ns,电平取反一次

always #(T/2) sys_clk = ~sys_clk;

//例化led模块

flow_led u0_flow_led (

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n),

.led (led )

);

endmodule

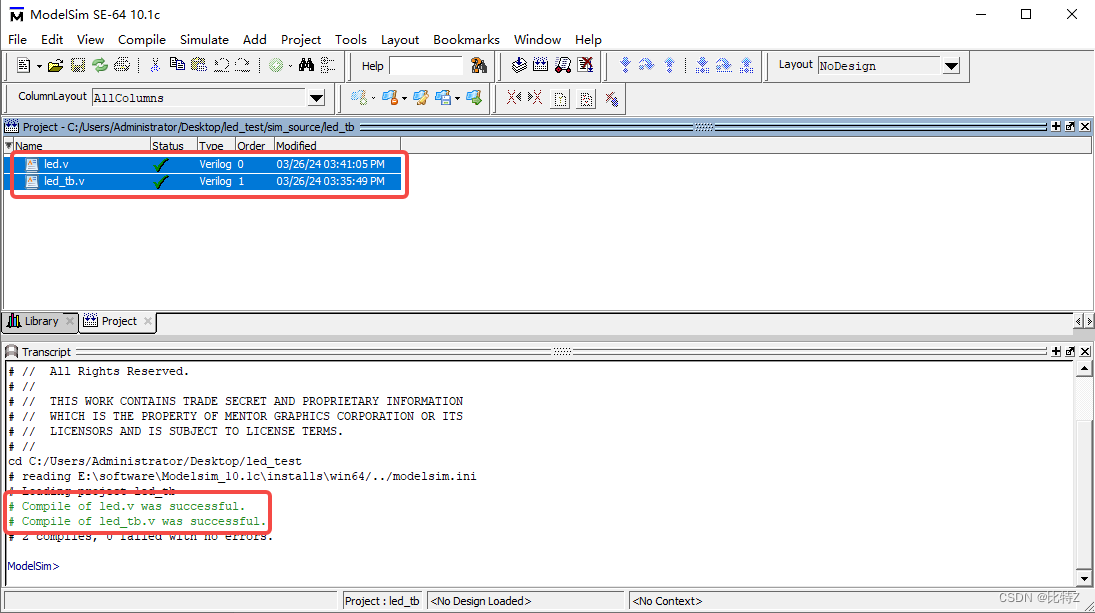

4.9. 编译仿真文件

开始编译

编译完成

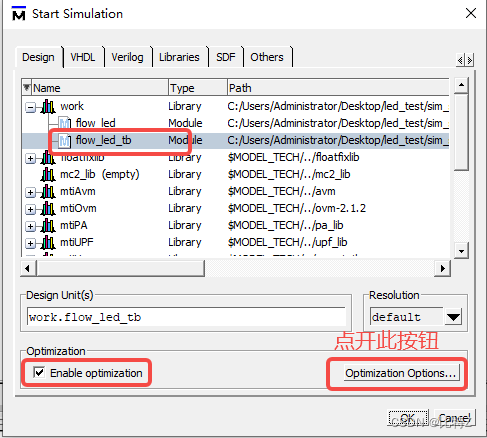

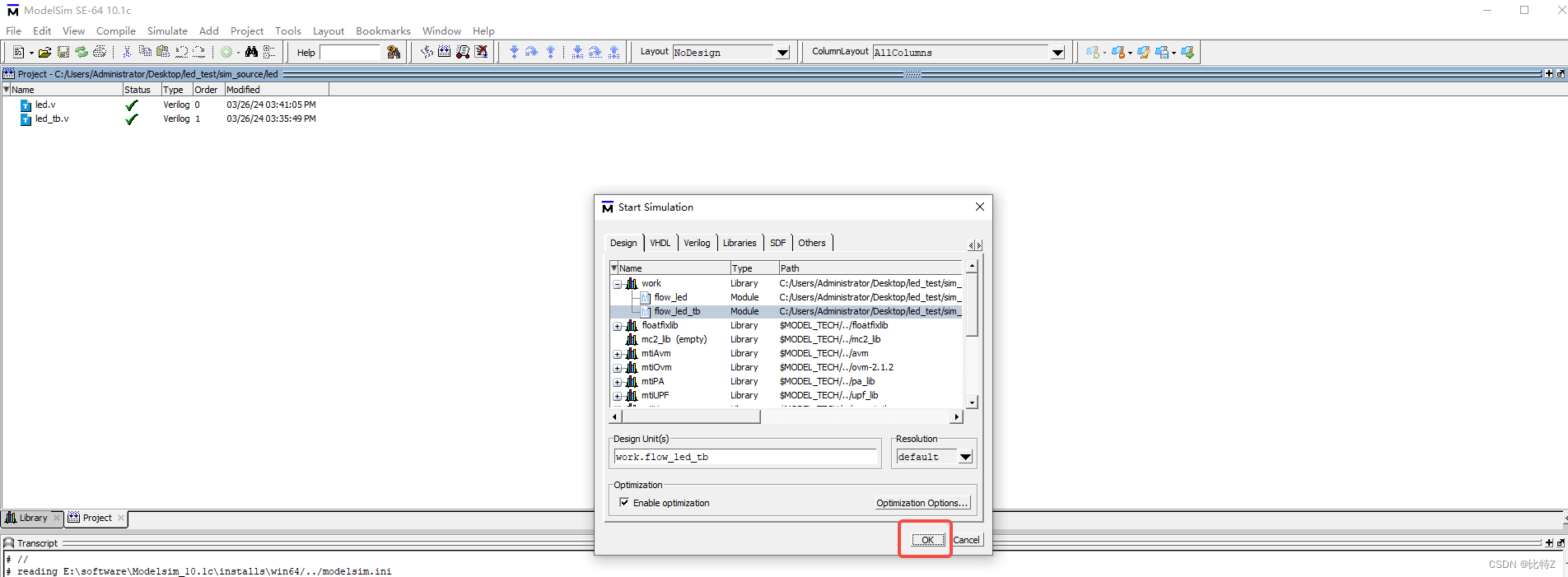

4.10. 配置仿真环境

4.11. 开始仿真

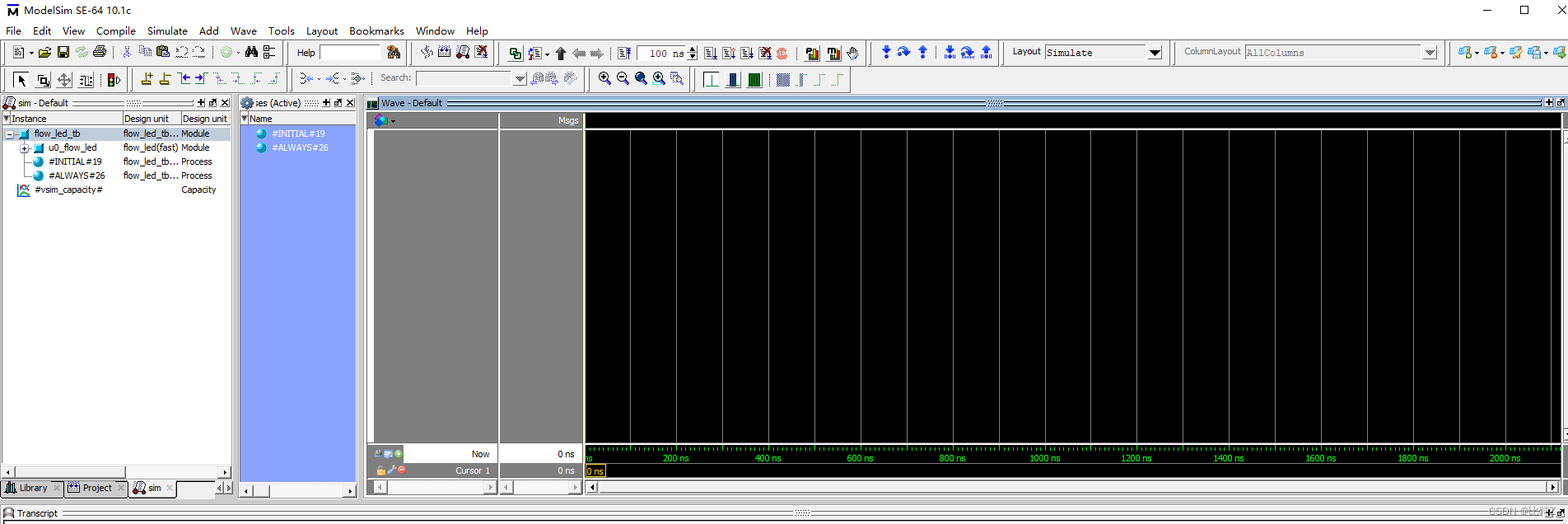

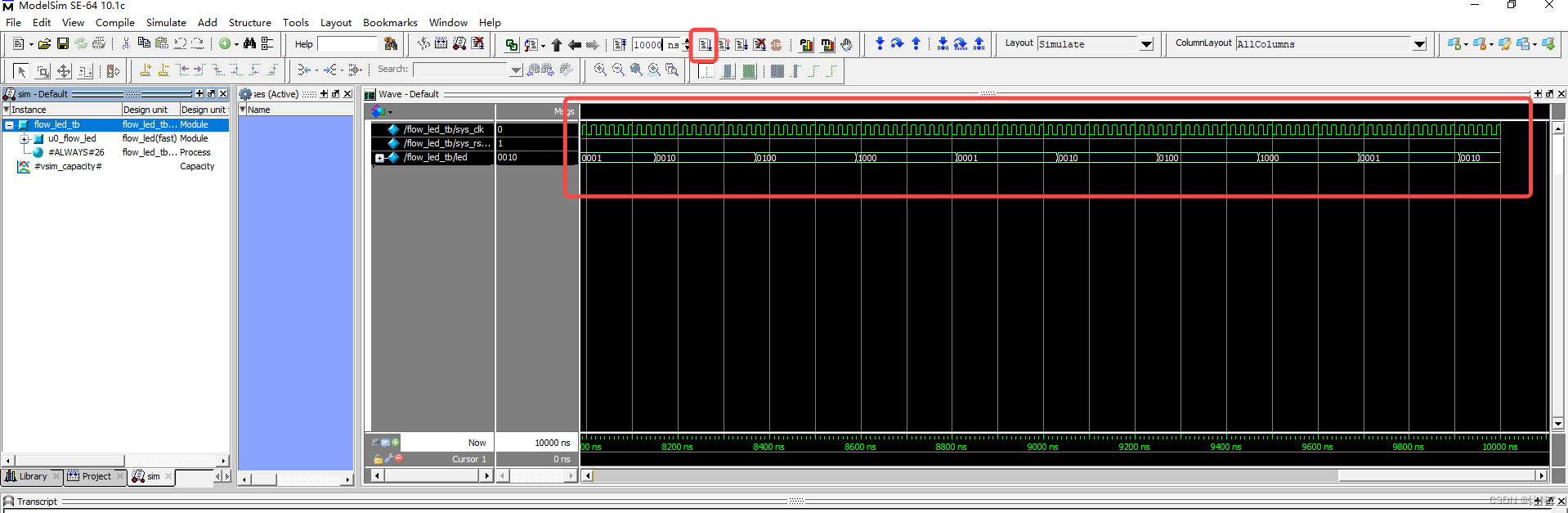

上一个章节配置完成后会出现以下仿真界面

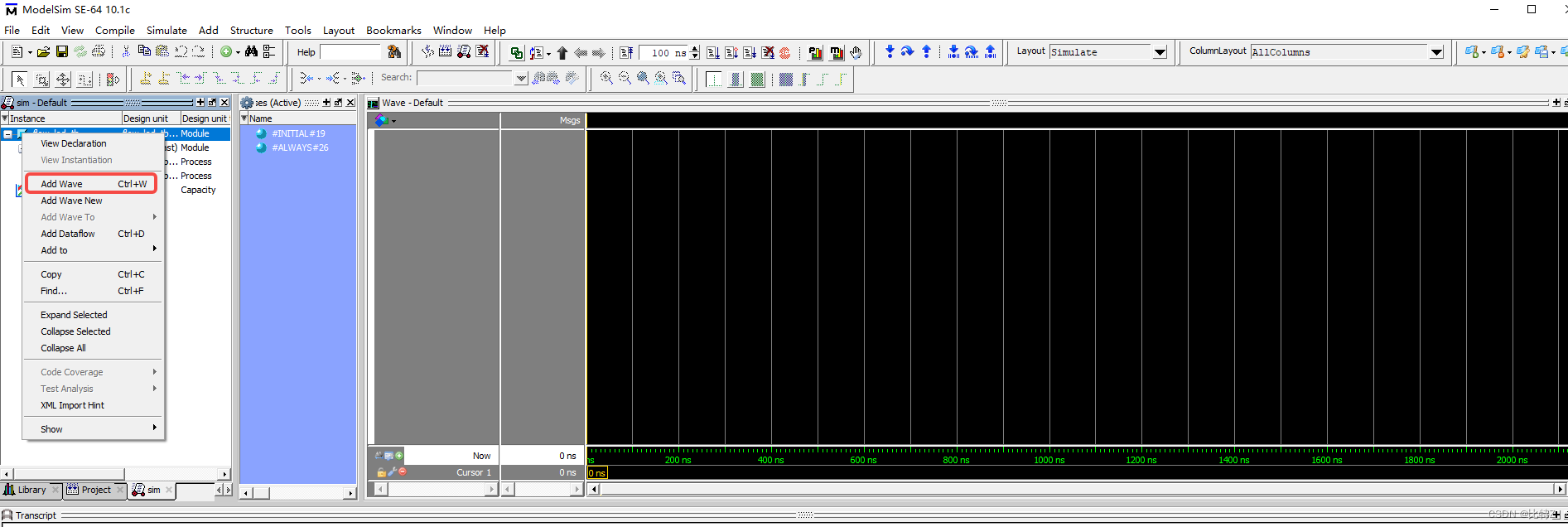

按照下图操作添加要观察的信号

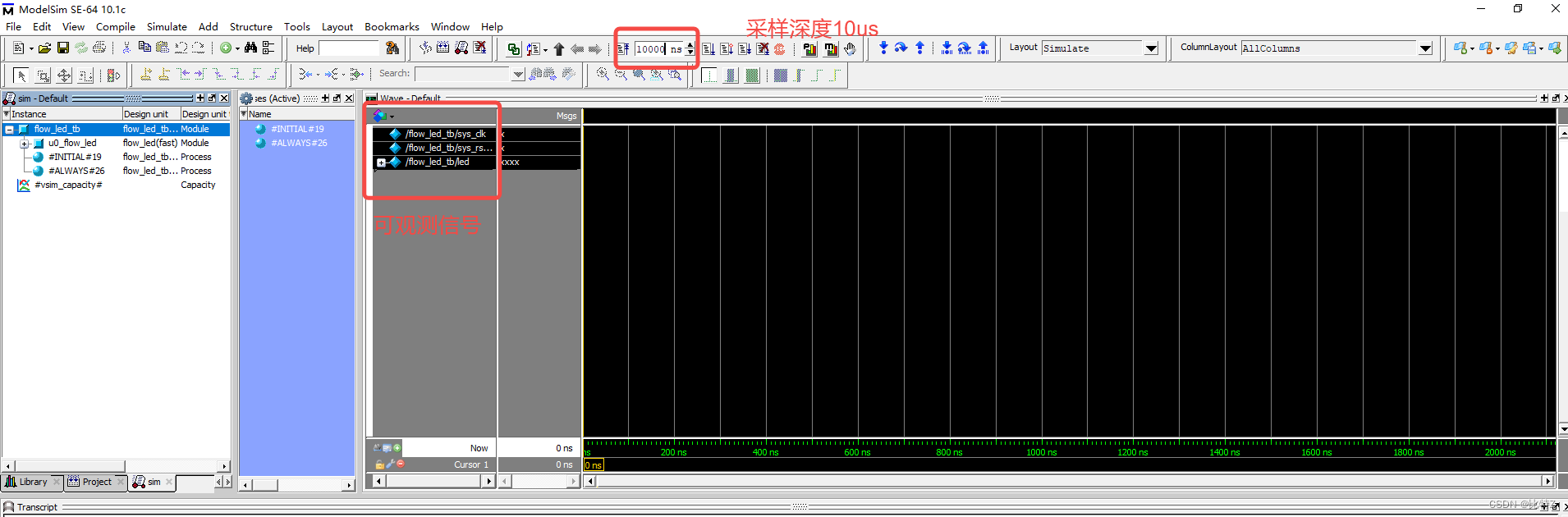

添加完,信号出现在可观察窗口。设置采样时间

开始仿真,输出可视化信号

回溯)

)

,附有道云笔记链接)