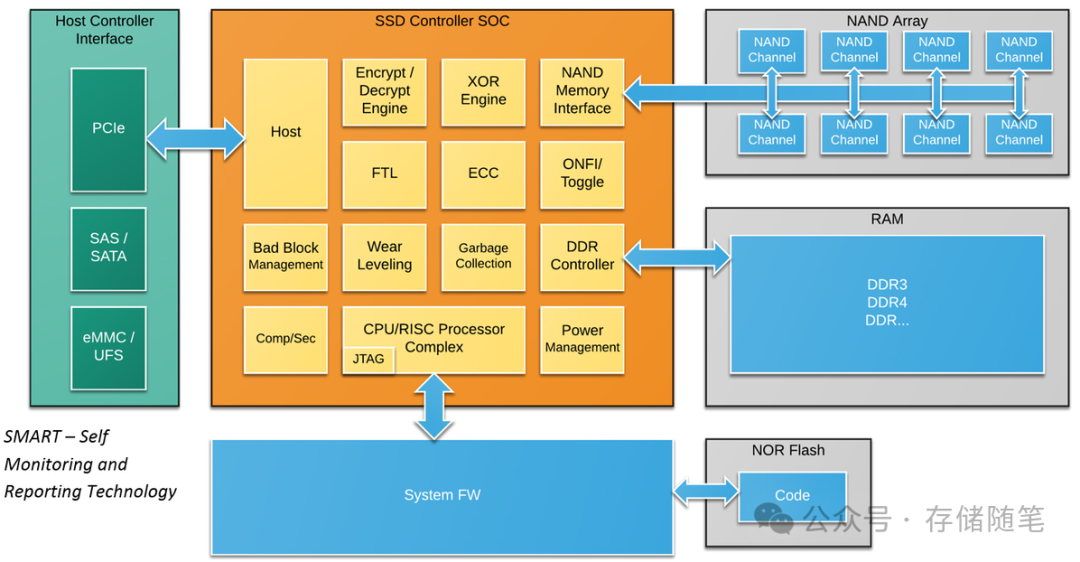

常见的SSD架构中,包括了SSD控制器、NAND颗粒、DRAM颗粒三大组件,SSD控制器的固件需要兼顾坏块管理、ECC纠错、垃圾回收GC、磨损均衡WL、NAND die介质管理、缓存交互等等。

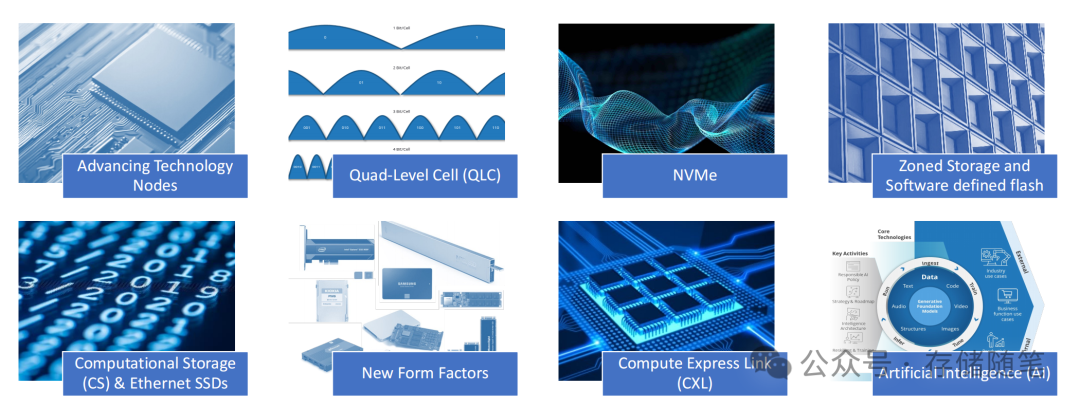

随着时代的发展,SSD架构,也不断有新的挑战和需求。基于小编目前的看到的信息,总结大概有几个方面:

首先就是性能与功耗问题。

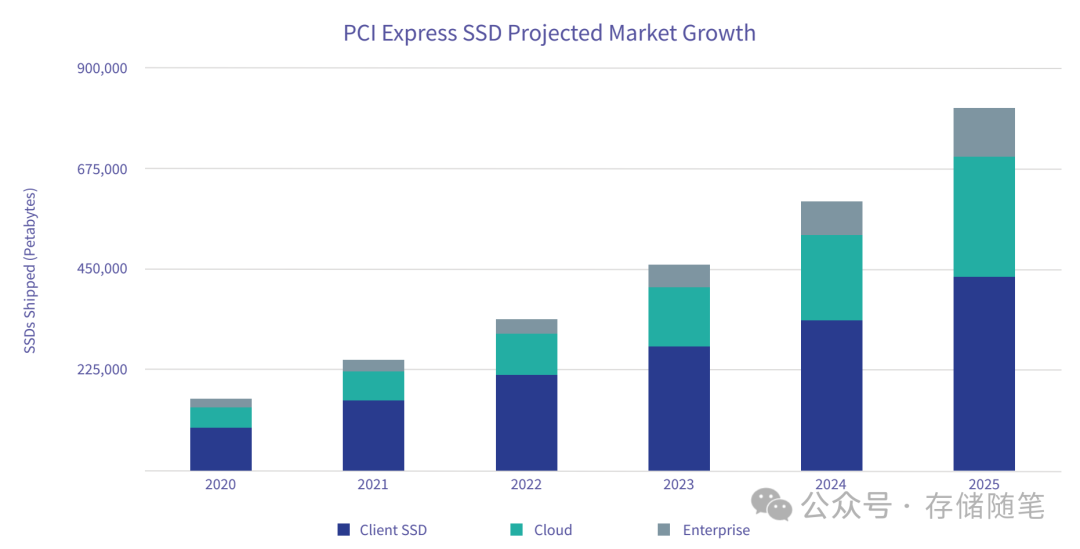

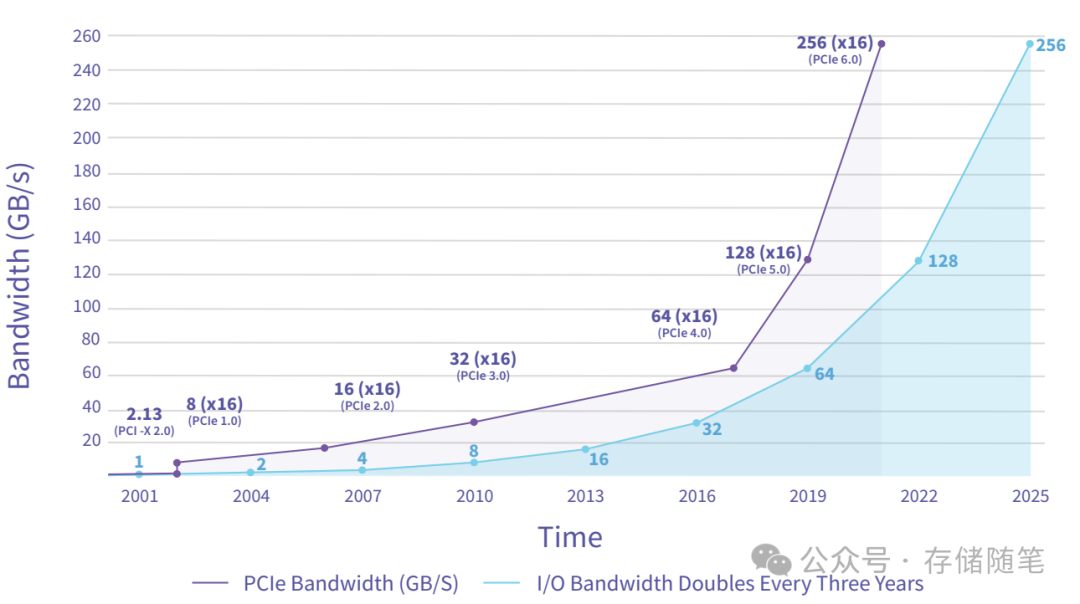

随着数据中心对存储设备速度要求的不断提升,SSD需要提供更高的IOPS(每秒输入输出操作次数)和带宽(GBPS),同时在保证高性能的同时必须有效控制功率消耗,实现单位性能所需的能耗降低(如IOPS/Watt或GBPS/Watt)。协议接口和NAND接口速率是最大助力点。

为了追求高性能,NVME/PCIE SSD是数据中心的高性能标配,NVME/PCIE SSD在数据中心的占比还在继续攀升。

pcie协议5.0还没完全普及,pcie 6.0 spec已经发布,pcie 7.0 spec也在路上了,这个世界都在狂奔。

扩展阅读:

-

浅析PCIe 6.0功能更新与实现的挑战

-

PCIe 6.0生态业内进展分析总结

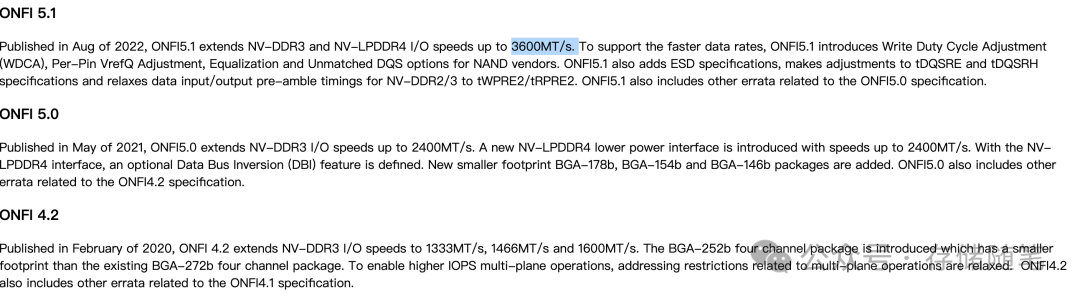

NAND ONFI接口速率也提升至了3600MT/s.

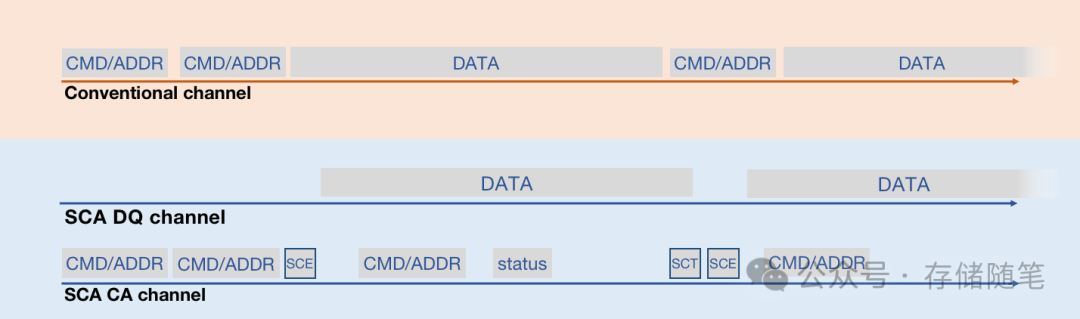

尽管NAND闪存接口速度不断提升,但由于命令和地址传输机制的局限性,实际应用中总线资源的利用率并未随速度提升而同步增长,反而出现了效率降低的问题,这对未来系统优化设计提出了新的难题。

当前,面对这一挑战,固态技术协会JEDEC正在深入讨论下一代协议的进化方向,除了继续提高接口速度外,还将优化命令和地址的传输模式,这无疑将给主控芯片的设计带来新的考验。

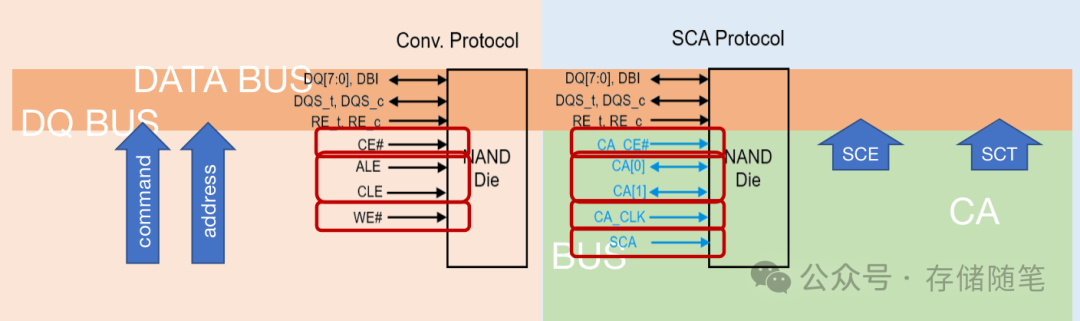

在Separate Command Address (SCA) 接口中,设计思路发生了根本性的变化。SCA接口将命令和地址信号与数据传输分离开来,增加了专门的CA(Command and Address)通道,而不是像传统接口那样混用I/O线传输命令、地址和数据。

扩展阅读:如何解决NAND系统性能问题?

它的主要原理在于将传统的命令和地址(CMD/ADD R)信号与数据传输(DATA/DQ)信号分离到不同的通道上,即创建了专门的SCA CA通道用于命令和地址的串行传输,而DQ通道专注于数据的并行传输。

通过这种方式,SCA接口不仅简化了布线和电路设计,还优化了控制器与NAND闪存之间的交互,允许更高级别的命令交错执行,从而显著提升固态硬盘(SSD)的并行操作能力和整体性能。

其次,是容量的需求。

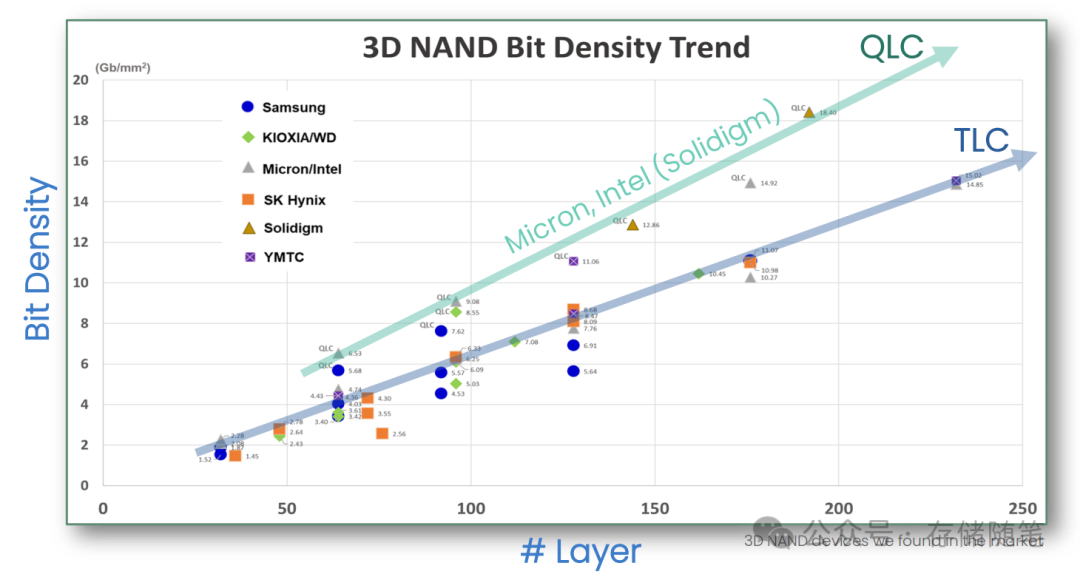

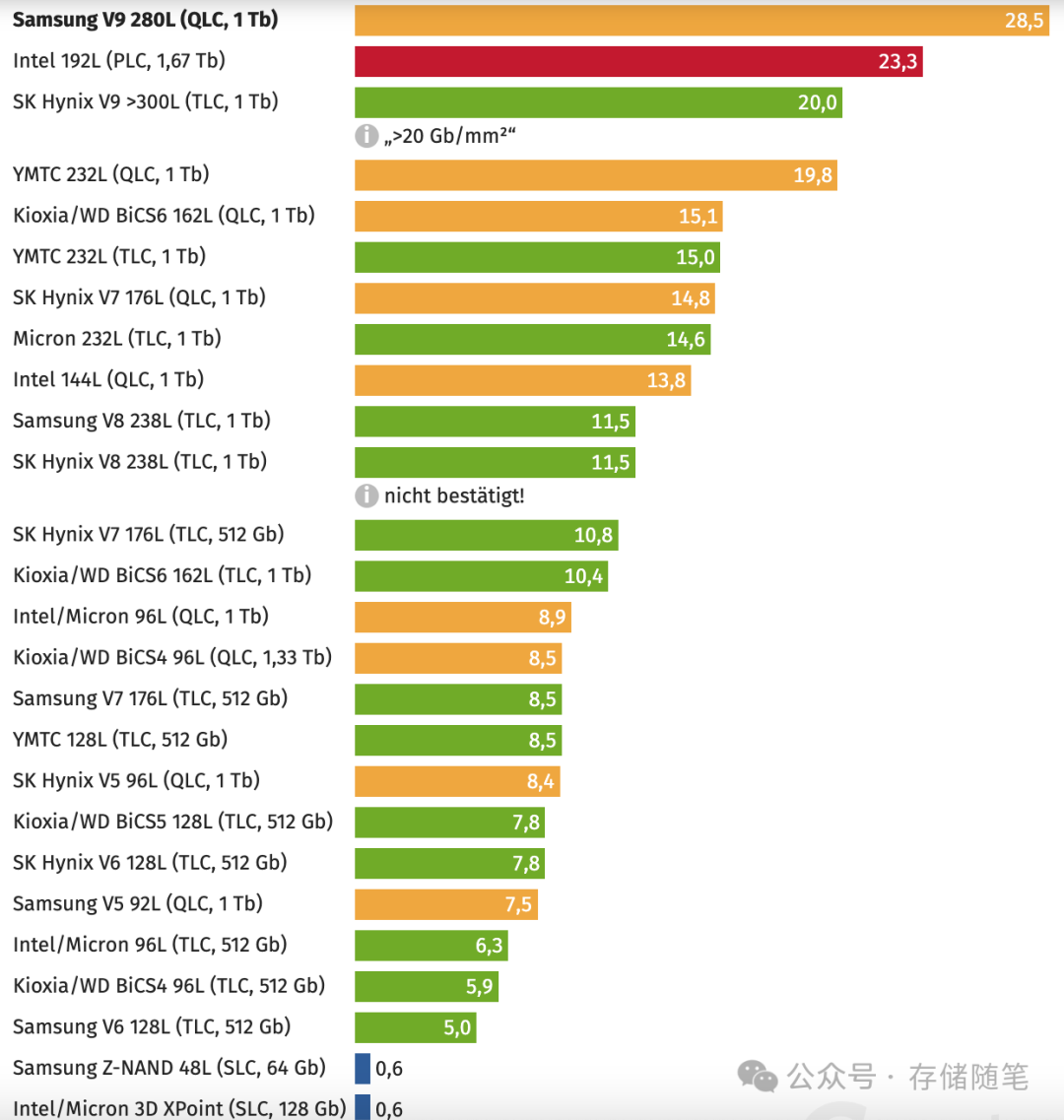

随着数据量的急剧增长,企业对存储空间的需求持续增加。这要求SSD不仅要有更大的存储容量,还要能在不牺牲性能的前提下,通过技术改进如3D NAND等提高闪存密度。不同NAND原厂 3D NAND Bit Density对比:

在2月份刚刚举行的2024年IEEE国际固态电路会议(ISSCC)上,三星也公布新一代QLC闪存芯片,采用280层堆叠设计,实现了每平方毫米28.5Gb的高密度存储。信息显示该闪存拥有1Tb的单Die容量,面积密度高达28.5 Gb/mm²(如下图,市面上的存储密度排行来看,三星这个存储密度排名第一),传输速率达到了3.2 GB/s,相较于当前市场常见的传输速度为2.4 GB/s的3D NAND闪存有了较大的提升。

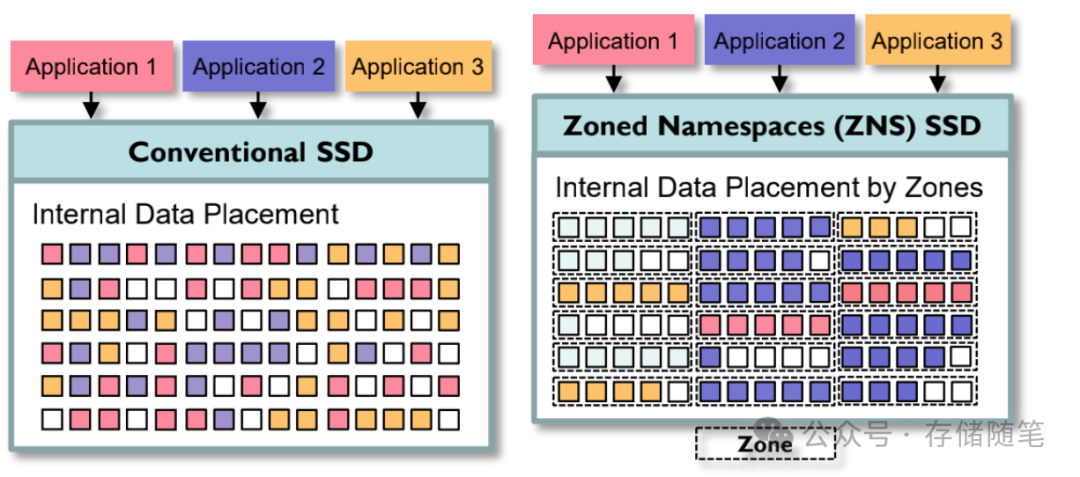

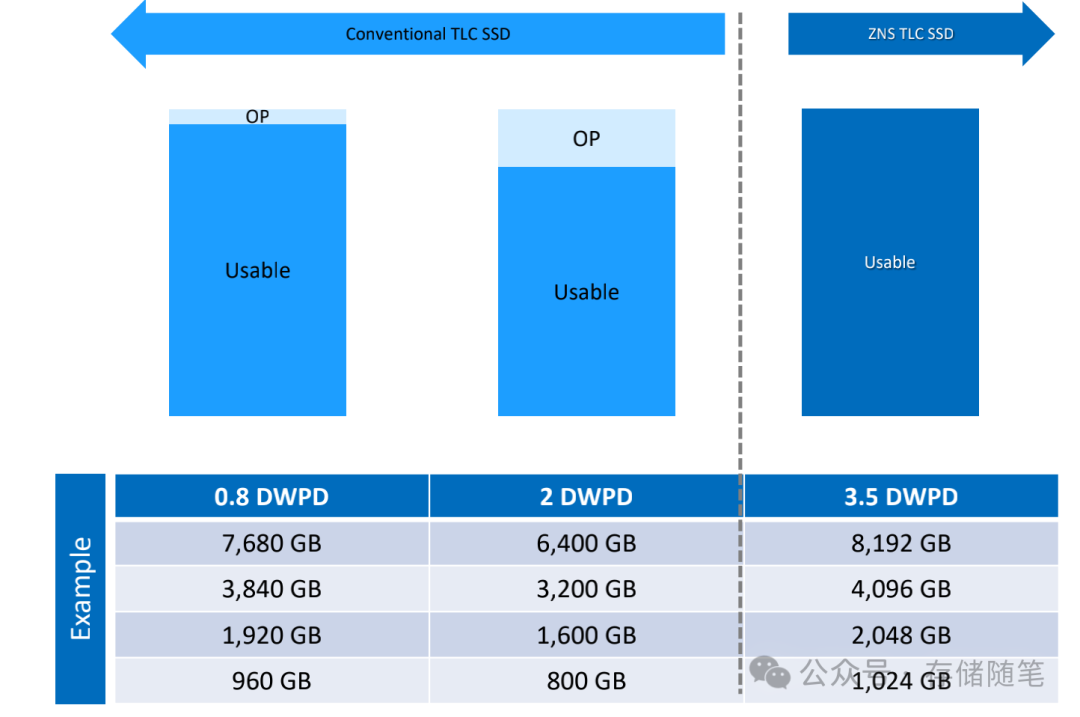

此外为了QLC的普及,ZNS也是拼尽全力。在ZNS的场景下,不同应用按照Zone配置信息,相应存放业务数据。由于是Host管理数据的摆放和存取位置,会最大程度减少GC垃圾回收。降低SSD内部的写放大,提升SSD的寿命。

减少SSD的DRAM空间和去掉OP冗余空间,提升用户可用的容量。

扩展阅读:

-

为什么QLC NAND才是ZNS SSD最大的赢家?

-

字节跳动ZNS SSD应用案例解析

-

NVMe SSD:ZNS与FDP对决,你选谁?

- dtb格式)

)

)

)

: flinkSQL 顶层 API ——实时数据流转化为SQL表的操作)

的算法与源代码)