AC耦合电容,也叫DC blocking隔直电容,在几乎所有的高速串行链路中,都可以看到它的身影,它的主要作用是去掉信号中的直流偏置分量,同时让高频分量可以顺利通过,类似于一个高宽带的滤波器。

由于电容的焊盘通常都要比传输线的宽度要细,在电容这里会形成一个阻抗偏低点,提升这个阻抗,是电容仿真优化的重点。

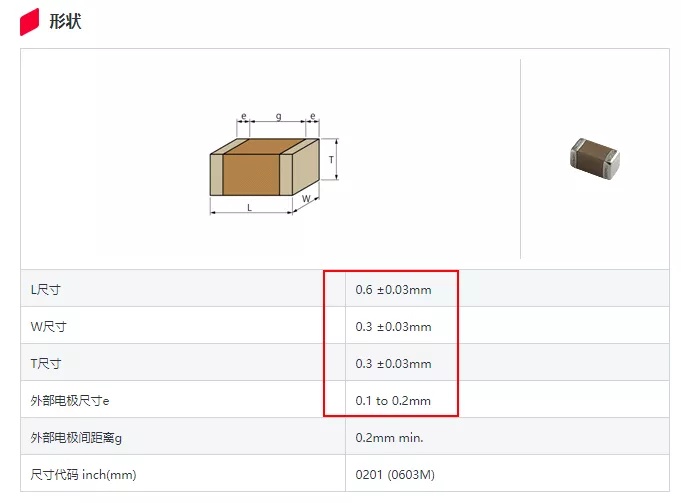

为了减小阻抗失配,会选用封装比较小的电容,目前高速PCB中,0201和01005封装的电容用的比较多,一般都是MLCC(Multi-layer Ceramic Capacitor )多层陶瓷电容,因为使用的是多层电极叠加结构,高频时电感非常低,具有非常低的等效串联电阻,损耗小。

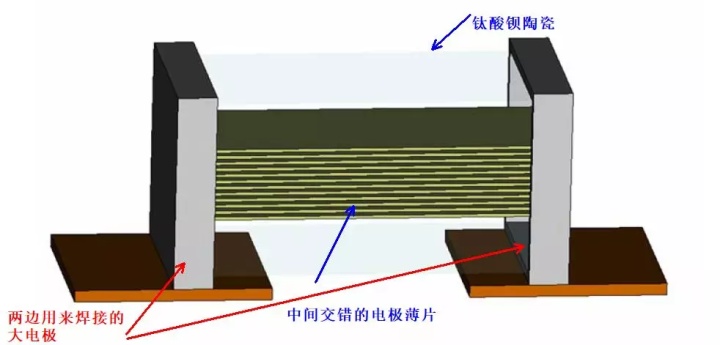

MLCC电容结构参考图一:两边是用来焊接的大电极,镀镍,镀锡,中间的陶瓷介质是钛酸钡,中间包裹着相互交错叠加的电极薄片,容值大小不同,电极的数量就不同。图二是0201封装电容尺寸,从村田官网截的图。

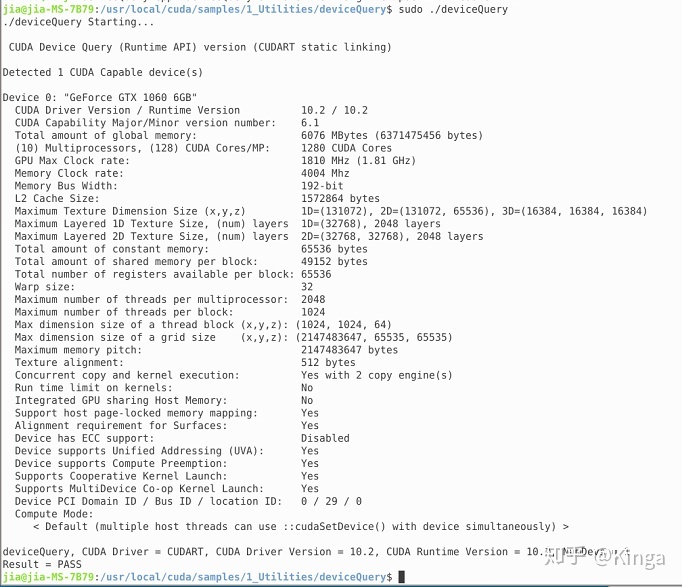

AC耦合电容仿真,如果能拿到具体的MLCC模型最好不过了,但是像陶瓷的介电常数、内部电极数量这些参数对厂家来说都是机密,一般人是没法拿到这些数据的,就算有这些尺寸,因为内部电极的厚度不过1~3um,这种薄片在HFSS中仿真,会划分非常多的网格数,耗费很多的CPU和内存资源,仿真时间很长,因此MLCC模型不太适合直接用来仿真。

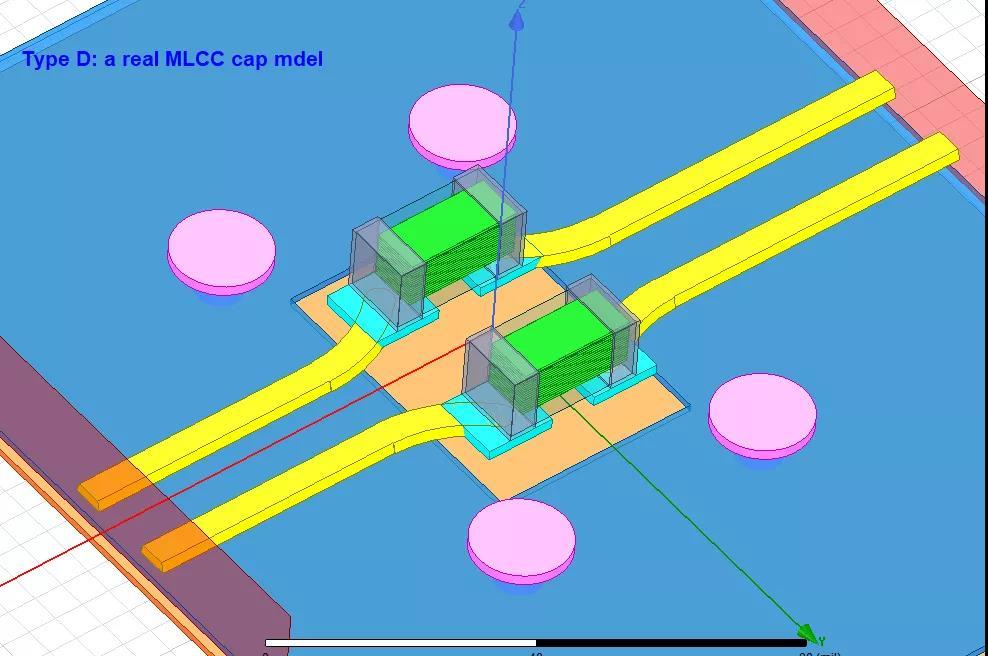

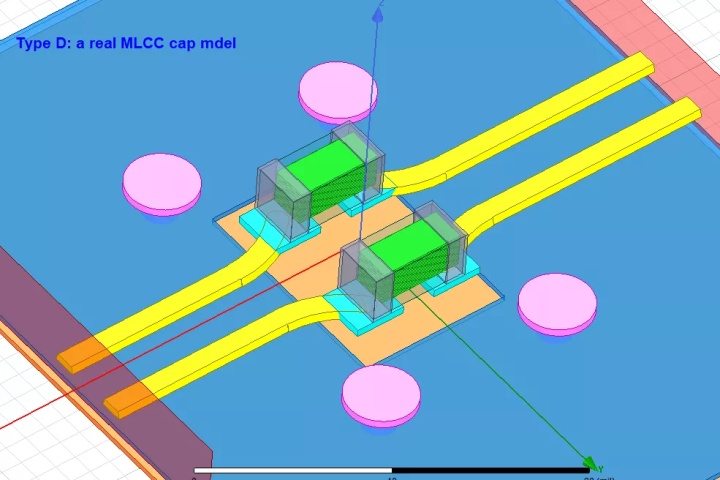

当然,这也并非绝对,samtec的大神就发表了关于用MLCC陶瓷电容仿真56Gbps和112Gbps PAM4的论文,有兴趣的可以去了解下文末的参考资料,但是对普通的仿真者来讲,技术难度还是比较大,图三是我根据论文建立的MLCC模型,因为仿真出来的SDD21曲线有很多谐振,就不过多分享了,毕竟结果不正确。

既然利用真实的MLCC模型仿真行不通,那么就得找到一些相对简单的模型来进行电容阻抗的优化。基于此模型,仿真出来的阻抗(TDR)应该与测试的TDR很接近,不然仿真模型也没有意义,凡是与测试结果差异很大的模型都无效,必须通过多次校准来完善模型。我自己建立的电容模型有6种,分别为:

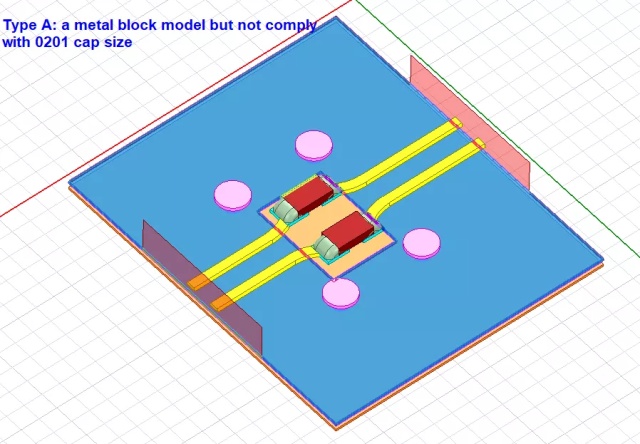

- 第一、type A——就是一个金属块模型,见图四,它不是标准的0201封装尺寸,这个模型是我校准过的模型,近期的一些测试发现它的精度还不够,要继续完善;

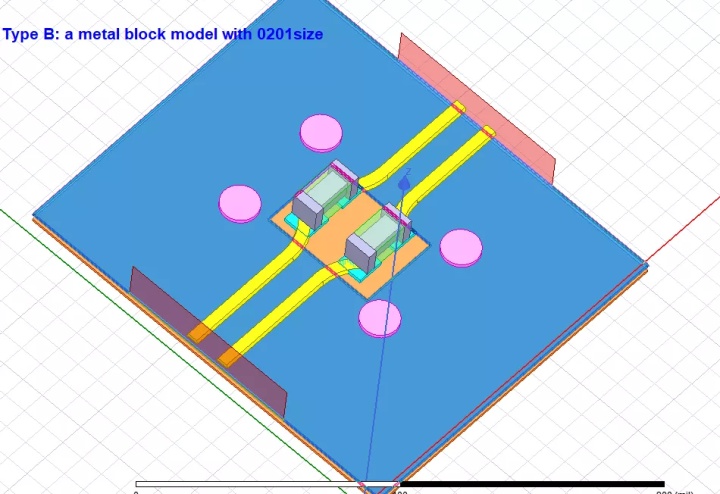

- 第二、type B——是一个标准0201封装尺寸的金属块模型,中间的block尺寸可调,需要基于实测TDR,见图五;

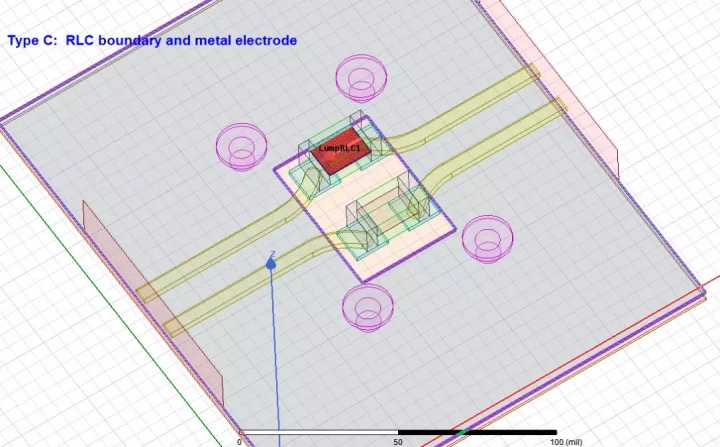

- 第三、type C——这个模型是HFSS help提到的一种,保留电容两边的金属电极,中间加了一个0.1uF电容边界条件,见图六;

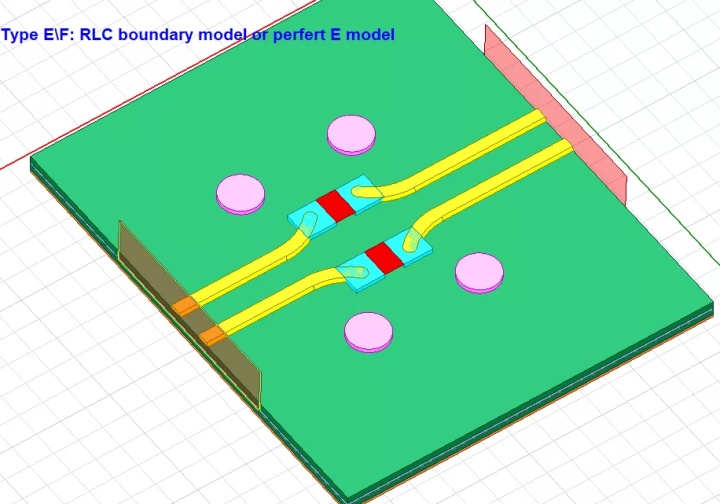

- type E/F——这是很多人常用的电容模型,用一个RLC boundary或者perfect E直接替代电容,见图七;

- type D——就是真实的MLCC电容模型,参考图三,因为仿真结果不对,仅分享下图片;

以上6种模型,除type D还有错误不参与比较外,哪一种模型跟实际的模型会更接近,或者说用它仿真得到的结果更准确?我们不能主观上判定哪一个更准,需要基于严格的仿真或者测试数据。

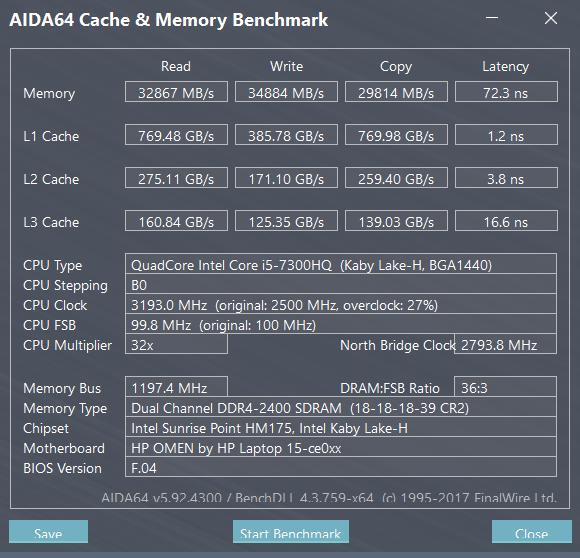

上面的几个模型,使用HFSS进行仿真,求解方式为drivern terminal,插值法宽带扫描并且使用的wave port的deembedding,求解频率设置为DC~75GHz,对应信号的上升沿时间为15ps。

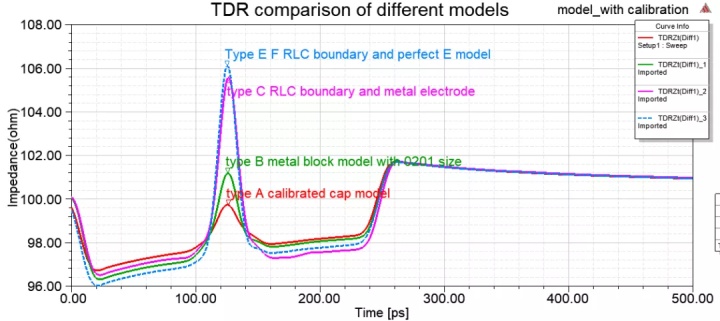

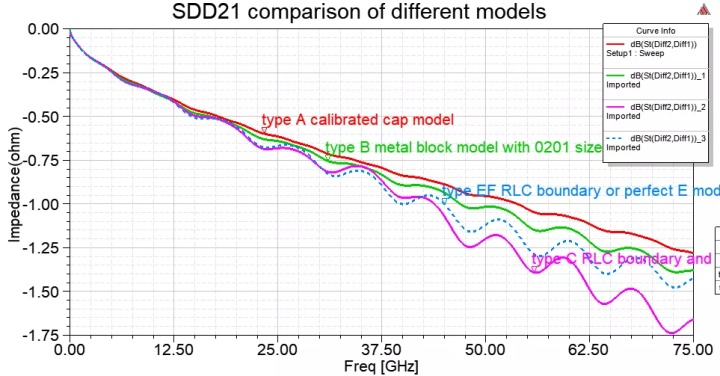

对比使用不同电容模型时的TDR曲线,其中尖峰前后两段较平坦的曲线为差分对的阻抗,尖峰为电容阻抗,从图八可以看出,同样的传输结构,使用不同的电容模型,仿真出来的阻抗差异还是很大的,Type A和Type B两种模型仿真出来的阻抗更接近,而使用边界条件的模型,阻抗要比纯金属的模型阻抗大5ohm左右。

再来看通道的插损insertion loss,也就是SDD21的差异,请看图九,当频率小于12.5GHz,可以认为模型间基本没差别,因此低速信号的仿真(<10Gbps),这几种模型都是可以使用的,但是到了高频尤其是20GHz以后,性能的差别就出来了,还是校准过的模型type A损耗最小,其次是type B,使用边界条件的模型损耗偏大,这跟电容这里的阻抗偏高(106ohm)有关系。

上面的仿真数据对比说明,使用不同的电容模型,当频率(>20GHz)高了以后,性能差异还是很大的。低速率时代(<10Gbps),使用任何一种模型都没问题,当速率高了以后,就不建议直接使用边界条件电容模型,因为它们不会呈现导体加厚后的寄生电容效应,以及电容本身与GND的电容效应,此时建议使用type A和Type B这两种模型,对应的金属block尺寸要经过严格的测试校准。

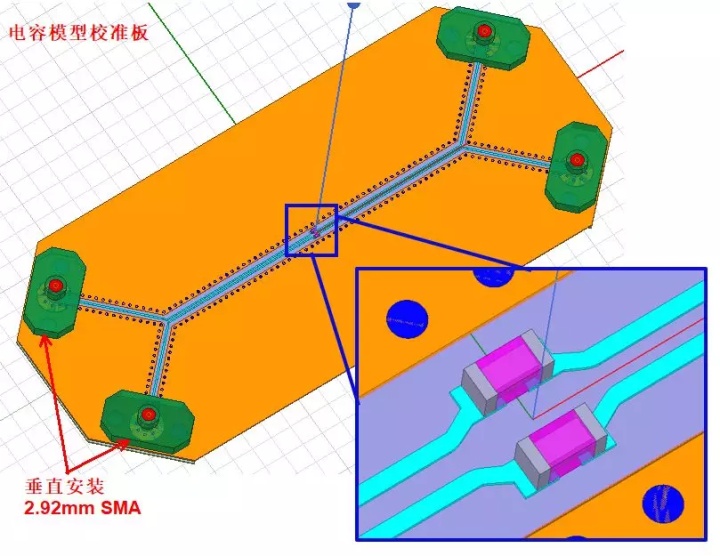

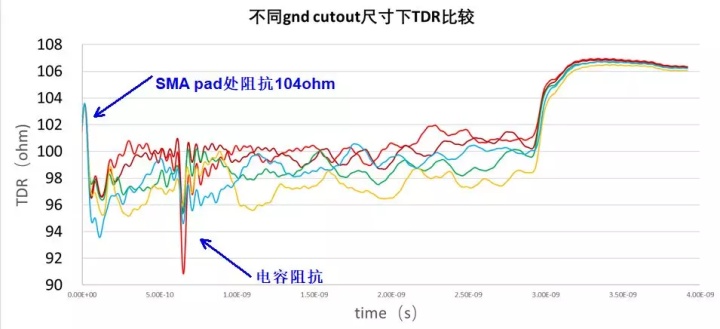

因此你需要做一些测试板,参考图十,对比电容有无隔层参考,以及隔层参考时不同GND cutout尺寸时的仿真与测试阻抗的对比,如此反复几次,就可以得到一个比较精确的电容模型,后面所有的电容仿真,你可以直接调用此模型。

图十一和十二是仿真和实测电容阻抗的对比值,当两者差异较小时,此时对应的电容模型,即可作为你的基础仿真模型之一,随用随调。

以上就是今天分享的AC耦合电容仿真的一些细节,当速率高于25Gbps及以上时,应尽量避免使用边界条件电容模型,要用自己校准过的金属block电容模型,当然电容还有其他细节要注意的比如:回流孔的位置摆放、电容位置摆放是靠近发射芯片好还是靠近接收芯片好、以及电容位置摆放对串扰的影响等,这些就留着以后有机会再讲。

参考资料:

“Embedded DC Blocking Capacitors in Connectors - Study of Impacts on PCB Design and High Speed Serial Link Performance”

作者:萧隐君,仿真秀专栏作者

声明:原创文章,首发仿真秀公众号(ID:fangzhenxiu2018),部分图片源自网络,如有不当请联系我们,欢迎分享,禁止私自转载,转载请联系我们。