🏆本文收录于「Bug调优」专栏,主要记录项目实战过程中的Bug之前因后果及提供真实有效的解决方案,希望能够助你一臂之力,帮你早日登顶实现财富自由🚀;同时,欢迎大家关注&&收藏&&订阅!持续更新中,up!up!up!!

问题描述

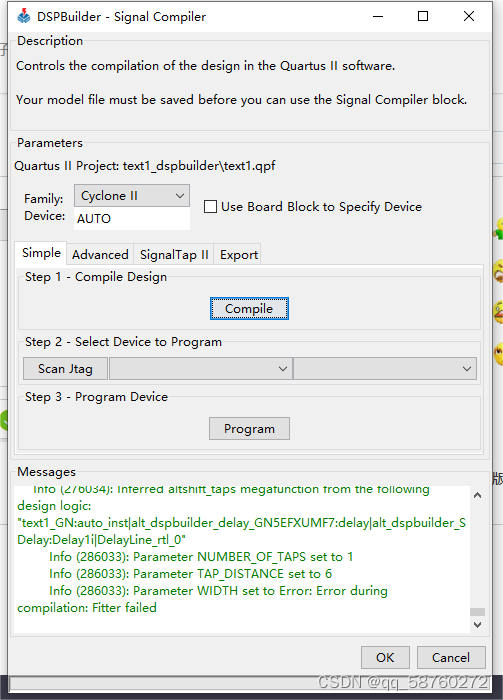

dspbuilder中使用signalcompiler时报错Error during compilation: Fitter failed,求解决办法

双击signalcompiler后就报错,刚开始以为是没破解好的原因,后面照着别的教程做了之后还是这样的报错,不知道是哪里出了问题,求怎么解决,不胜感激!

我的软件版本是quartusii13.0,dspbuilder13.0,matlabr2010b。

如上问题有来自我自身项目开发,有的收集网站,有的来自读者,如有侵权,立马删除。

解决方案

如下是上述问题的解决方案,仅供参考:

"Fitter failed"错误通常表明在DSP Builder中进行HDL代码生成时,Quartus II软件无法完成适配(fitting)过程。这可能是由多种原因引起的,以下是一些可能的解决方案:

-

资源限制:检查您的设计是否超出了FPGA的资源限制,如逻辑单元(LEs)、寄存器(registers)或块RAM(BRAM)。如果设计过于复杂,尝试简化设计或使用更高性能的FPGA。

-

时序问题:时序约束可能没有被正确满足。检查您的时钟定义和时序约束,确保所有的时钟频率和时序要求都在FPGA的规格范围内。

-

错误的代码或设置:检查DSP Builder生成的MATLAB代码和Simulink模型是否有错误。同时,检查DSP Builder项目的设置,确保所有的参数和选项都正确配置。

-

软件版本兼容性:确保您使用的Quartus II、DSP Builder和MATLAB版本相互兼容。有时候,软件版本不匹配可能会导致适配失败。

-

许可问题:尽管您提到不是破解问题,但确保您的软件许可有效也是很重要的。无效的许可也可能导致适配失败。

-

清理项目:尝试清理项目(使用Quartus II的“File”->“Cleanup”功能),然后重新生成HDL代码。

-

查看日志文件:检查DSP Builder和Quartus II的日志文件,这些文件通常包含了详细的错误信息,可以帮助您定位问题。

-

更新软件:如果您使用的是较旧的软件版本,尝试更新到最新的版本。

-

重新安装软件:如果上述方法都无法解决问题,您可能需要卸载并重新安装Quartus II、DSP Builder和MATLAB。

-

寻求支持:如果问题依然无法解决,您可以联系Altera(现为Intel PSG)的技术支持或在相关的技术论坛上寻求帮助。

请注意,DSP Builder已经很多年没有更新,而且已经被Intel的 newer design suite取代。如果您的项目允许,考虑迁移到更新的工具链可能会更有益。

希望能够帮到有需要的你。

PS:如若遇到采纳如下方案还是未解决的同学,希望不要抱怨&&急躁,毕竟影响因素众多,我写出来也是希望能够尽最大努力帮助到同类似问题的小伙伴,即把你未解决或者产生新Bug黏贴在评论区,我们大家一起来努力,一起帮你看看,可以不咯。

若有对当前Bug有与如下提供的方法不一致,有个不情之请,希望你能把你的新思路或新方法分享到评论区,一起学习,目的就是帮助更多所需要的同学,正所谓「赠人玫瑰,手留余香」。

☀️写在最后

ok,以上就是我这期的Bug修复内容啦,如果还想查找更多解决方案,你可以看看我专门收集Bug及提供解决方案的专栏「Bug调优」,都是实战中碰到的Bug,希望对你有所帮助。到此,咱们下期拜拜。

码字不易,如果这篇文章对你有所帮助,帮忙给bugj菌来个一键三连(关注、点赞、收藏) ,您的支持就是我坚持写作分享知识点传播技术的最大动力。

同时也推荐大家关注我的硬核公众号:「猿圈奇妙屋」 ;以第一手学习bug菌的首发干货,不仅能学习更多技术硬货,还可白嫖最新BAT大厂面试真题、4000G Pdf技术书籍、万份简历/PPT模板、技术文章Markdown文档等海量资料,你想要的我都有!

📣关于我

我是bug菌,CSDN | 掘金 | InfoQ | 51CTO | 华为云 | 阿里云 | 腾讯云 等社区博客专家,C站博客之星Top30,华为云2023年度十佳博主,掘金多年度人气作者Top40,51CTO年度博主Top12,掘金/InfoQ/51CTO等社区优质创作者;全网粉丝合计 20w+;硬核微信公众号「猿圈奇妙屋」,欢迎你的加入!免费白嫖最新BAT互联网公司面试真题、4000G PDF电子书籍、简历模板等海量资料,你想要的我都有,关键是你不来拿。

)

)

)