1.简介

本节主要讲解如何基于ZYNQ7020搭建一个视频流接收以及显示的数据通路。为后续的算法图像验证提供基础。

2.项目框架

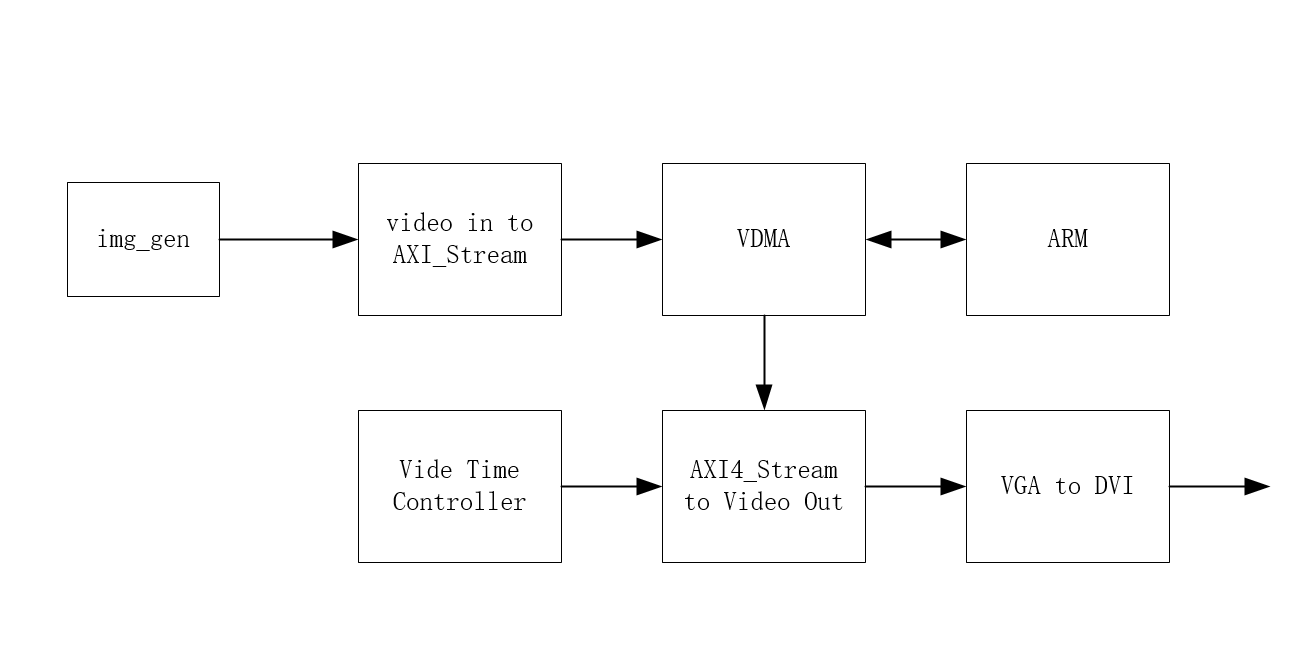

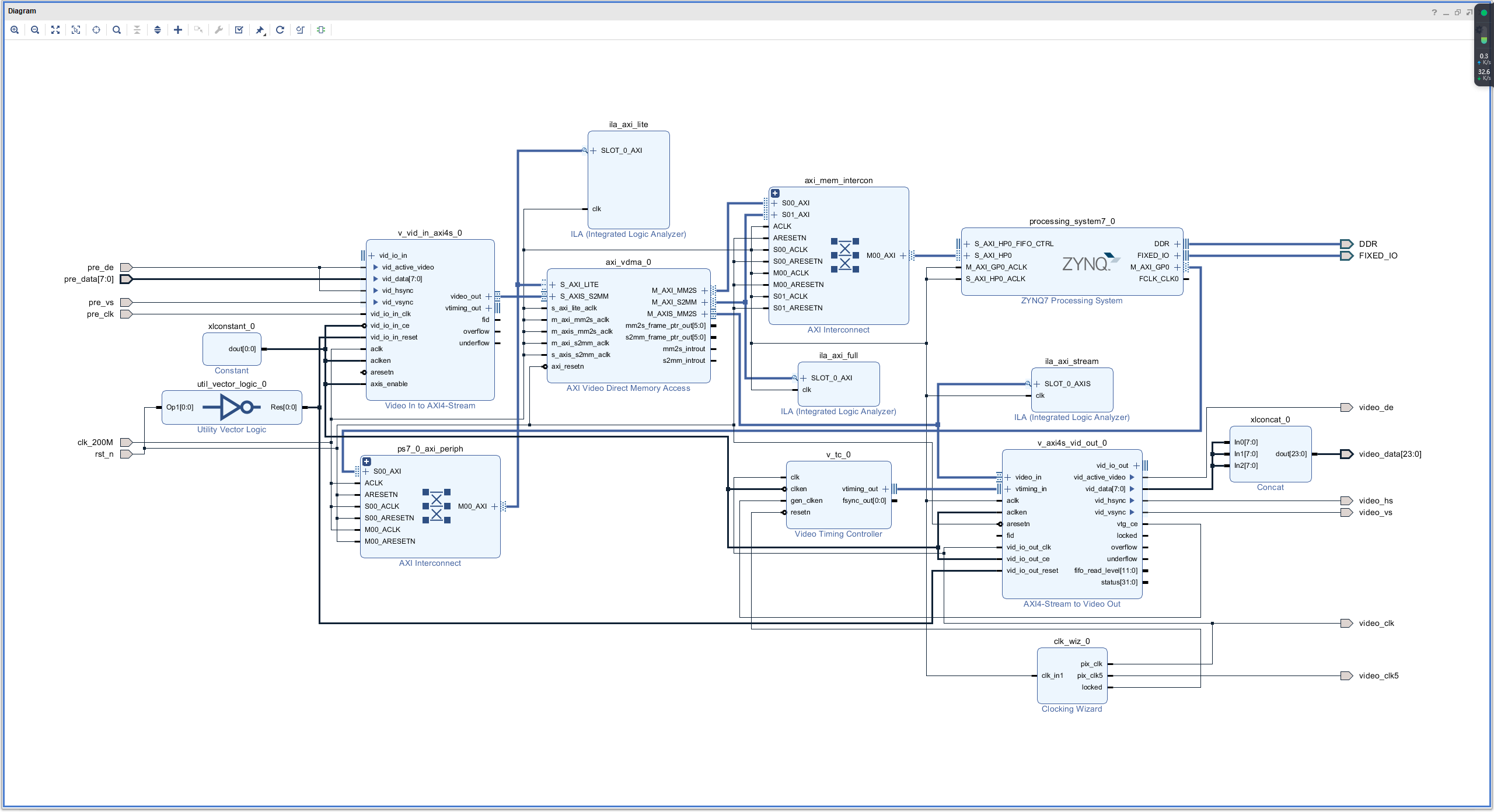

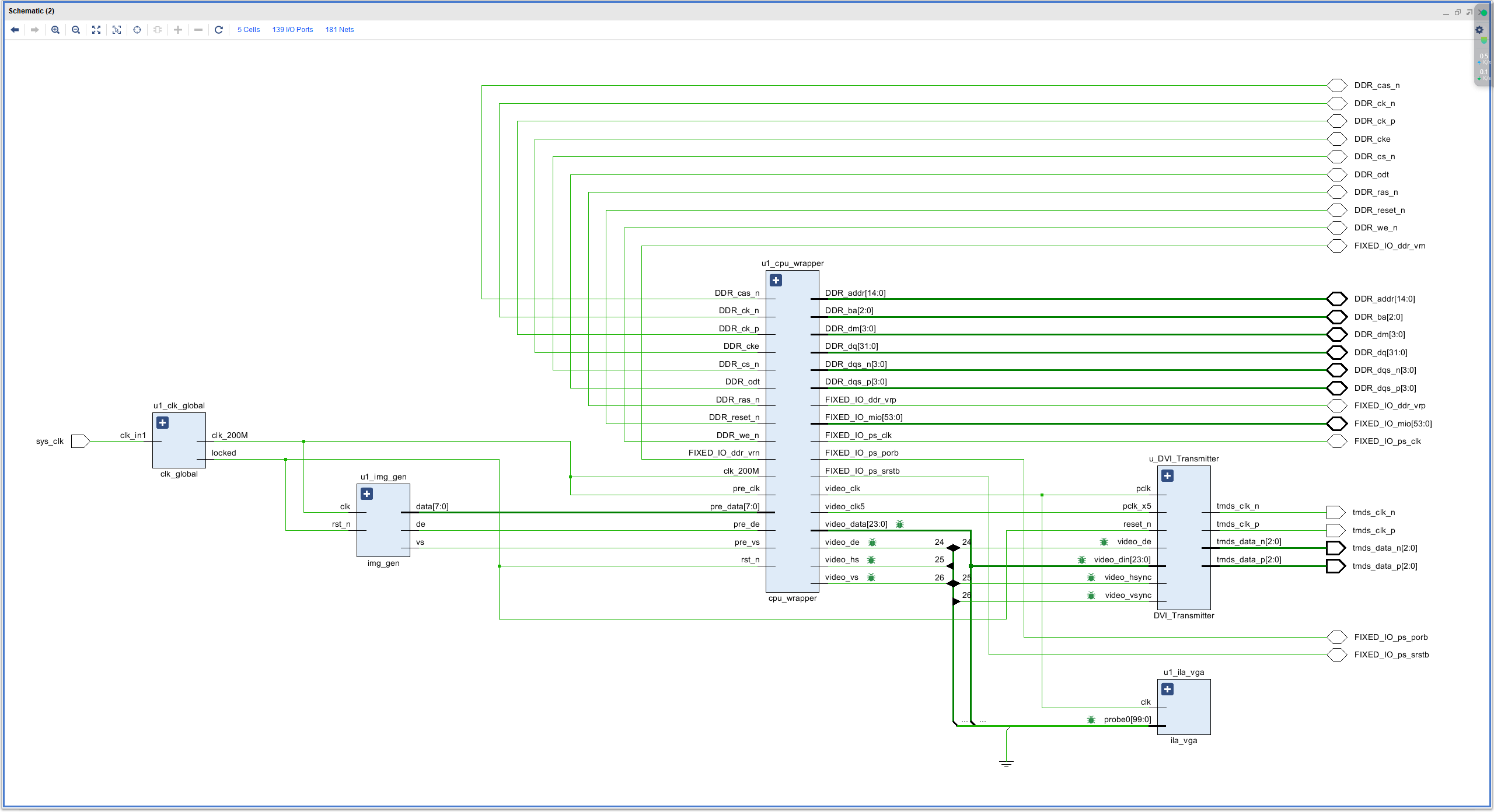

整个项目简略框架如图,img_gen负责产生图像像素点,给到video in to AXI_Stream模块后转化为AXI_Stream数据流给到VDMA,VDMA采用三帧缓存的方式向ARM控制的DDR3写入像数据据并读出像素数据,读出的数据给到AXI4_Stream to Video Out模块,AXI4_Stream to Video Out同时接收Vide Time Controller模块产生的VGA时序,并将VGA时序与像素点信息全部给到VGA to DVI模块,然后交由HDMI显示屏显示。项目完成后的详细信息如下:

3.现象

本次的图像为1080P,考虑到资源问题,本次的像素信息实时生成,最终上板测试的图像为黑白渐变条纹。上板验证无误。

)

)

)

![[C++ 从入门到精通] 20.对象移动、移动构造函数、移动赋值运算符](http://pic.xiahunao.cn/[C++ 从入门到精通] 20.对象移动、移动构造函数、移动赋值运算符)

Diffusion原理 pytorch代码实例)

——unordered_set,unordered_map学习使用)

)