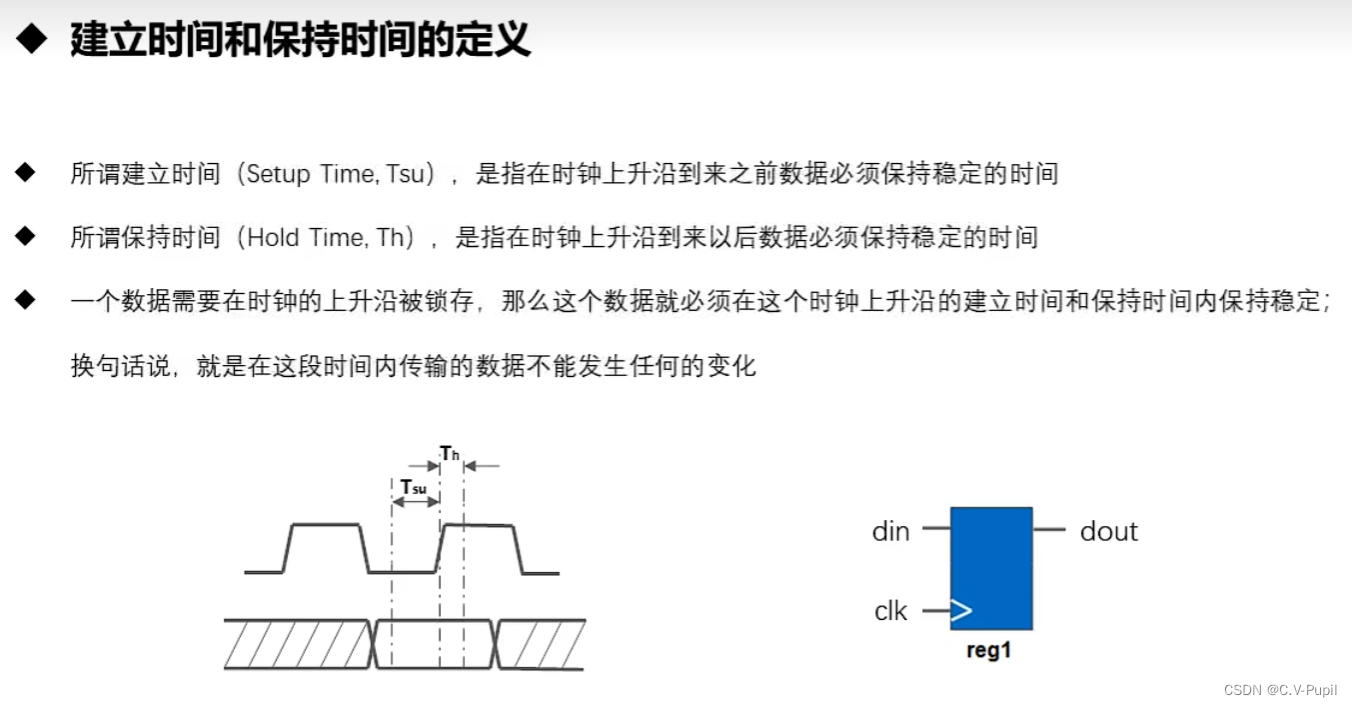

FPGA时序约束与分析--建立时间与保持时间

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.mzph.cn/news/719754.shtml

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

搜索回溯算法(DFS)1------递归

目录

简介:

递归问题解题的思路模板

例题1:汉诺塔

例题2:合并两个有序链表

例题3:反转链表

例题4:两两交换链表中的节点

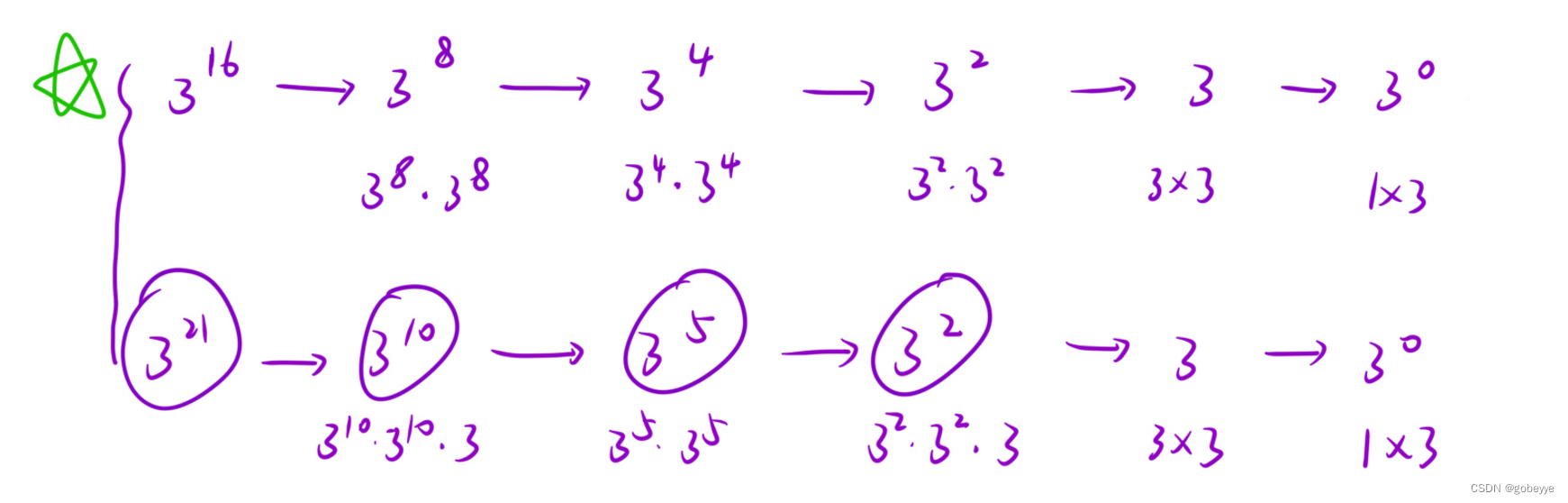

例题5:Pow(x,n)-快速幂

结语: 简介&…

嵌入式驱动学习第二周——断言机制

前言 这篇博客来聊一聊C/C的断言机制。 嵌入式驱动学习专栏将详细记录博主学习驱动的详细过程,未来预计四个月将高强度更新本专栏,喜欢的可以关注本博主并订阅本专栏,一起讨论一起学习。现在关注就是老粉啦! 目录 前言1. 断言介绍…

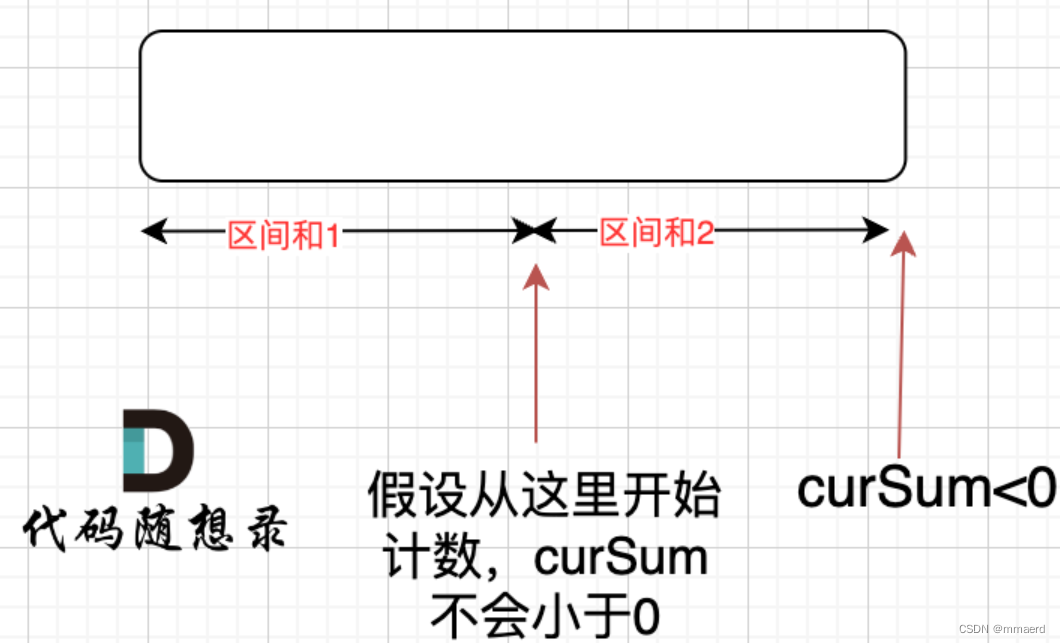

贪心 Leetcode 134 加油站

加油站

Leetcode 134

学习记录自代码随想录

在一条环路上有 n 个加油站,其中第 i 个加油站有汽油 gas[i] 升 你有一辆油箱容量无限的的汽车,从第 i 个加油站开往第 i1 个加油站需要消耗汽油 cost[i] 升。你从其中的一个加油站出发,开始时油…

steam游戏搬砖,跨国信息差项目,每天1小时收益也很不错

大家好,我是阿阳!每天都是一个新的开始!

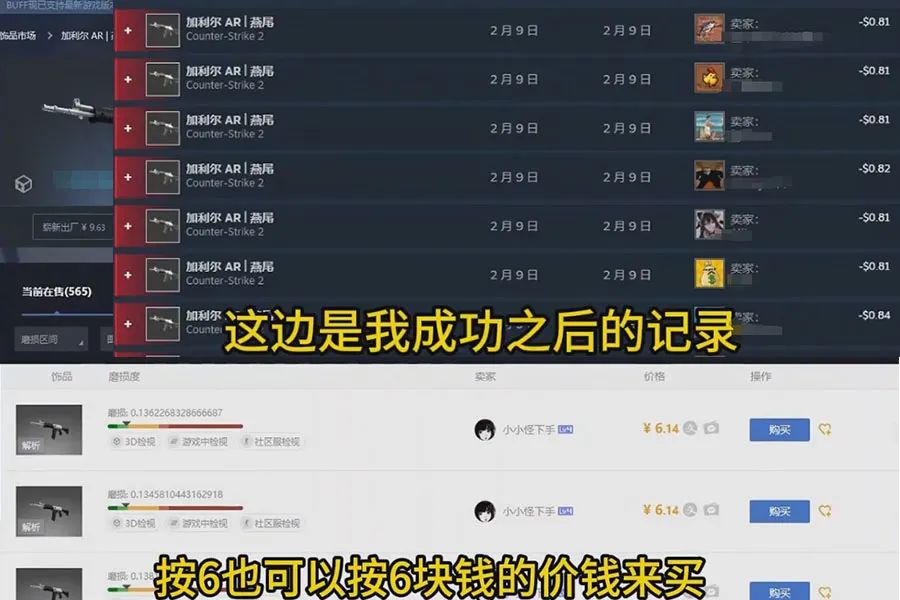

今天看到个Steam游戏搬砖项目,还是跨国国际贸易,感觉很好玩,特来给大家分享。 原理简介

就是把Steam上的游戏装备,搬运到国内网易Buff平台上来卖。目前…

算法沉淀——动态规划之01背包问题(leetcode真题剖析)

算法沉淀——动态规划之01背包问题 01.【模板】01背包02.分割等和子集03.目标和04.最后一块石头的重量 II 01背包问题是一类经典的动态规划问题,通常描述为:有一个固定容量的背包,以及一组物品,每件物品都有重量和价值,…

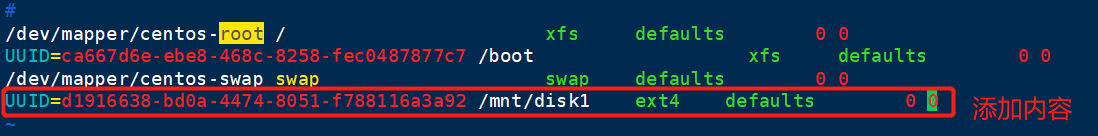

云计算 2月28号 (linux的磁盘分区)

一 存储管理

主要知识点: 基本分区、逻辑卷LVM、EXT3/4/XFS文件系统、RAID

初识硬盘 机械 HDD

固态 SSD SSD的优势 SSD采用电子存储介质进行数据存储和读取的一种技术,拥有极高的存储性能,被认为是存储技术发展的未来新星。 与传统硬盘相比,…

深度伪造,让网络钓鱼更加难以辨别

网络钓鱼一直是安全领域的一个突出话题,尽管这类诈骗形式已经存在了几十年,依旧是欺诈攻击或渗透组织的最有效方法之一。诈骗分子基于社会工程原理,通过邮件、网站以及电话、短信和社交媒体,利用人性(如冲动、不满、好…

嵌入式驱动学习第二周——Linux内核打印

前言 这篇博客来聊一聊Linux内核打印。 嵌入式驱动学习专栏将详细记录博主学习驱动的详细过程,未来预计四个月将高强度更新本专栏,喜欢的可以关注本博主并订阅本专栏,一起讨论一起学习。现在关注就是老粉啦! 目录 前言1. dmesg指令…

【LeetCode:225. 用队列实现栈 + 栈 | 队列】

🚀 算法题 🚀 🌲 算法刷题专栏 | 面试必备算法 | 面试高频算法 🍀 🌲 越难的东西,越要努力坚持,因为它具有很高的价值,算法就是这样✨ 🌲 作者简介:硕风和炜,…

水牛社软件是真的吗?

软件是真的,不过毕竟是为了赚钱或者获取资源而买的,所以大部分只关心能赚多少钱吧

说实话,我用了2年了,一些独立的项目还有群,有一月挣几千上万的,有一月赚几百的

软件是一个集合体,不是像很多…

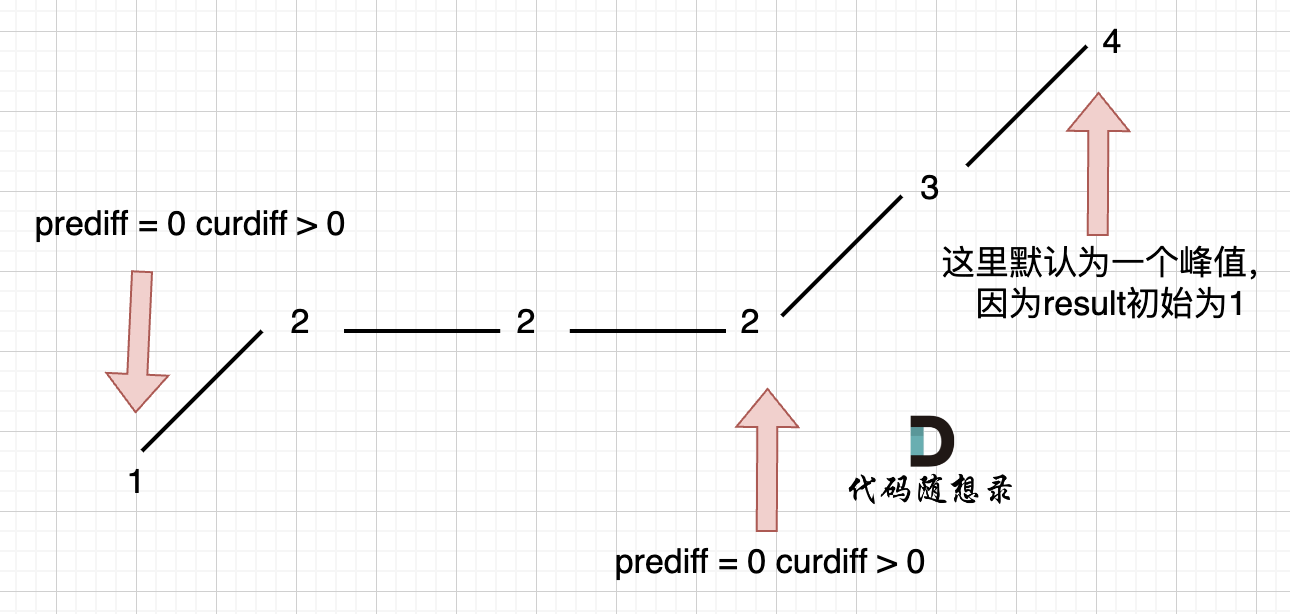

代码随想录第二十七天 455.分发饼干 376.摆动序列 53.最大子序和 122.买卖股票的最佳时机II

LeetCode 455 分发饼干

题目描述

假设你是一位很棒的家长,想要给你的孩子们一些小饼干。但是,每个孩子最多只能给一块饼干。

对每个孩子 i,都有一个胃口值 g[i],这是能让孩子们满足胃口的饼干的最小尺寸;并且每块饼…

2024全国护网行动HW行动招聘/收人!!!

2024全国护网行动HW行动招聘 溯蓉信创开始收人啦!!!现在开始收录2024HW简历,感兴趣的小伙伴扫码二维码添加微信

我们签约后,入场即预付款3k,签约后我们会在HW之前对我们的人员进行HW培训,保证上…

Three.js--》探寻Cannon.js构建震撼的3D物理交互体验(一)

我们用three.js可以绘制出各种酷炫的画面,但是当我们想要一个更加真实的物理效果的话,这个时候我们就需要一个物理的库,接下来我们就讲解一下今天要学习的canon,它可以给我们提供一个更加真实的物理效果,像物体的张力、…

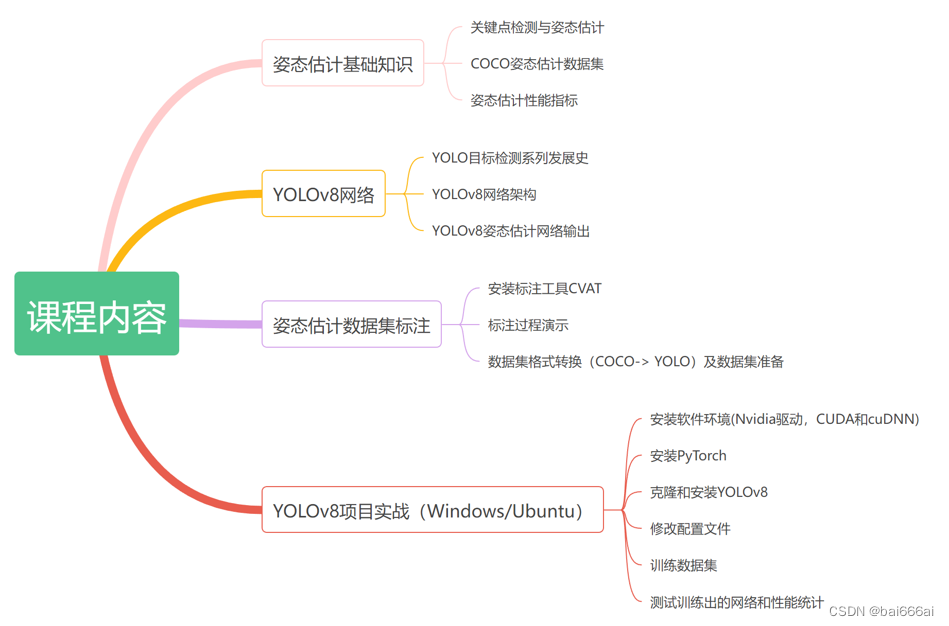

YOLOv8姿态估计实战:训练自己的数据集

课程链接:https://edu.csdn.net/course/detail/39355 YOLOv8 基于先前 YOLO 版本的成功,引入了新功能和改进,进一步提升性能和灵活性。YOLOv8 同时支持目标检测和姿态估计任务。 本课程以熊猫姿态估计为例,将手把手地教大家使用C…

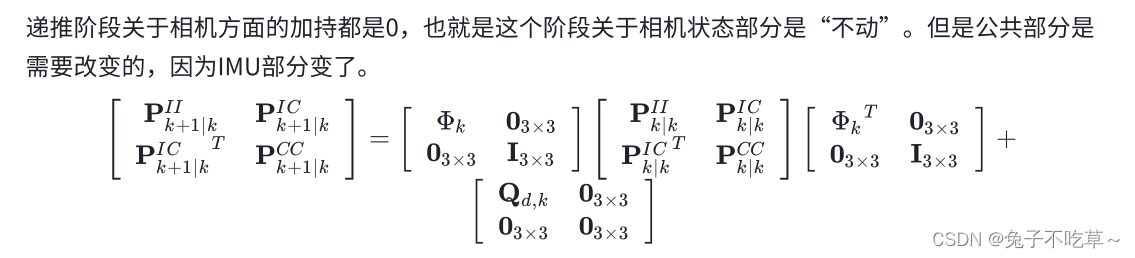

MSCKF5讲:后端代码分析

MSCKF5讲:后端代码分析 文章目录 MSCKF5讲:后端代码分析1 初始化initialize()1.1 加载参数1.2 初始化IMU连续噪声协方差矩阵1.3 卡方检验1.4 接收与订阅话题createRosIO() 2 IMU静止初始化3 重置resetCallback()4 featureCallback4.1 IMU初始化判断4.2 I…

【文末送书】智能计算:原理与实践

欢迎关注博主 Mindtechnist 或加入【智能科技社区】一起学习和分享Linux、C、C、Python、Matlab,机器人运动控制、多机器人协作,智能优化算法,滤波估计、多传感器信息融合,机器学习,人工智能等相关领域的知识和技术。关…

基于YOLOv8/YOLOv7/YOLOv6/YOLOv5的停车位检测系统(Python+PySide6界面+训练代码)

摘要:开发停车位检测系统对于优化停车资源管理和提升用户体验至关重要。本篇博客详细介绍了如何利用深度学习构建一个停车位检测系统,并提供了完整的实现代码。该系统基于强大的YOLOv8算法,并结合了YOLOv7、YOLOv6、YOLOv5的性能对比…

HarmonyOS端云体化开发—创建端云一体化开发工程

云开发工程模板

DevEco Studio目前提供了两种云开发工程模板:通用云开发模板和商城模板。您可根据工程向导轻松创建端云一体化开发工程,并自动生成对应的代码和资源模板。在创建端云一体化开发工程前,请提前了解云开发工程模板的相关信息。 …