AGM CPLD (AGRV2K )的时钟(外部时钟和片上内部振荡器)

外部晶振 与 内部振荡器:

mcu 和 cpld 联合编程时, 整颗芯片需要一颗外部晶振。

(芯片有内部振荡器, 但误差较大, 校准后 5%以内误差, 参后续介绍)

1、使用外部晶振

该晶振是 MCU和 CPLD 共用的, (没必要为 CPLD 再单独提供一颗晶振) 。晶振可以是有源的, 也可以是无源的。

【注: 这里的外部晶振配置, 跟单纯使用 MCU 是一样的】

如果是无源晶体, 频率限制在 4M~16M。 要接到芯片的 OSC_IN/OUT 引脚。 然后VE 中直接定义主频多少 M 即可。 如

如果是有源晶体, 频率无限制。 根据接入点分为两种情况:

1) 如果接入到 OSC_IN 引脚:

ve 里定义同上(配置 HSECLK 项) 。

同时, 需要在 platformio.ini 里, 增加配置宏: BOARD_HSE_BYPASS=SYS_HSE_NONE,如图:

2) 如果接入到别的 IO 引脚(如 PIN_2) :

同 1)中, platformio.ini 里也同样增加配置宏;

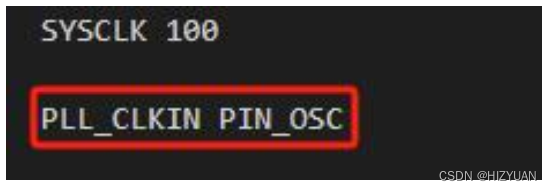

然后在 VE 配置中, 除了配置 HSECLK 项 外, 还需要配置 PLL_CLKIN 项, 如图:

配置完后, 需要重新下载 logic, 重新下载 code。

2、使用内部振荡器:

校准后精度大约在 5%以内, 想省成本且对时钟要求不高的话可以使用。如对精度有要求,海振远建议预留外部晶振接口,方便自由选择。

使用方式:

在 VE 里增加: “PLL_CLKIN PIN_OSC”, 如下图:

只修改以上配置, 不用配置 HSECLK 项, 代码中也不需修改。

注: 自动校准目前有以下使用限制:

a) 逻辑部分要压缩, platformio.ini 中配置 board_logic.compress = true

b) 校准动作是在烧录时进行的。

烧录时, 需要使用 swd 方式且通过我们的软件烧录, uart 不支持。(即: 出厂烧录不支持 uart 方式)

目前测试过 jlink 和 dap 校准结果都还不错, 但是也出现过一个客户使用其他烧录器校准结果差很多。

(对一个全新的或是 wipe 过后的芯片烧录会看到校准信息)。

AGM AG32系列MCU,不仅仅是高性能MCU,还在片上集成了2KLE FPGA逻辑资源,非常适合工业控制、医疗及消费市场。芯片技术支持与芯片订购,可联系海振远科技提供支持。

)

)

)

)

)