4.2.1 静态读写存贮器( SRAM )

1.概述

静态读写存贮器(SRAM)使用十分方便,在微型计算机领域获得了极其广泛的应用。现以一块典型的SRAM芯片为例说明其外部特性及工作过程。

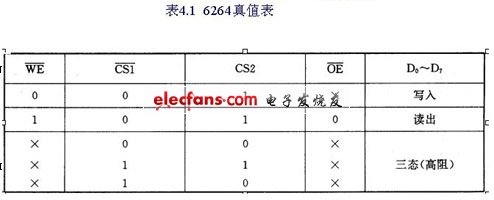

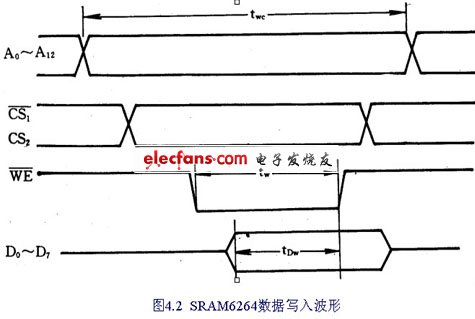

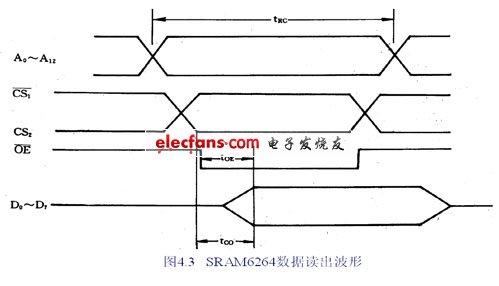

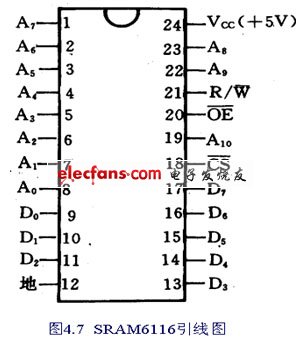

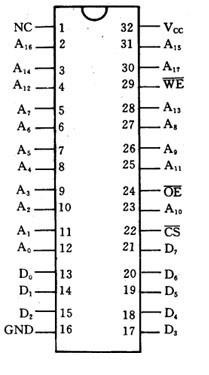

(1) 8K×8bit的CMOSRAM芯片 ① 引线功能。6264(6164)有28条引出线,它们包括:A0~A12为13条地址信号线。D0~D7为8条双向数据线。CS2为两条选片信号的引线。

NC为没有使用的空脚。芯片上还有+5V电压和接地线。 ② 6264(6164)的工作过程。

2. 连接使用

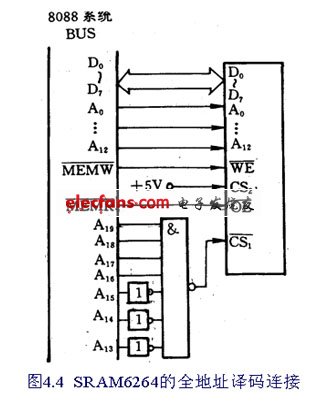

(1) 全地址译码方式

从图4.4可以看到,6264这一8KB的芯片唯一地占据从F0000H到F1FFFH这8KB内存空间;芯片的每一个存贮单元唯一地占据上述地址空间中的一个地址。

该图用在CPU最大模式下。

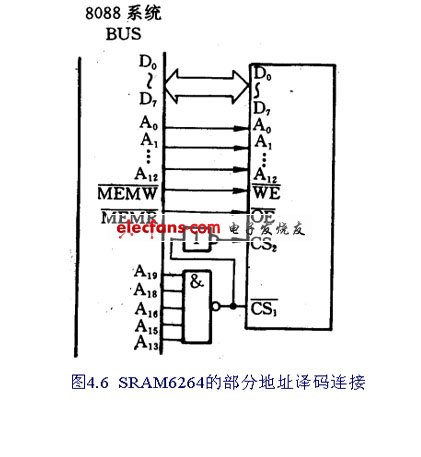

(2)部分地址译码方式

首先,让我们看一下图4.6所示的6264的连接图。

分析图4.6所示的连接图,可以发现,此时的8KB芯片6264所占据的内存地址空间为

DA000H~DBFFFH

DE000H~DFFFFH

FA000H~FBFFFH

FF000H~FFFFFH

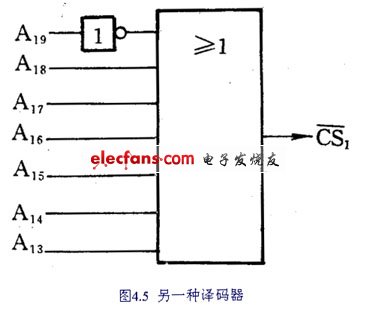

(3) 译码器电路

在工程上常用的译码电路还有如下几种类型:

①利用厂家提供的现成的译码器芯片。

②利用厂家提供的数字比较器芯片。

③利用ROM做译码器。

④利用PLD。

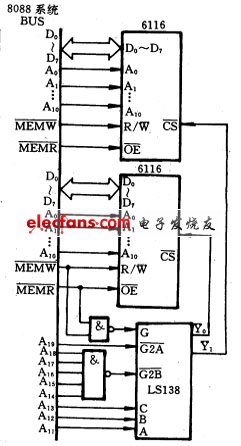

3. 静态RAM连接举例

图4.8中,使用一块3-8译码器芯片(74LS138或8205),将两片6116所占的内存地址范围安排在7C000H~7CFFFH。

4.等待的实现

在存贮器芯片的连接使用中,由于采用了要求的定时时间比较长的芯片或由于总线的时间延迟过大等原因,CPU提供的定时时间不能满足存贮器芯片的要求,

使CPU无法正确地读写存贮器。这就要求电路的设计者采取适当的措施来解决。

IT技术分享社区个人文章汇总(编程技术篇))

....)

入门教程)

.doc)

)

)