好文:

【精选】摄像头的MIPI接口、DVP接口和CSI接口-CSDN博客【精选】摄像头的MIPI接口、DVP接口和CSI接口-CSDN博客

(56 封私信 / 24 条消息) 显示器的 VGA、HDMI、DVI 和 DisplayPort 接口有什么区别? - 知乎 (zhihu.com)

嵌入式工程师必备:MIPI CSI-2 接口协议_mipi csi2有多少pin-CSDN博客

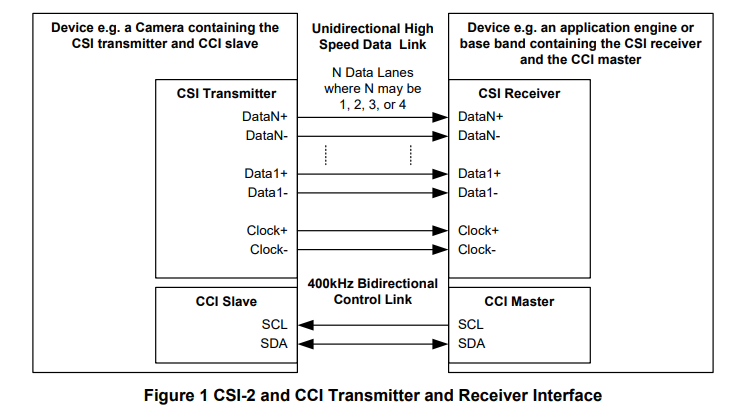

CSI-2 规范定义了发送器和接收器之间的标准数据传输和控制接口。

数据传输接口(简称CSI-2)是单向差分串行接口,具有476个数据和时钟信号;

该接口的物理层是 MIPI Alliance Specification for D-PHY [MIPI01]。

图 1 显示了 CSI-2 发送器和接收器之间的连接,通常是 摄像头模块和接收器模块(移动电话引擎的一部分)。

控制接口(简称CCI)是兼容I2C标准的双向控制接口

DVP和MIPI CSI

DVP是并口,需要PCLK、VSYNC、HSYNC、D[0:11]——可以是8/10/12bit数据,具体情况要看ISP或baseband是否支持;MIPI是LVDS低压差分串口,只需要要CLKP/N、DATAP/N——最大支持4-lane,一般2-lane可以搞定。MIPI接口比DVP的接口信号线少,由于是低压差分信号,产生的干扰小,抗干扰能力也强。最重要的是DVP接口在信号完整性方面受限制,速率也受限制。500W还可以勉强用DVP,800W及以上都采用MIPI接口。

该图定义了 CSI-2 中使用的概念层结构。这些层的特征如下:

CSI协议层设计:

应用层:

主要设计了上层数据流的编码以及解码格式,规定了像素转换为字节的映射关系;

协议层:

主要包括了像素/字节打包/字节解包层,

LLP层提供了串行传输数据的同步机制,

通道管理层提供了数据位宽可扩展功能,从而灵活的适应不同的应用场景;

物理层:

定义了基本传输介质规范,确定了CSI-2协议物理层的输入输出特性参数,并确定其电气特性以及时钟时序。

PHY:物理层。

PHY 层指定传输介质(电导体)、输入/输出电路以及从串行比特流捕获“1”和“0”的时钟机制。规范的这一部分记录了传输介质的特性、信令的电气参数以及时钟和数据通道之间的定时关系。

指定了发送传输开始 (SoT) 和传输结束 (EoT) 信号的机制以及可以在发送和接收 PHY 之间传送的其他“带外”信息。位级和字节级同步机制包含在 PHY 中。

Protocol Layer:协议层。

协议层由多个层组成,每个层都有不同的职责。 CSI-2 协议使用主机处理器上的单个接口支持多个数据流。协议层指定如何标记和交织多个数据流,以便可以正确地重建每个数据流。

Pixel/Byte Packing/Unpacking Layer: 像素/字节打包/解包层。

CSI-2 支持具有从每像素六位到二十四位的不同像素格式的图像应用。在发送器中,该层将来自应用层的像素打包为字节,然后将数据发送到低级协议层。

在接收器中,该层将来自低级协议层的字节解包为像素,然后将数据发送到应用程序层。每像素八位数据在该层中传输不变。

Low Level Protocol:低级协议层

低级协议 (LLP) 包括为 SoT(传输开始)和 EoT(传输结束)事件之间传输的串行数据建立位级和字节级同步以及向下一层传输数据的方法。

LLP的最小数据粒度是1字节。 LLP 还包括字节内位值解释的分配,即“Endian”分配。

封装数据成为MIPI帧的结构。

Lane Management.:

CSI-2 可进行通道扩展以提高性能。数据通道的数量可以是 1、2、3 或 4,具体取决于应用的带宽要求。

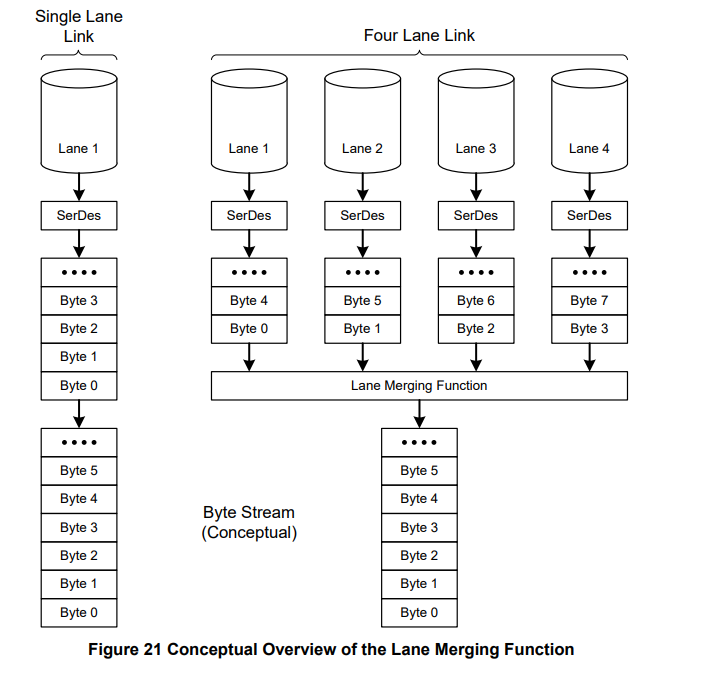

接口的发送侧将输出数据流分发(“分发器”功能)到一个或多个通道。在接收侧,接口从通道收集字节并将它们合并(“合并”功能)在一起形成重新组合的数据流,其恢复原始流序列。

协议层小结

协议层内的数据被组织为数据包。接口的发送端将标头和可选的错误检查信息附加到要在低级协议层发送的数据上。在接收端,标头在低级协议层被剥离,并由接收器中的相应逻辑进行解释。错误检查信息可用于测试传入数据的完整性。

应用层

该层描述了数据流中包含的数据的高级编码和解释。 CSI-2 规范描述了像素值到字节的映射。

规范的规范部分仅涉及链接的外部部分,例如通过链路传输的数据和位模式。所有内部接口和层都是纯粹的信息性的。

LLP编码:

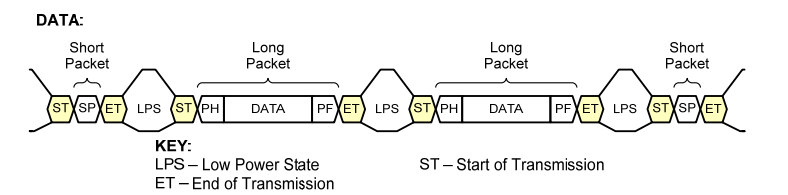

低级协议 (LLP) 是一种面向字节、基于数据包的协议,支持使用短数据包和长数据包格式传输任意数据。为简单起见,本节中的所有示例都是单通道配置。

低级协议特性:

• 传输任意数据(与有效负载无关)

• 8 位字长

• 在同一链路上支持最多四个交错虚拟通道

• 用于帧起始、帧结束、行起始和帧起始的特殊数据包行结束信息

·用于应用特定有效负载数据的类型、像素深度和格式的描述符821

·用于错误检测的16位校验和代码。

低级协议分组格式

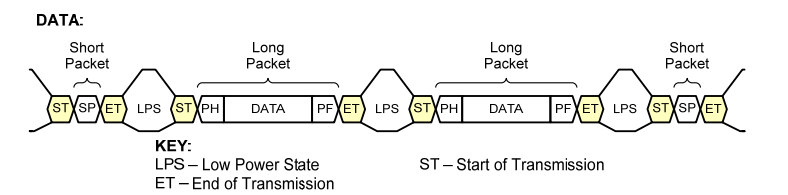

为低级协议通信定义了两种分组结构:长分组和短分组。

对于每个数据包结构,从低功耗状态退出后跟随的传输开始 (SoT) 序列指示数据包的开始。传输结束 (EoT) 序列后跟低功耗状态表示数据包结束

低级协议长数据包格式

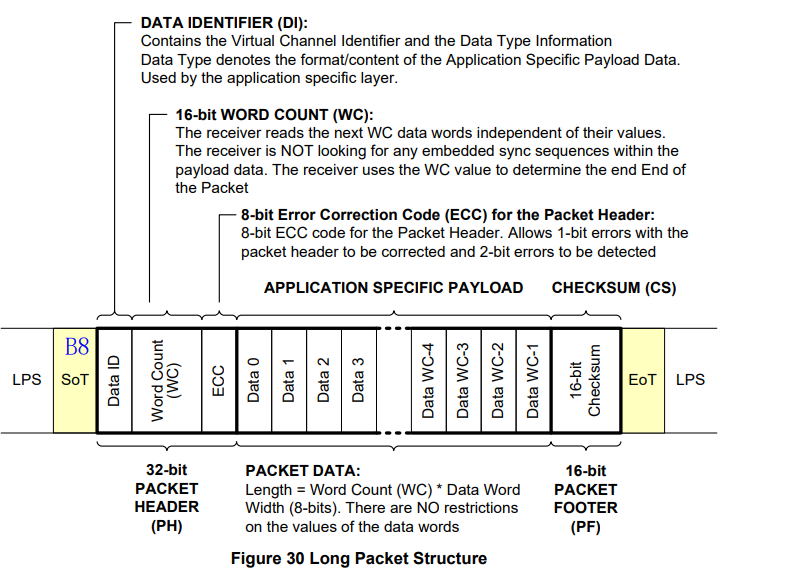

图 30 显示了低级协议长数据包的结构。

长数据包应由数据类型 0x10 至 0x37 标识。有关数据类型的说明,请参阅表 3。

长数据包应由三个元素组成:

32 位数据包标头 (PH)、具有可变数量的 8 位数据字的应用程序特定数据有效负载以及 16 位数据包页脚 (PF)。

包头进一步由三个元素组成:8位数据标识符、16位字计数字段和8位ECC。数据包页脚有一个元素,即 16 位校验和(CHECKSUM)。

有关数据包元素的进一步描述,请参阅第 9.2 节到第 9.5 节。

SOT:Start of trans

8位数据标识符(DI:VC & DT):

包含虚拟通道标识符和数据类型信息。

数据类型表示应用特定有效负载数据的格式/内容。由应用程序特定层使用。

16 位字计数 (WC):

接收器读取下一个 WC 数据字,与其值无关。

Packet Data的数据长度

接收器不会在有效负载数据中寻找任何嵌入的同步序列。

接收方使用WC值来确定数据包的结束End

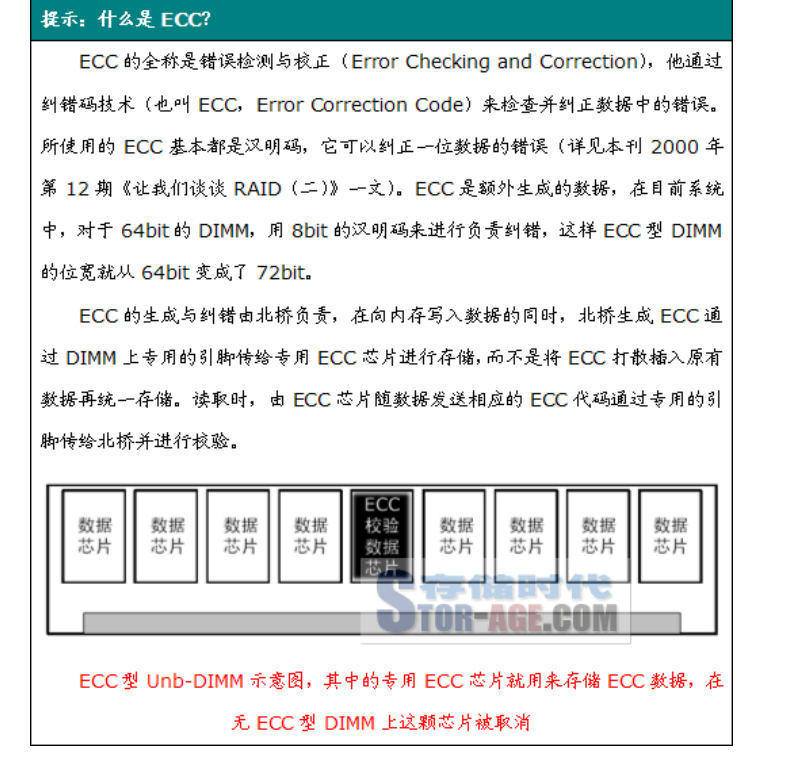

数据包标头的 8 位纠错码 (ECC):

数据包标头的 8 位 ECC 代码。

允许纠正数据包标头的 1 位错误并检测 2 位错误

数据包数据:特定于应用的有效负载

长度 = 字数 (WC) * 数据字宽度(8 位)。数据字的值没有限制

16 位校验和(CHECKSUM)

校验图像数据的错误

EOT:End of trans

Data ID:数据标识符定义数据的虚拟通道和应用特定有效负载数据的数据类型。

WC:字数定义了数据有效负载中数据包报头末尾和数据包页脚开头之间的8位数据字的数量。

字数统计中不包括包头和包尾。

纠错码(ECC):字节允许纠正单比特错误,并在数据包标头中检测2比特错误。这包括数据标识符值和字计数值。

包头结束后,接收器读取数据有效负载的下一个字数*8位数据字。

在读取数据有效负载时,接收器不应查找任何嵌入的同步代码。

因此,数据字的值没有限制。

一旦接收器读取了数据有效负载,它就会读取数据包页脚中的校验和。

在一般情况下,数据有效负载的长度应为 8 位数据字的倍数。

另外,每种数据格式可以对有效负载数据的长度施加附加限制,例如四字节的倍数。

每个字节应首先传输最低有效位。

有效负载数据可以以仅受数据格式要求限制的任何字节顺序来传输。

多字节元素(例如字计数、校验和和 短数据包 16 位数据字段)应首先传输最低有效字节。

在 EoT 序列之后,接收器开始寻找下一个 SoT 序列。

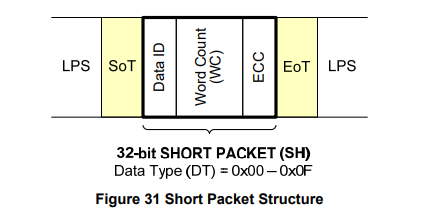

低级协议短数据包格式

图 31 显示了低级协议短数据包的结构。

短数据包应由数据类型 0x00 至 0x0F 标识。

有关数据类型的说明,请参阅表 3。

短数据包应仅包含数据包标头;不得出现数据包页脚。

包头中的字数字段应被短包数据字段替换。

对于帧同步数据类型,短包数据字段应为帧号。

对于线路同步数据类型,短包数据字段应为线路号。

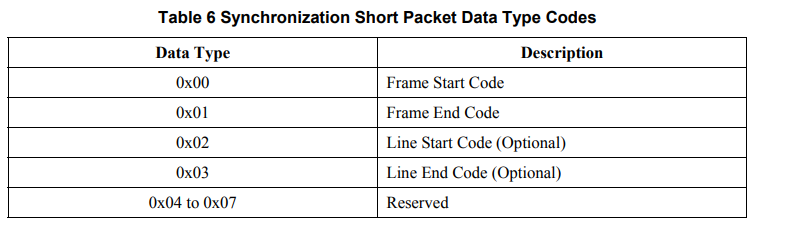

有关帧和行同步数据类型的说明,请参阅表 6。

对于通用短包数据类型,短包数据字段的内容应由用户定义。

纠错码 (ECC) 字节允许纠正单比特错误并检测短数据包中的 2 位错误。

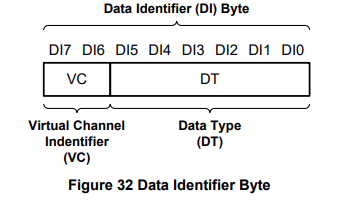

数据标识符 (DI)

数据标识符字节包含虚拟通道标识符 (VC) 值和数据类型 (DT) 值,如图 32 所示。虚拟通道标识符包含在数据标识符字节的两个 MS 位中。数据类型值包含在数据标识符字节的六个 LS 位中

虚拟信道标识符:Virtual Channel Identifier

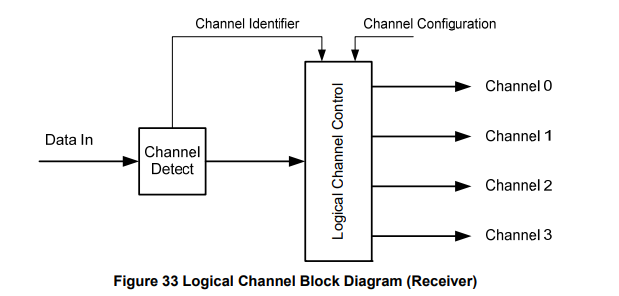

虚拟通道标识符的目的是为数据流中交错的不同数据流提供单独的通道。虚拟通道标识符号位于数据标识符字节的前两位中。接收器将监视虚拟通道标识符并将交错的视频流解复用到其适当的通道。最多支持四个数据流;有效通道标识符为 0 到 3。外设中的虚拟通道标识符应该是可编程的,以允许主机处理器控制数据流的解复用方式。逻辑通道的原理如图 33 所示。

图 34 说明了利用虚拟通道支持的数据流的示例。

数据类型(DT)

数据类型值指定有效负载数据的格式和内容。最多支持六十四种数据类型。

如表 3 所示,有八种不同的数据类型类别。每个类别中最多有八种不同的数据类型定义。前两类表示短包数据类型。其余六类表示长数据包数据类型。

有关短数据包数据类型类别的详细信息,请参阅第 9.8 节。

有关五种长数据包数据类型类别的详细信息,请参阅第 11 节。

包头纠错码:Packet Header Error Correction Code

数据标识符和字计数值的正确解释对于数据包结构至关重要。

包头纠错码字节允许纠正数据标识符和字计数中的单位错误以及检测两位错误。

应使用第 9.5.2 节中描述的代码的 24 位子集。因此,ECC 字节的第 7 位和第 6 位应为零。基于 ECC 解码的错误状态应在接收器的应用层可用。

数据标识符字段 DI[7:0] 应映射到 ECC 输入的 D[7:0],

字计数 LS 字节 (WC[7:0]) 映射到 D[15:8],字计数 MS 字节(WC[15:8]) 至 D[23:16]。

该映射如图 35 所示,它也是 ECC 计算示例。

Synchronization Short Packet同步短包

短包数据类型应仅使用短包格式进行传输。 格式说明请参见第 9.1.2 节

帧同步数据包:Frame Synchronization Packets

每个图像帧应以包含帧起始码的帧起始(FS)数据包开始。

FS 数据包后面应跟随一个或多个包含图像数据的长数据包以及零个或多个包含同步代码的短数据包。每个图像帧应以包含帧结束代码的帧结束(FE)数据包结束。

有关同步代码数据类型的说明,请参见表 6。

对于 FS 和 FE 同步数据包,短数据包数据字段应包含 16 位帧号。对于与给定帧对应的 FS 和 FE 同步数据包,该帧号应相同。16 位帧号在使用时应为非零,以区别于帧号不起作用并保持设置为零的用例。16 位帧号的行为应为以下之一

• 帧号始终为零 – 帧号不起作用。

• 对于具有相同虚拟通道的每个 FS 数据包,帧号递增 1,并定期重置为 1,

例如1, 2, 1, 2, 1, 2, 1, 2 或 1, 2, 3, 4, 1, 2, 3, 4

帧编号必须是非零值。

RAW10

DATA TYPE ID

10位Raw数据的传输是通过将10位像素数据打包成8位数据格式来完成的。表 24 指定 RAW10 数据包的数据包大小限制。每个数据包的长度必须是表中值的倍数。

图 97(VGA 情况)说明了该序列。

传输中的位顺序遵循一般 CSI-2 规则,LSB 在前。

所以每个RAW帧的构成:

0x00 FS帧同步+具体数据+ 0x01 FE

一个长包包含一幅图像的一行像素点数据。

多通道分配和合并:Multi-Lane Distribution and Merging

CSI-2 是一种通道可扩展规范。需要比一个数据通道提供的带宽更多的应用程序,或者那些试图避免高时钟速率的应用程序,可以将数据路径扩展到两个、三个或四个通道宽,并获得峰值总线带宽的近似线性增加。高层数据和串行比特流之间的映射被明确定义,以确保主机处理器和使用多个数据通道的外设之间的兼容性。

从概念上讲,PHY 和更高功能层之间有一个处理多通道配置的层。

在发送器中,该层将数据包字节序列分布在 N 个通道上,其中每个通道都是物理层逻辑(串行器等)和传输电路的独立单元。在接收器中,它收集来自 N 个通道的传入字节,并将它们合并(合并)为完整的数据包,以传递到数据包分解器。

最高支持是4-Lane。

通道分配器接受任意字节长度的传输,缓冲 N 个字节(其中 N = 通道数),然后跨 N 个通道并行发送 N 个字节组。

在发送数据之前,所有通道并行执行 SoT 序列,以向其相应的接收单元指示数据包的第一个字节正在开始。

SoT 之后,通道按照循环过程并行发送第一个数据包中的连续字节组。

示例:

• 2 通道系统(图 22):

数据包的字节 0 进入通道 1,字节 1 进入通道 2,

字节 2 进入通道 1,字节 3 进入通道 2,

字节 4 进入通道 1,并以此类推。

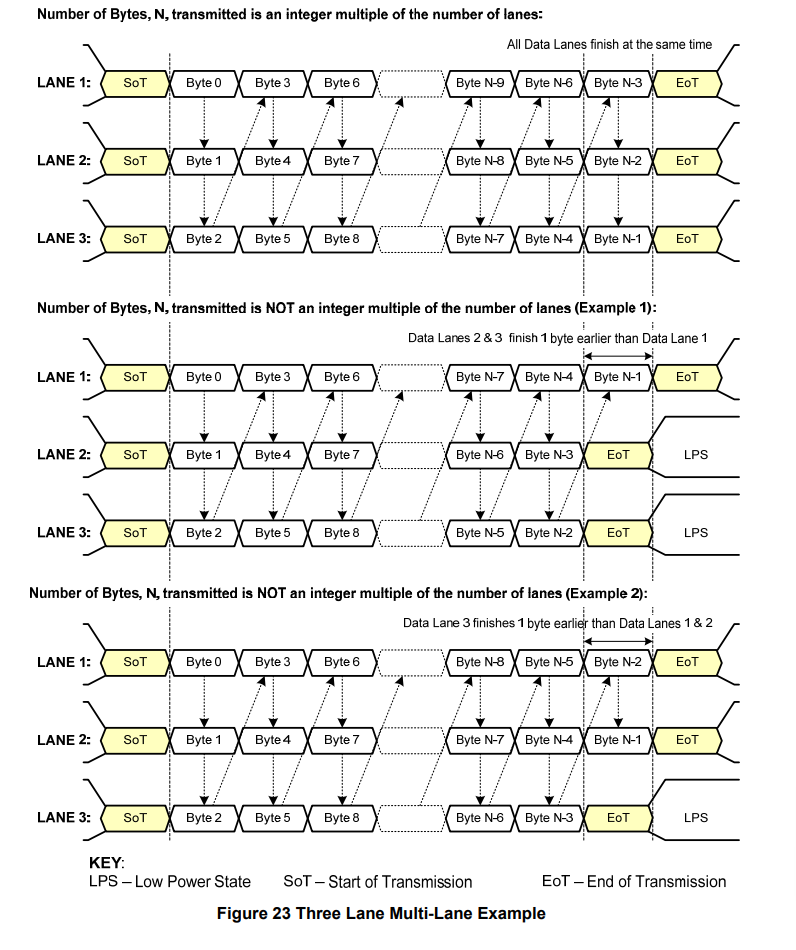

• 3 通道系统(图 23):

数据包的字节 0 进入通道 1,字节 1 进入通道 2,字节 2 进入通道 3,

字节 3 进入通道 1,字节 4 进入通道 2,依此类推。

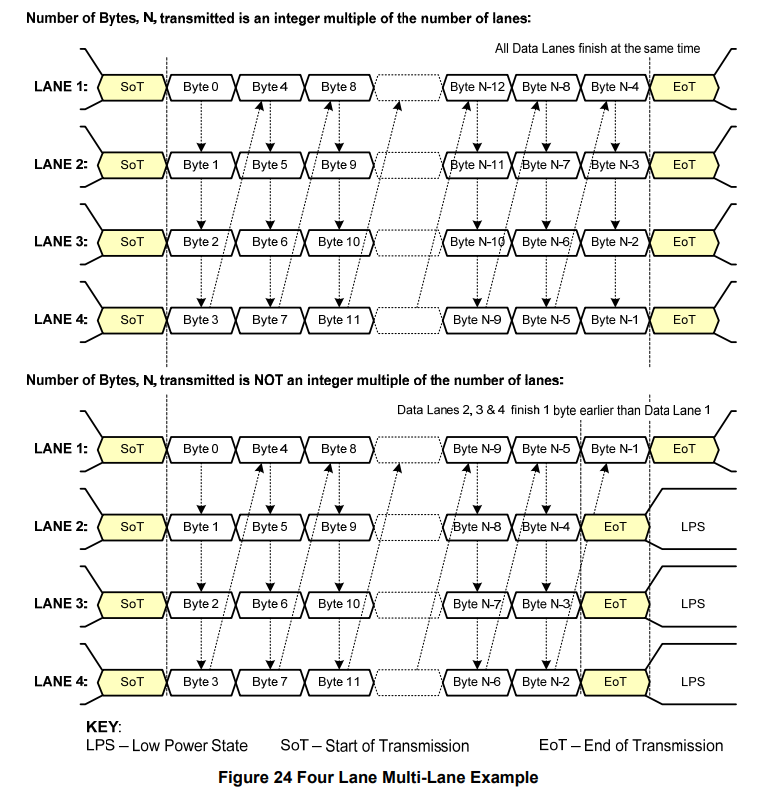

• 4 通道系统(图 24):

数据包的字节 0 进入通道 1,字节 1 进入通道 2,字节 2 进入通道 3,字节 3 进入通道 4,

字节 4 进入通道 1,依此类推。

在传输结束时,可能存在“额外”字节,因为总字节数可能不是通道数 N 的整数倍。

一个或多个通道可能会在其他通道之前发送其最后一个字节。

通道分配器在并行缓冲最后一组少于 N 个字节以发送到 N 个数据通道时,会取消将其“有效数据”信号发送到没有更多数据的所有通道。

每个 D-PHY 数据通道均自主运行。

尽管多个通道均以并行的“开始数据包”代码同时启动,但它们可能在不同时间完成事务,间隔一个周期(字节)发送“结束数据包”代码。

链路接收端的 N 个 PHY 并行收集字节,并将它们馈送到通道合并层。这会重构传输中的原始字节序列,然后可以将其划分为数据包解码器层的各个数据包。

)

)