名称:多路彩灯控制器LED流水灯花型verilog

软件:Quartus

语言:Verilog

代码功能:

用quartus和modelism,设计一个多路彩灯控制器,能够使花型循环变化,具有复位清零功能,并可以选择花型变化节奏。具体要求如下:

1)彩灯控制器由16路发光二极管构成,当控制开关打开时,能够自动在6种不同的花型之间循环变化。

2)控制器具有复位清零功能,当复位信号有效时,不管花型状态如何,都会立即清零,恢复到初始状态。

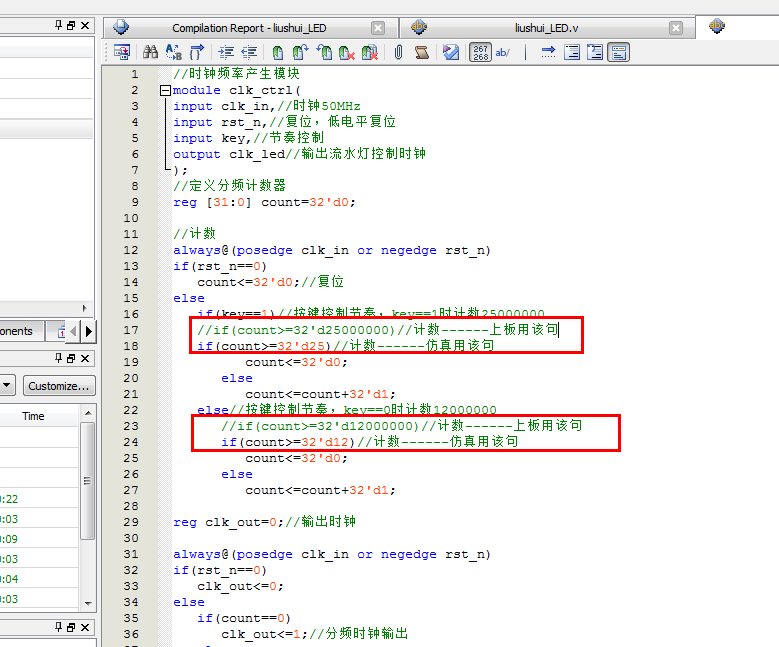

3)设置节拍控制开关,控制多路彩灯的花型以快慢两种节奏变化。

代码下载:多路彩灯控制器LED流水灯花型verilog_Verilog/VHDL资源下载名称:多路彩灯控制器LED流水灯花型verilog(代码在文末付费下载)软件:Quartus语言:Verilog代码功能: 用quartus和modelism,设计一个多路彩灯控制器,能够使花型循环变化,具有复位清零功能,并可以选择花型变化节奏。具体要求如下: 1)彩灯控制器由16路发光二极管构成,当控制开关打开时,能够自动在6种不同的花型之间循环变化。 2)控制器具有复位清零功能,当复位![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=188

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=188

FPGA代码资源下载网:hdlcode.com

部分代码展示

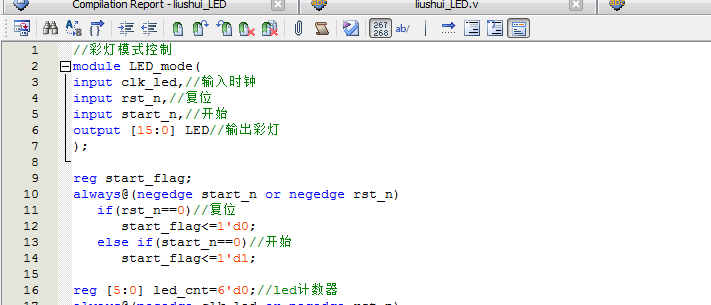

//彩灯模式控制 module LED_mode( input clk_led,//输入时钟 input rst_n,//复位 input start_n,//开始 output [15:0] LED//输出彩灯 );reg start_flag; always@(negedge start_n or negedge rst_n)if(rst_n==0)//复位start_flag<=1'd0;else if(start_n==0)//开始start_flag<=1'd1;reg [5:0] led_cnt=6'd0;//led计数器 always@(posedge clk_led or negedge rst_n)if(rst_n==0)//复位led_cnt<=5'd0;else if(start_flag)//开始beginif(led_cnt>=6'd39)//0~39循环led_cnt<=5'd0;elseled_cnt<=led_cnt+5'd1;//计数endreg [15:0] mode=16'b00000000_00000000; always@(posedge clk_led or negedge rst_n)if(rst_n==0)//复位mode<=16'b0000000000000000;elsecase(led_cnt)//根据计数控制LED5'd0: mode<=16'b10000000_10000000;//从左向右移5'd1: mode<=16'b01000000_01000000;5'd2: mode<=16'b00100000_00100000;5'd3: mode<=16'b00010000_00010000;5'd4: mode<=16'b00001000_00001000;5'd5: mode<=16'b00000100_00000100;5'd6: mode<=16'b00000010_00000010;5'd7: mode<=16'b00000001_00000001;5'd8: mode<=16'b00000010_00000010;//从右向左移5'd9: mode<=16'b00000100_00000100;5'd10:mode<=16'b00001000_00001000;5'd11:mode<=16'b00010000_00010000;5'd12:mode<=16'b00100000_00100000;5'd13:mode<=16'b01000000_01000000;5'd14:mode<=16'b10000000_10000000;5'd15:mode<=16'b10000001_10000001;//从两边向中间移5'd16:mode<=16'b01000010_01000010;5'd17:mode<=16'b00100100_00100100;5'd18:mode<=16'b00011000_00011000;5'd19:mode<=16'b00011000_00011000;//从中间向两边移5'd20:mode<=16'b00100100_00100100;5'd21:mode<=16'b01000010_01000010;5'd22:mode<=16'b10000001_10000001;

本代码已在AX301开发板验证,开发板资料:

AX301_UG.pdf

设计文档(文档点击可下载):

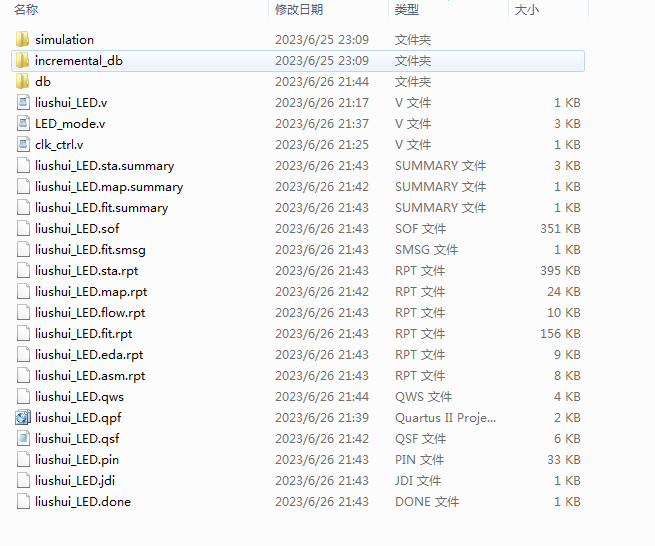

1. 工程文件

2. 程序文件

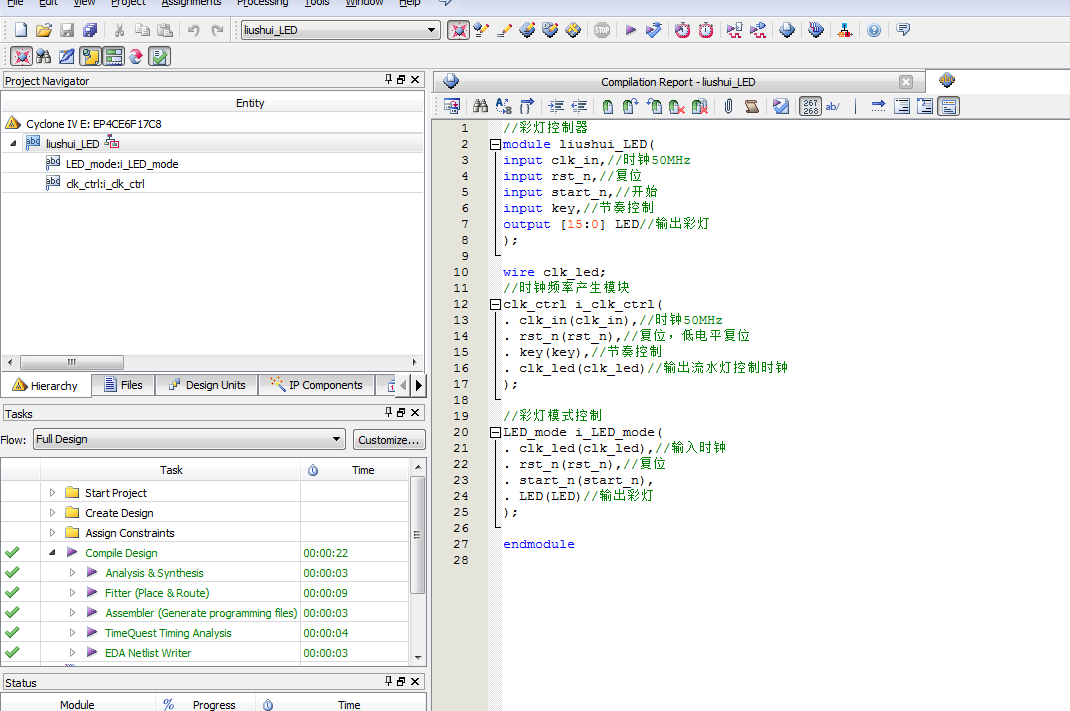

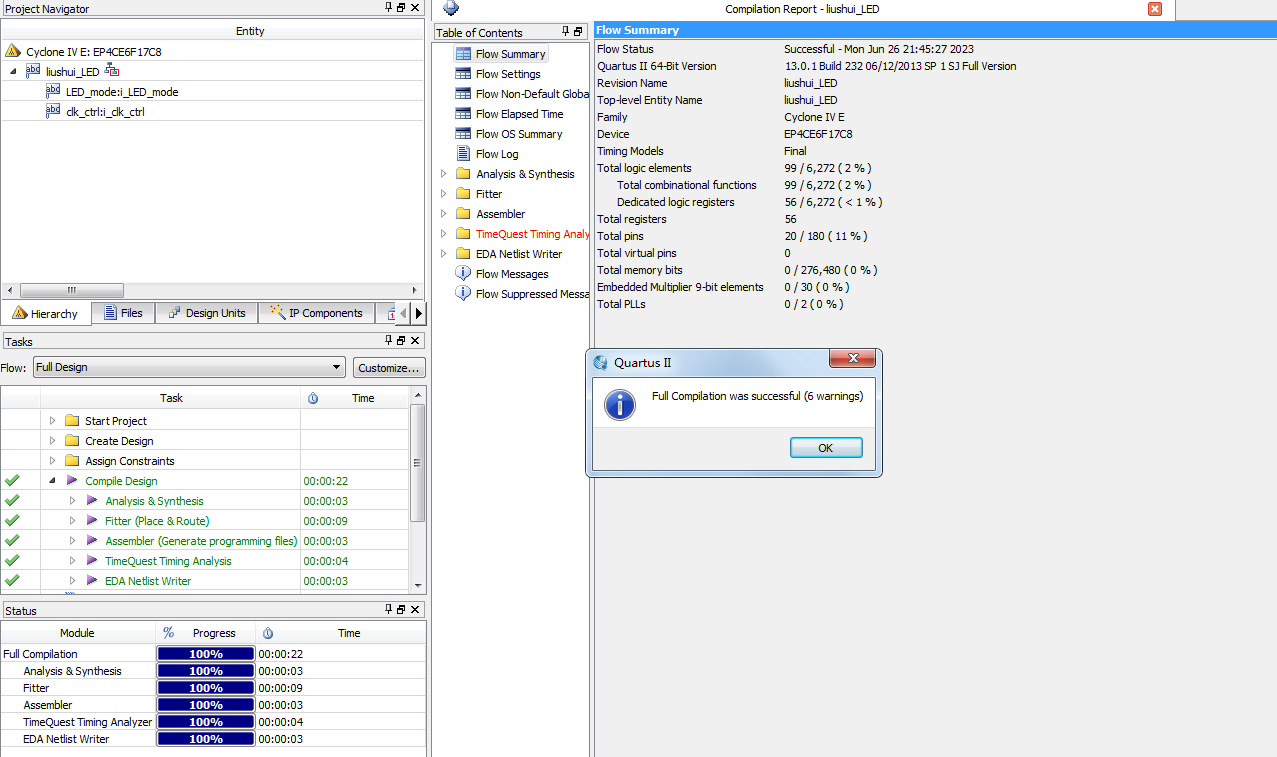

3. 程序编译

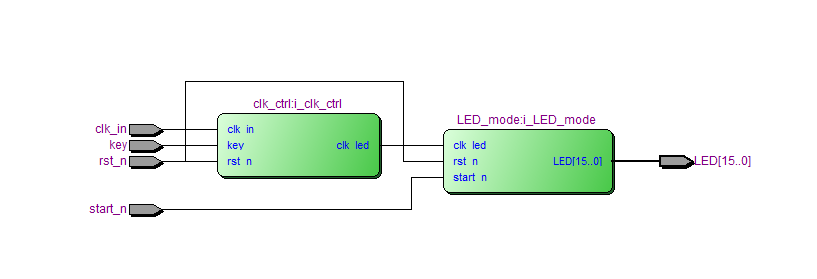

4. RTL图

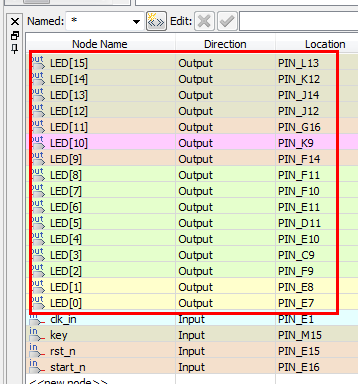

5. 管脚分配

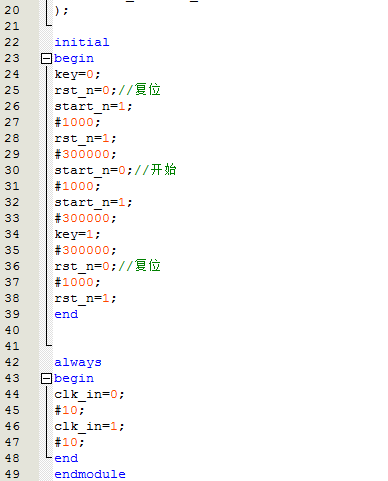

6. Testbench

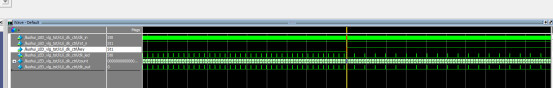

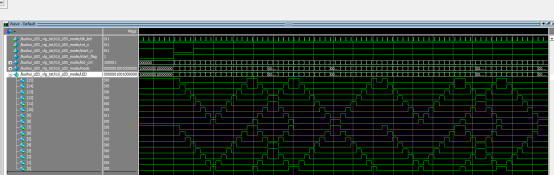

7. 仿真图

整体仿真图

时钟频率产生模块

彩灯模式控制模块

设计文档.doc

演示视频:多路彩灯控制器LED流水灯花型verilog_Verilog/VHDL资源下载

:C++编程常用技术)

.11)

)

![聊聊分布式架构05——[NIO基础]BIO到NIO的演进](http://pic.xiahunao.cn/聊聊分布式架构05——[NIO基础]BIO到NIO的演进)

真题解析#中国电子学会#全国青少年软件编程等级考试)