启动STARTUPEn Primitive (原语)参数在 FPGA的主 SPI模式下非常有用。当你启用这个参数时,对于 7 系列设备,STARTUPE2 原语会被包含在设计中;而对于 UltraScale™ 设备,则是 STARTUPE3 原语。这些原语在 FPGA 配置后成为IP核的一部分。

1 启用STARTUPEn 原语参数

STARTUPEn(如STARTUPE2或STARTUPE3)原语在FPGA设计中起着关键的作用,特别是在与FPGA的SPI配置接口相关时。

FPGA内部的一个输出端口SCK_O(即SPI的时钟输出)会与STARTUPEn原语连接。这个连接允许FPGA在配置过程中与外部的SPI从设备(通常是配置存储器)进行通信。在FPGA配置之前,STARTUPEn也可以用于预配置过程,其中外部SPI从设备会被预先配置。这个过程确保了FPGA在上电时可以立即从已知的状态开始工作。

在FPGA配置完成后,SCK_O端口会驱动STARTUPEn原语的USRCCLK0端口。这个信号在FPGA IP核外部是不可见的,因为它是内部连接的一部分。

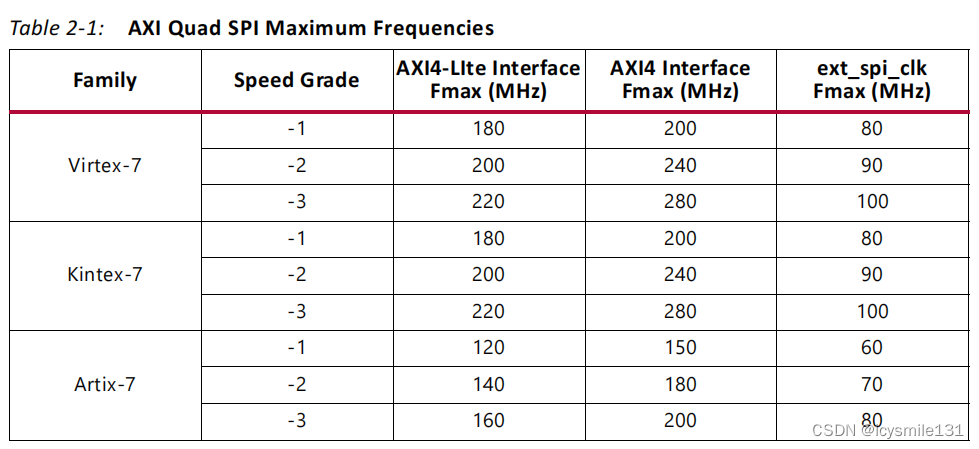

实例化STARTUPEn原语会影响ext_spi_clk(外部SPI时钟)的最大频率。这是因为STARTUPEn原语的性能会限制SPI接口可以支持的最大时钟速率。如下图所示:

注:对于xip和标准模式,ext_spi_clk可能被限制为60 MHz。

UltraScale™设备的频率数字预计与7系列相似。

上表中提到的频率特定于传统的SPI x 1模式。如果我们改变模式和其他设置,它们会发生变 化。

2 使用双通道四通道模式

启用Dual Quad模式这个参数仅在UltraScale™及未来系列的设备中,在特定的IP核配置下才有效。

-

Master mode:IP核工作在主模式下,即它是SPI通信的发起者和控制者。

-

STARTUP enabled

-

SPI mode is QUAD

-

Number of slaves is 2:IP核配置为与两个SPI从设备通信。

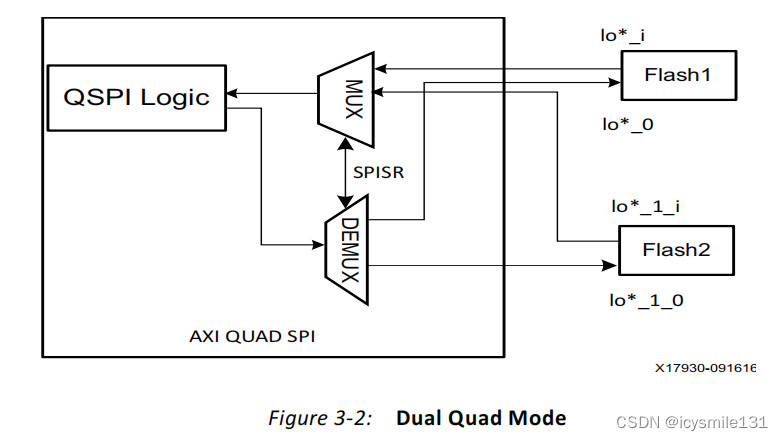

当“Enable Dual Quad Mode”参数被启用时,IP核将拥有两个SPI接口。这意味着它可以同时与两个flash存储器或其他SPI从设备通信,如图3-2所示。这提高了数据传输的效率和灵活性,允许IP核在单个时钟周期内与两个从设备交换数据。

在SPI通信中,当涉及到多个从设备时,数据流量的控制是通过从设备选择寄存器(SPISSR)来控制实现的。

3 不启用STARTUPEn 原语参数

SCK_O 和 IO1_I 端口是IP核的一部分,但由于它们不是IP核内部实例化的原语,这些端口作为IP核的外部端口存在,并被放置在用户配置位置的输入输出块(IOB, Input/Output Block)中。

(1) 在传统和增强非XIP模式下

无论是否选择了Enable Performance Mode,都设置该模式。这时,不选择Enable XIP Mode。AXI Quad SPI IP核支持Winbond、Micron、Spansion和Macronix存储器。当使用AXI Quad SPI IP核测试不同的存储器时,确实需要检查不同存储器所需的命令是否相同。如果不同存储器的命令、地址和数据行为都相同,那么可以选择其中一个设备作为基准存储器来测试IP核。

IP核通过内部逻辑了解目标内存的命令及其预期行为。当IP核尝试执行一个不被存储器设备支持的命令时,它会设置一个命令错误标志。一旦命令错误被设置,IP核将不会执行与该命令相关的SPI事务,并生成一个命令错误中断。这允许系统识别并响应不支持的命令,从而避免潜在的错误或数据损坏。

在命令阶段之后,如果包含地址相位,则根据地址模式位定义的模式,在SPI事务中传输下一个DTR(数据/地址/寄存器传输)内容。地址相位通常用于指定存储器中要访问的具体位置(例如,读取或写入的起始地址)。

如果特定命令包含数据相位,则根据读或写操作以及数据模式位设置的模式来执行数据相位。数据相位涉及数据的实际传输,无论是从存储器读取数据还是向存储器写入数据。

dummy bytes(虚拟字节)是在与某些存储器通信时,特别是在执行某些指令时,为了符合特定时序要求而插入的额外字节。这些虚拟字节并不包含实际的数据或地址信息,但它们对于确保命令的正确执行至关重要。

在SPI通信中,DTR(Data/Address/Register Transfer)是数据传输的基本单元,它可能包含地址、数据、控制信号或其他信息。当执行某些指令时,除了需要传输的实际数据字节数外,还需要在DTR中包含一定数量的dummy bytes。

对于读取命令,在传输地址位之后,IP核立即切换到输入模式,并开始在DRR中存储数据。因此,请注意有多少虚拟字节在DRR中被忽略。例如,对于Winbond存储器中的快速读取双输出命令,DTR应填充一个命令字节加三个地址字节加上dummy cycle(虚拟周期)的两个虚拟字节加上要从存储器中读取的虚拟字节数。命令和地址在标准SPI模式下传输,之后IP核切换到输入模式并开始存储数据。数据在IO0_I和IO_1线上传输,并存储在SPI DRR中,包括两个虚拟循环加上有效数据。因此,在读取SPI DRR时,忽略掉SPI DRR的前6个字节。FIFO中可用的有效数据从第七个字节开始。这也适用到其他双读取或四读取命令。

对于每个新事务,必须清除SPI DTR FIFO。SPI DTR中的第一个条目始终被视为命令条目,它与所选SPI模式的相应存储器的内置逻辑进行交叉检查。

(2)在XIP模式下

当“Enable Performance Mode”和“Enable XIP Mode”都被选中时,IP核将支持标准模式、双模式和四模式,具体设置和配置如下:

- 标准模式(Standard mode):设置“Mode”为“Standard”,“Slave Device”设置为Winbond、Micron、Macronix或Spansion等支持的存储器设备。

- 双通道模式(Dual mode):设置“Mode”为“Dual”,“Slave Device”同样需要设置为Winbond、Micron、Macronix或Spansion等支持的存储器设备。在双模式下,SPI通信将使用两条数据线(如IO0和IO1)同时进行数据传输。

- 四通道模式(Quad mode):设置“Mode”为“Quad”,“Slave Device”也需要是Winbond、Micron、Macronix或Spansion等支持四模式的存储器设备。在四模式下,SPI通信将使用四条数据线(如IO0、IO1、IO2和IO3)同时进行数据传输。

此模式的假设为:

Winbond存储器

当IP核在执行DIOFR或QIOFR命令之前被配置为双模式或四模式时,IP核会在上电复位(POR)后在AXI4接口接收事务之前向存储器写入高性能模式(HPM)命令。这个HPM命令需要一个命令周期和三个dummySPI周期来完成。这个HPM命令在存储器中的写入仅在系统上电时执行一次。当HPM命令成功写入后,Winbond存储器就被配置为高性能模式(HPM — 0xA3h),并允许DIOFR或QIOFR命令在相应的模式下进行操作。

在Micron存储器中,无论是易失性配置寄存器还是非易失性配置寄存器,其关于dummy周期的字段(VCR[7:4]和NVCR[15:12])在出厂时都被设置为默认值,即1111。IP核特征是基于这些dummy周期寄存器的默认设置(即1111)来设计的。这意味着,当这些寄存器保持默认设置时,IP核可以预期按照特定的行为模式来工作。

建议:不要更改默认的易失性配置寄存器(VCR)和非易失性配置寄存器(NVCR)配置。

在每个新事务开始时,IP核发送相应的命令、地址和所需要的dummy周期,然后接收数据。

Spansion 存储器

当IP核不直接写入状态寄存器,并假定在执行XIP模式之前已经完成这一配置时,这通常意味着系统设计师或开发者需要在系统启动或初始化阶段进行必要的配置。

当设置四通道模式时,Spansion内存必须预先通过写入配置寄存器来设置QUAD位为1。这一步骤是为了确保内存能够按照四通道模式进行工作,以提供更高的数据传输速率和吞吐量。

Macronix 存储器

在Macronix存储器中,配置寄存器负责处理虚拟周期的信息。虚拟周期的配置因配置寄存器中的bit6和bit7(DC0和DC1)的设置而异。默认情况下,bit6和bit7的值为00。

根据Macronix的数据手册,DC0和DC1的不同设置会对应不同的虚拟周期数量。

推荐:不要改变默认的配置寄存器配置。

)

从入门到精通系列之十九:Operator模式)

)

)