文章目录

- 一、模块框图

- 二、代码编写

- 三、注意点

- 四、总结

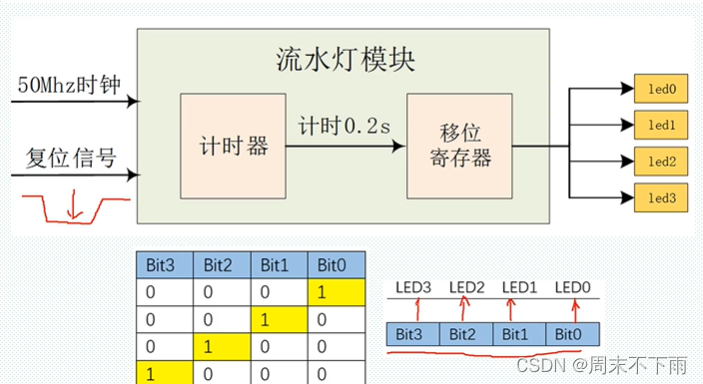

一、模块框图

二、代码编写

- endmodule下面需要敲出一个回车

- 代码拼接是大括号

led <= {led[2:0],led[3]} - 注意二进制和十进制

module flow_led(input sys_clk50,input rst_n,output reg [3:0] led

);reg [23:0] cnt;always @(posedge sys_clk50 or negedge rst_n)

beginif(!rst_n) // 低电平有效(为复位信号),此时计数器清零cnt <= 1'b0;elseif(cnt < 24'd10000000)cnt <= cnt + 1'b1;elsecnt <= 24'd0;

endalways @(posedge sys_clk50 or negedge rst_n)

beginif(!rst_n) // 低电平有效(为复位信号)led <= 4'b0001;elseif(cnt == 24'd10000000)led <= {led[2:0],led[3]};elseled <= led;

endendmodule三、注意点

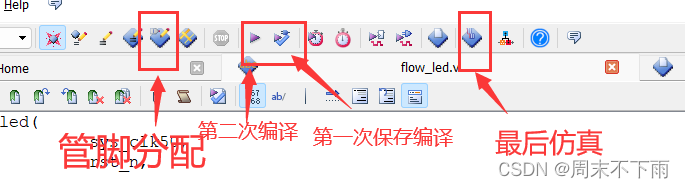

等会查查这些按钮

添加项目的时候,可以根据之前的文章的步骤一步步来就行

对于硬件管脚分配,查看execl表格就行

四、总结

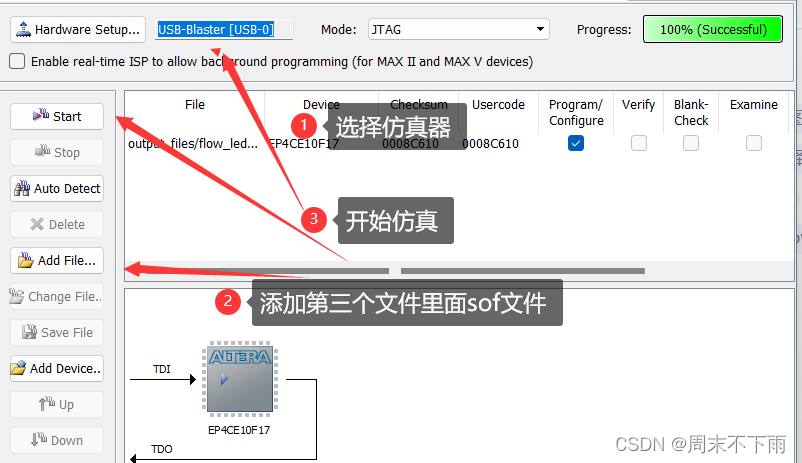

第一就是一些创建仿真流程有点生疏了,这个无所谓都是套路

第二就是数字进制和位宽的长度

第三就是变量的设置(寄存器类型等等,这个有点头疼,不知道应该在什么时候设置,什么地方设置)

第四的话,就是对于fpga这个东西是并行的有了一个粗浅的感觉,always就像一个主函数,几个always就像几个主函数并行运行,有点像中断的意思但也不是中断,就像进程的那种感觉。

)

)

)

异常最后解决手段)