目录

系统概述

概述

系统框图

应用框图

最小系统设计

时钟:

复位/看门狗/TSADC电路:

系统启动引导顺序:

系统概述

概述

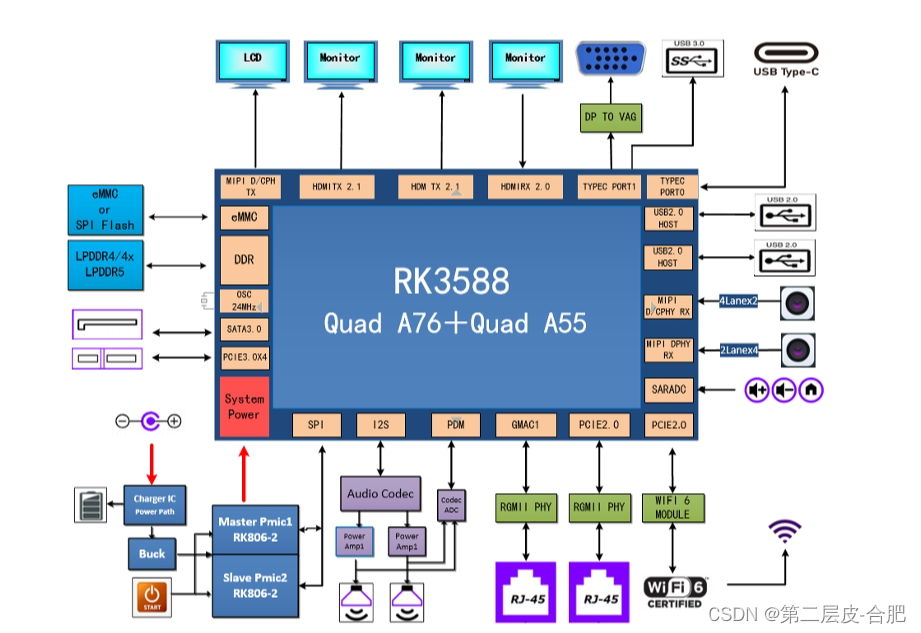

RK3588 是一颗高性能、低功耗的应用处理器芯片,由4个Cortex-A76和4个Cortex-A55 及独立的 NEON协处理器集成,适用于ARM PC、边缘计算、个人移动互联网设备和其它多媒体产品。 RK3588 内置了多种功能强大的嵌入式硬件引擎,为高端应用提供了优异的性能,支持8K@60fps 的 H.265 和VP9解码器、8k@30fps的H.264解码器和4K@60fps的AV1解码器;还支持8K@30fps的H.264 和H.265编码器,高质量的JPEG编码器/解码器,专门的图像预处理器和后处理器。 内置3D GPU,能够完全兼容OpenGL ES1.1/2.0/3.2、OpenCL 2.2 和Vulkan 1.2。带有 MMU的特殊2D 硬件引擎将最大限度地提高显示性能,并提供流畅的操作体验。 引入了新一代完全基于硬件的最大48M像素ISP(图像信号处理器),它实现了很多算法加速器,如 HDR、3A、LSC、3DNR、2DNR、锐化、去雾、鱼眼校正、伽马校正等。 内嵌的NPU支持INT4/INT8/INT16/FP16 混合运算,算力高达 6TOP。此外,凭借其强大的兼容性, 可以轻松转换基于TensorFlow/MXNet/PyTorch/Caffe 等一系列框架的网络模型。 RK3588 具有高性能的4通道外部存储器接口(LPDDR4/LPDDR4X/LPDDR5),能够支持苛刻的存储 器带宽(能够支持存储器高带宽要求的系统),还提供了一套完整的外设接口,以灵活支持各类应用。

系统框图

应用框图

最小系统设计

时钟:

RK3588 芯片内部的振荡器电路与外置的24MHz晶体一起构成系统时钟,如图2-1所示。XOUT24M 网络务必串接22ohm电阻,用于限流,防止过驱。XOUT24M和XIN24M网络之间的510Kohm电阻不可 随意修改。

系统时钟还可以直接由外部的有源晶体电路产生时钟,时钟幅度为 1.0V。工作情况下,时钟通过 XIN24M脚输入,XOUT24M管脚悬空,

RK3588 可向外设提供工作时钟:

REFCLK_OUT:预留时钟输出引脚,根据实际需求选用;

CLK32K_OUT0:32.768KHz时钟输出,可提供给WIFI,BT,PCIe等设备当休眠或工作时钟; CLK32K_OUT1:32.768KHz时钟输出,可提供给WIFI,BT,PCIe等设备当休眠或工作时钟; ETH0_REFCLKO_25M:25MHz时钟输出,可提供给Ethernet PHY等设备当工作时钟;

ETH1_REFCLKO_25M:25MHz时钟输出,可提供给Ethernet PHY等设备当工作时钟;

GMAC0_CLKINOUT:50MHz、125MHZ时钟输入或输出,可提供给Ethernet PHY作为RMII数 据发送和数据接收参考时钟

GMAC1_CLKINOUT:50MHz、125MHZ时钟输入或输出,可提供给Ethernet PHY作为RMII数 据发送和数据接收参考时钟

MIPI_CAMERA0_CLK------MIPI_CAMERA4_CLK:默认24MHz时钟输出,可提供给Camera等 设备当工作时钟;也可根据PLL分频得到其它频点,并且每路时钟支持各自输出不同的频率。

PCIE20_REF_CLKP/N:输入或者输出100M时钟,默认100M时钟频率输出,给PCIE2.0设备用。

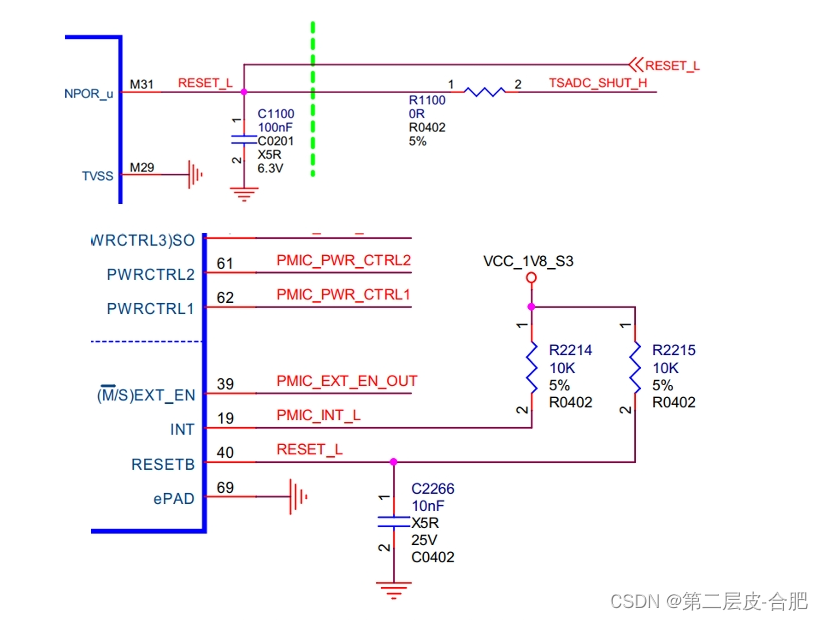

复位/看门狗/TSADC电路:

RK3588 芯片的硬件复位通过Pin M31(NPOR_u)管脚输入,必须由外部控制,低电平有效,为保证芯 片稳定和正常工作,所需的最短复位时间为100个24MHz主时钟周期,即至少4us以上。 Pin M31(NPOR_u)管脚需要增加100nF电容,用来消除复位信号上的抖动,增强抗干扰能力,防止误 触发导致的系统异常复位。 RESET_L网络的上拉电源必须和NPOR管脚所在的IO电源域(PMUIO1_1V8)保持一致。

RK3588 芯片内部集成了Watchdog Timer,当产生复位信号时,可以通过TSADC_SHUT管脚输出低 电平,对RK3588进行硬件复位。

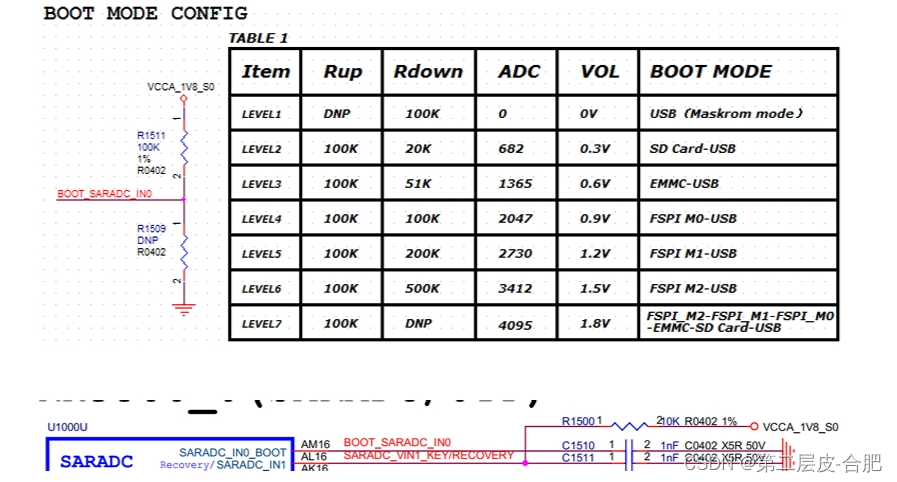

系统启动引导顺序:

RK3588 芯片支持多种启动引导方式,在芯片复位结束后,芯片内部集成的引导代码可以在如下接口 设备进行引导,具体引导顺序可根据实际应用需求进行选择(见下文中“引导顺序选择”描述)

Serial Flash(FSPI) eMMC SDMMC Card

如果在上述设备中没有引导代码,可以通过 USB2.0 OTG0 接口 TYPEC0_USB20_OTG_DP/ TYPEC0_USB20_OTG_DM 信号将系统代码下载到这些设备中。 引导顺序选择: RK3588 的Boot启动顺序可以通过SARADC_IN0_BOOT Pin(PIN AM16)进行设置,从不同接口对应的 外设启动,如下表所示硬件通过配置不同的上下拉电阻值,设计LEVEL1-LEVEL7七种模式的外设引导顺 序,可根据实际应用需求进行对应配置。

按照以上LEVEL1设置,SARADC_IN0_BOOT对地短路,可使设备进入Maskrom状态,无需再通过 短路EMMC_CLK/DATA进入Maskrom; SARADC_IN1用于对地短路进入Recovery状态;其它SARADC 口可根据应用需求配置。

?)

![[Flutter]环境判断](http://pic.xiahunao.cn/[Flutter]环境判断)