1、三态门介绍

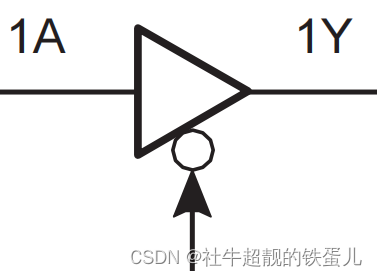

三态门和普通逻辑门相比,增加了一只使能(选通)引脚,如下图所示。

(1)当三态门的使能引脚有效时,三态门按照正常的逻辑功能进行工作。

(2)当三态门的使能引脚处于无效电平时,三态门输出高阻态,与所连接电路断开。

常用的三态门有74HC125、74LVC125A,总线收发器74HC244、74HC245则包含了8路三态门。此外,很多数字集成芯片的输出端均采用了三态门结构。

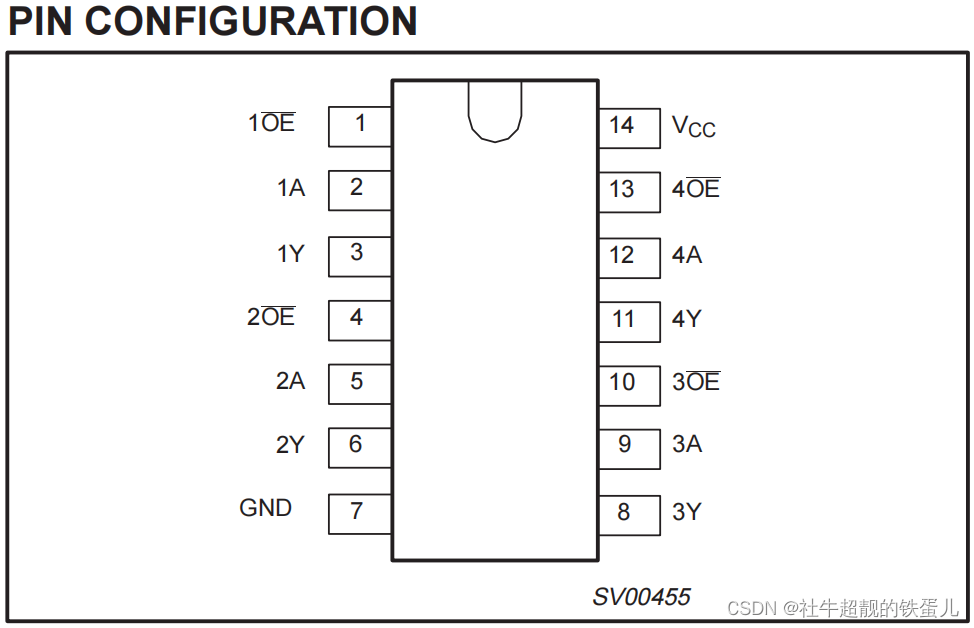

2、74LVC125A

74LVC125A是一款高性能、低功耗、低电压硅门CMOS器件,优于大多数先进的CMOS兼容TTL系列。输入信号可以来自3.3V或5.0V设备。在三态操作中,输出可以处理5V。74LVC125A包括四个非反向缓冲器/线路驱动器,具有三态输出。三态输出(nY)由输出使能输入(nOE)控制,nOE处于高电平时会使输出处于高阻态。

2.1 引脚分布和功能定义

Pin2/5/9/12_1A/2A/3A/4A:数据输入。

Pin1/4/10/13_1OE/2OE/3OE/4OE:数据输出使能输入(低电平有效&#x