一、前言

在之前的内容中,我们介绍了组合电路的时序问题和可能导致的毛刺,强烈推荐在阅读前文的基础上再继续阅读本文, 前文链接:FPGA时序分析与约束(1)——组合电路时序

这篇文章中,我们将继续介绍FPGA时序分析相关内容,本文介绍的是时序电路的时序问题。

二、时序电路时序

1、D触发器时序问题

1.1 回顾

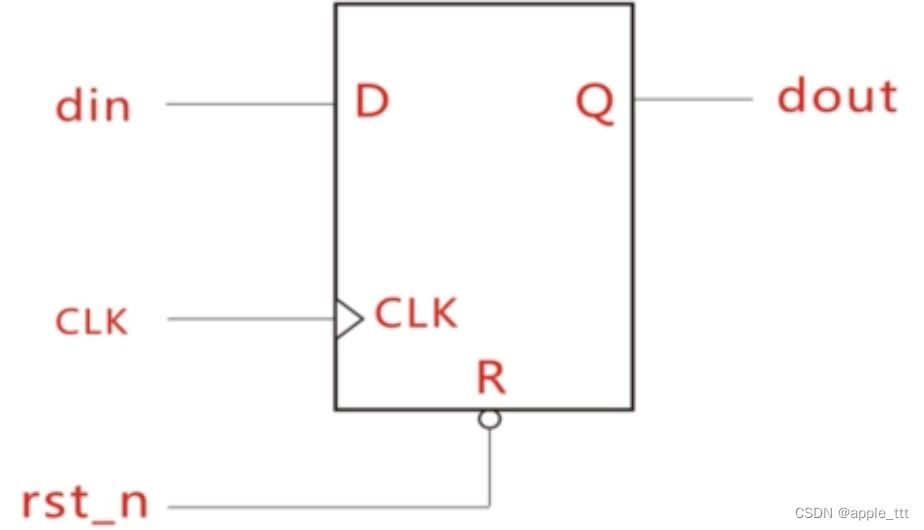

触发器(Filp Flop,FF)是一种只能存储一个二进制位(bit,比特)的存储单元,可以用作时序逻辑电路的记忆元件。FPGA逻辑单元中的D触发器(D-FF)是一种在时钟边沿将输入信号的变化传送到输出的边沿触发器。

D触发器的本质是由组合电路元件组成的。D、Q、CLK都有时序要求。

1.2 建立时间与保持时间

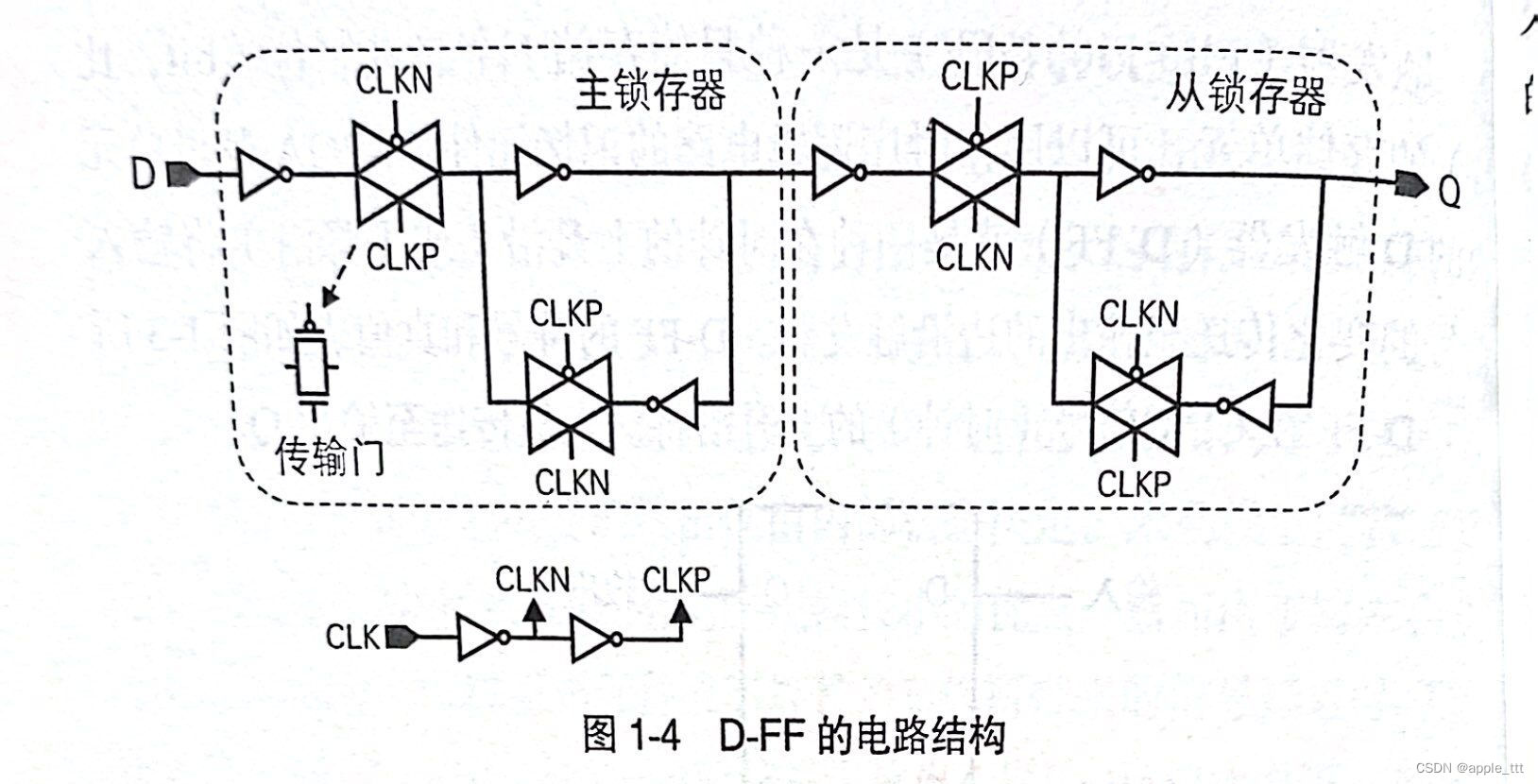

CMOS工艺下的D-FF结构如下图所示:

先由传送门和两个反相器组成一个循环电路(锁存器),再由前后两级锁存器按主从结构连接而成。 这里的传输门起开关的作用,随着CLK的状态变化切换开关。只看输入的话,前级锁存器的值将会随着时钟输入的变化有序地传输到后级锁存器。为了防止时钟信号变化时输入信号发生冒险,从而使稳定的输入信号进入前级锁存器,前级锁存器的时钟相位应该与产生输入信号的电路时钟相反。

D-FF电路原理图如下:

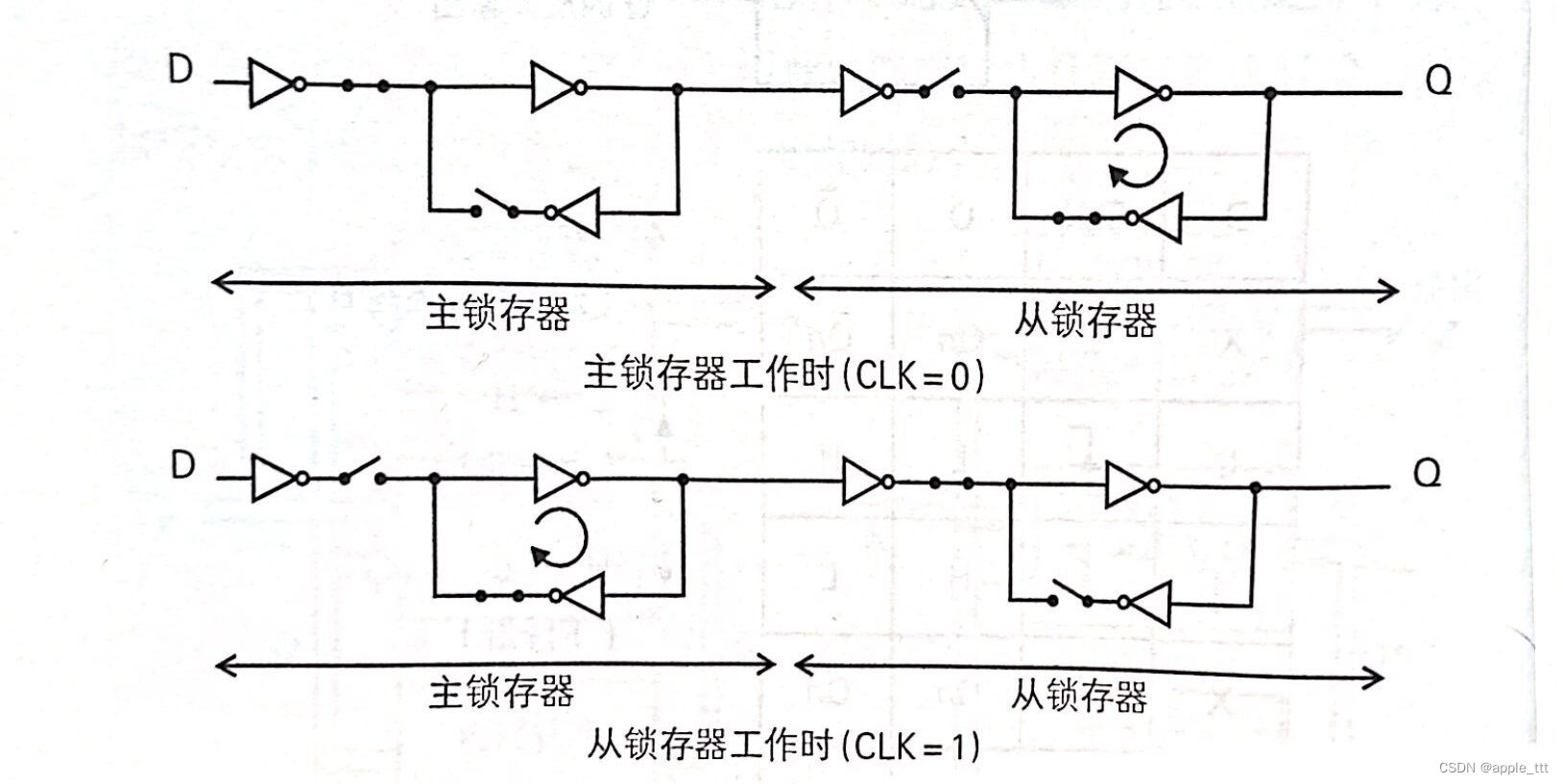

当CLK=0(主锁存器工作)时,位于前级的主锁存器将输入D的值保存进来,后级的从锁存器维持上一个时钟周期的数据。由于此时前级和后级反相器环路之间的传输门是关闭状态,所以前级的信号不会传送到后级。

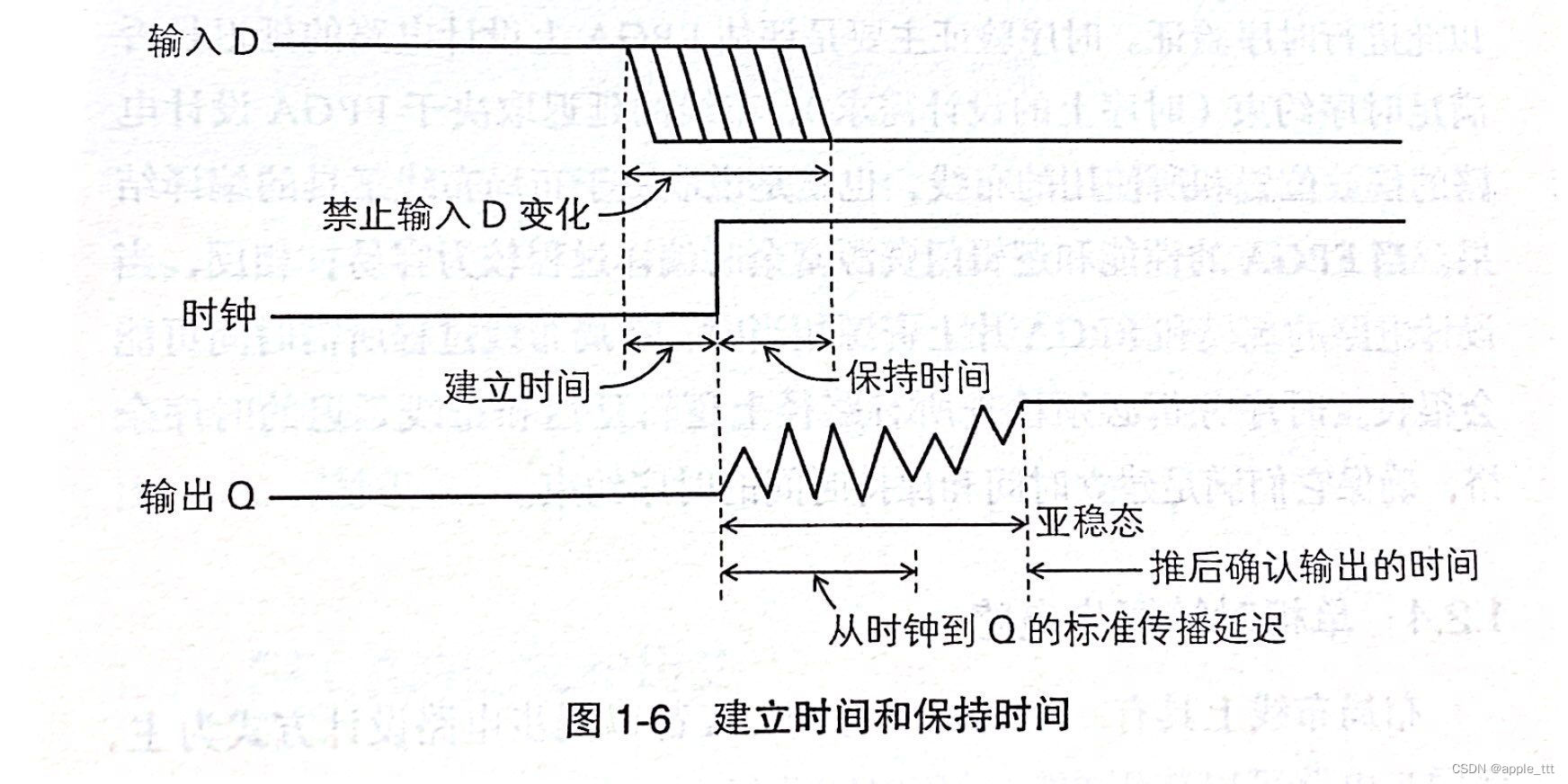

当CLK=1(从锁存器工作)时,前级反相器环路中保存的数据会传输到后级,同时输入D信号会被隔绝在外。如果此时前级反相器环路中的信号没有循环一周以上,就会出现在0和1之间摇摆的中间电位,这就是所谓的亚稳态。由于亚稳态时间比延迟时间长,在该阶段读取数据可能会引入错误,所以我们就引入了建立时间(setup time)来约束在时钟上升沿到来前输入D保持稳定的时间。

当CLK=1时,如果输入D在传送门关闭前就发生了变化,那么本该在下一个时钟周期读取的数据就提前进入了锁存器,就会引起反相器环路振荡或产生亚稳态。因此,在CLK=1之后也需要输入D维持一定的时间,我们称之为保持时间(hold time)约束。

所以总结一下就是:

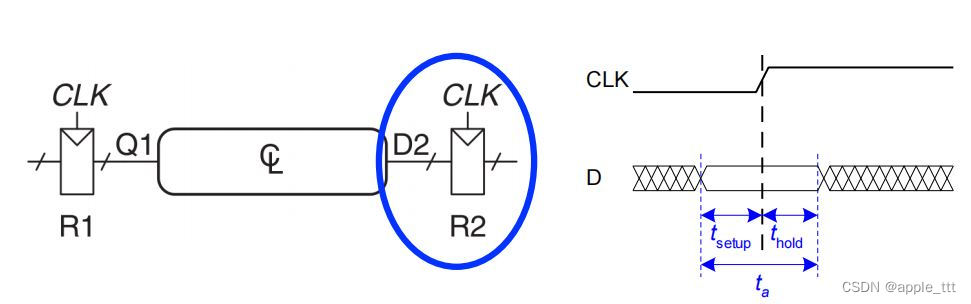

建立时间 Setup time (

): 时钟沿到来前数据信号必须保持稳定的最短时间

保持时间 Hold time(

): 时钟沿到来后数据信号必须保持稳定的最短时间

然后我们可以得到Aperture time (): 时钟沿附近数据信号必须保持稳定的最短时间

()

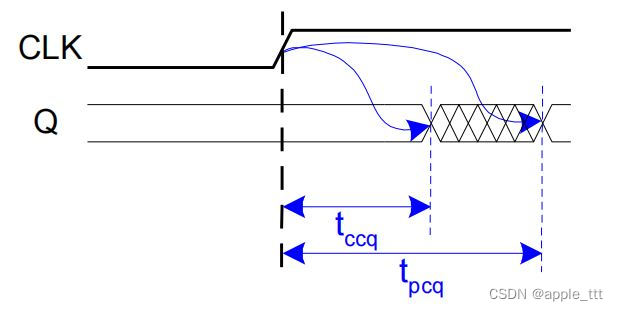

1.3 触发器输出时序

Contamination delay clock-to-q(tccq):在时钟沿过后,Q开始变化的最早的时间

Propagation delay clock-to-q (tpcq) : 在时钟沿过后,Q停止变化的最晚的时间

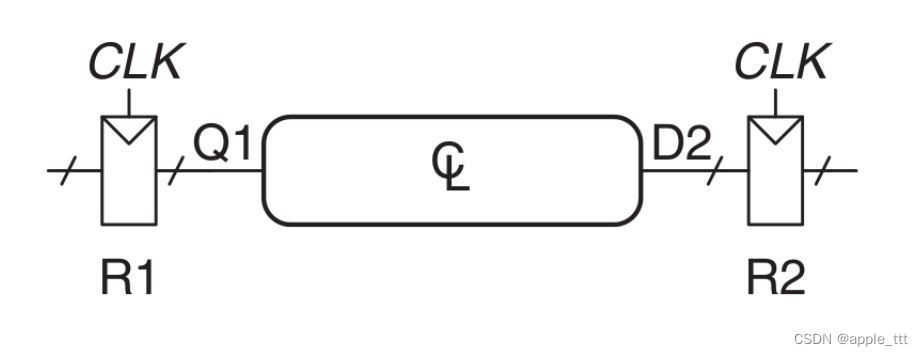

1.4 时序系统设计

多个触发器被连接到组合电路中,必须要满足每一个寄存器的时序要求:

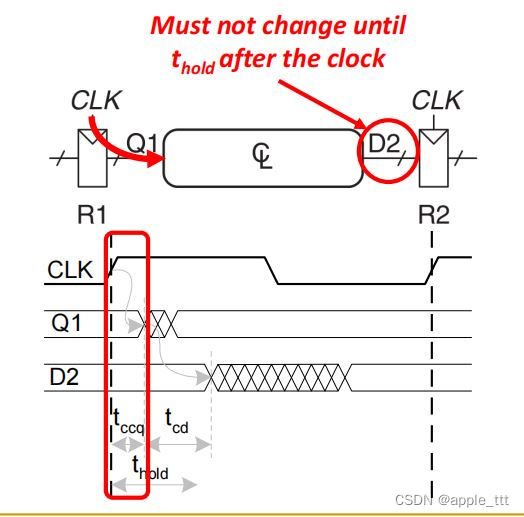

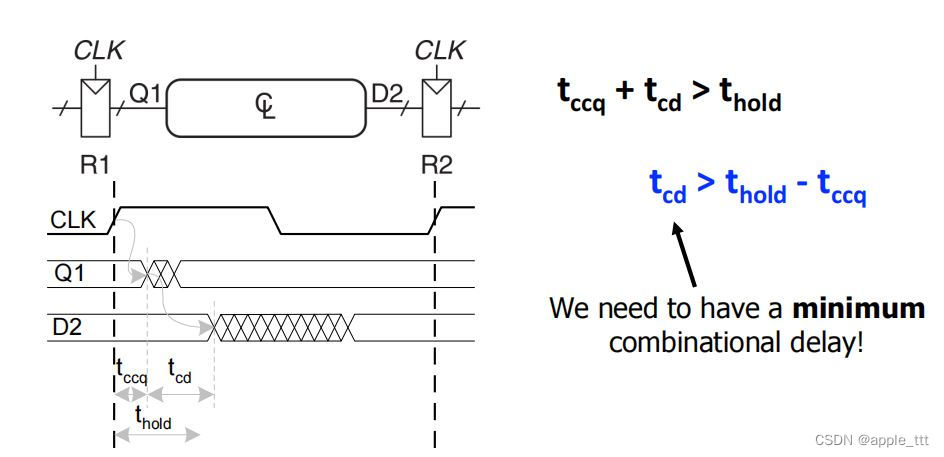

以上图为例,需要满足R1,R2两个寄存器的时序要求。也就要求确保R2的正确输入时序。也就要求满足R2的建立时间要求和保持时间要求。

这就意味着在两个触发器之间的组合逻辑电路需要有一个最小的时间延迟和一个最大的时间延迟:

(1)时间延迟太小(传播太快):违反R2的保持时间;

(2)时间延迟太大(传播太慢):违反R2的建立时间。

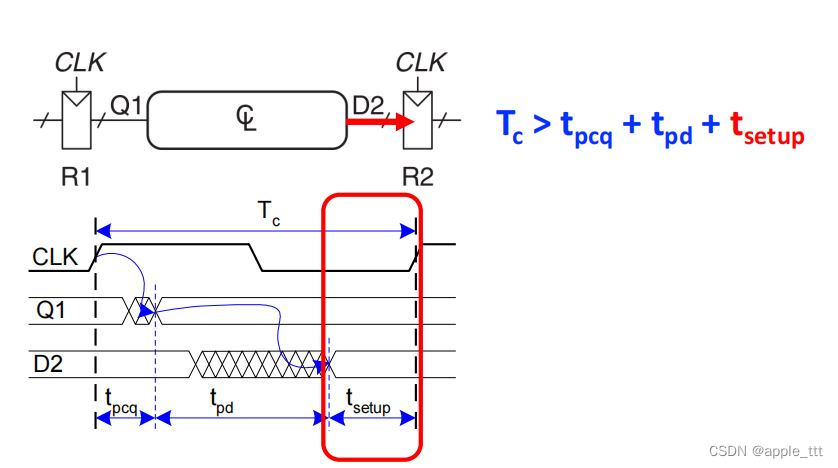

1.4.1 建立时间约束

安全时间取决于R1到R2的最大时间延迟,到达R2的输入信号必须在时钟沿到来前的建立时间内保持稳定(为时钟周期,

为Q停止变化的时间,

为组合电路输出结束变化的时间)

1.4.2 保持时间约束

安全时间取决于R1到R2的最小时间延迟,到达R2的输入信号D2必须在时钟沿到来后的保持时间内保持稳定(为Q开始变化的时间,

为组合电路输出开始变化的时间)

也就是说为了满足我们的设计不出现时序违规的情况,两个触发器R1,R2之间的组合电路被设置了一个最大时间延迟和一个最小时间延迟。组合电路的时延在这个范围之内。

三、总结

本文我们介绍了时序电路中的时序问题,这是我们进行进一步时序分析内容学习的重要理论基础,首先我们介绍了D触发器相关内容,着重说明了建立时间和保持时间的含义和产生原因,然后引入了触发器的输出时序,最后介绍了时序电路系统的设计约束。

在后续的文章中,我们计划进一步讨论关于时钟的相关内容,毕竟除了组合逻辑电路和时序逻辑电路,我们现实中的时钟也是存在时延的。

)

)