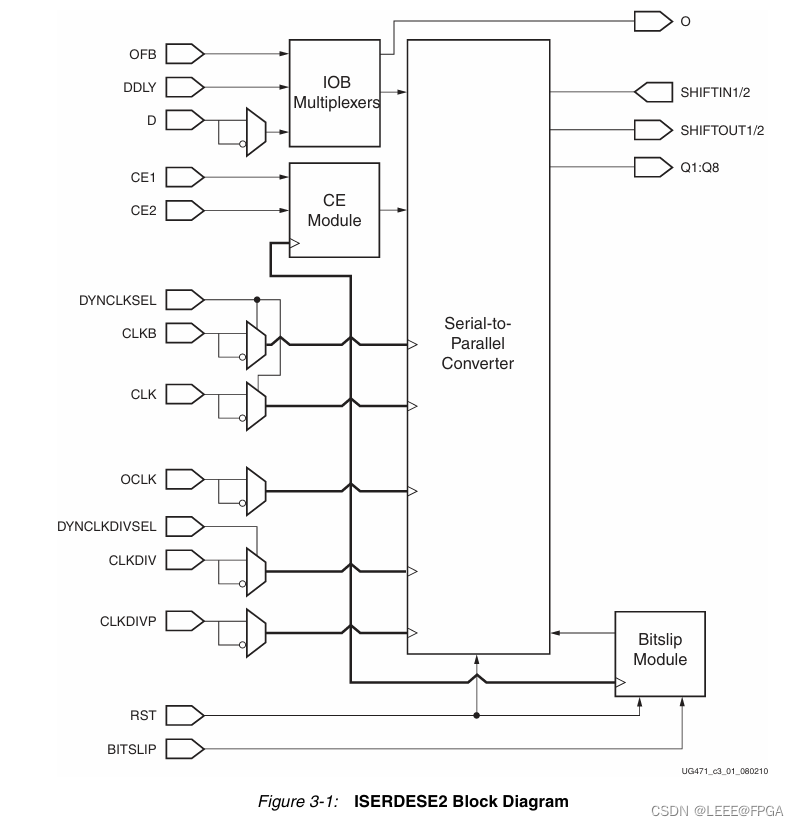

ISERDESE2 7 系列 FPGA 是一款专用的串行到并行转换器,具有特定的时钟和逻辑功能,旨在促进高速源同步应用的实现。该ISERDESE2避免了在FPGA架构中设计解串器时遇到的额外时序复杂性.

ISERDESE2功能包括:

1,专用解串器/串行转换器 ISERDESE2解串器可实现高速数据传输,而无需FPGA架构匹配输入数据频率。该转换器支持单数据速率 (SDR) 和双倍数据速率 (DDR) 模式。在 SDR 模式下,串行到并行转换器可创建 2 位、3 位、4 位、5 位、6 位、7 位或 8 位宽的并行字。在 DDR 模式下,串行到并行转换器在使用一个 ISERDESE2 时创建 4 位、6 位和 8 位宽的并行字模式,在使用两个级联ISERDESE2时创建 10 位或 14 位宽的并行字。

2,Bitslip 子模块 Bitslip 子模块允许设计人员对进入 FPGA 架构的并行数据流的顺序进行重新排序。这可用于训练包含训练模式的源同步接口。

3,对基于选通的存储器接口的专用支持

ISERDESE2包含专用电路(包括 OCLK 输入引脚),用于完全在 ISERDESE2 模块内处理选通至 FPGA 时钟域交叉。这允许更高的性能和简化的实现。

对网络接口的专用支持

• 对 DDR3 接口的专用支持

• 对 QDR 接口的专用支持

• 对异步接口的专用支持

ISERDESE2框图,突出显示了模块的所有主要组件和功能,包括可选的逆变器。

ISERDESE2 Primitive (ISERDESE2)

、时序约束)

)

以及开发问题记录)

:Java类加载过程)

)