前言

首先了解差分逻辑电平结构,也包括单端逻辑电平

地址:常见的逻辑电平_常用的逻辑电平-CSDN博客

注:ECL >> PECL >> LVPECL演变而来;QDR(Quad Data Rate):四倍数据倍率

本文章只涉及差分逻辑电平:LVDS 、LVPECL、CML (高速)(最常用)

常见差分晶振的差分逻辑信号类型及特点介绍如下:

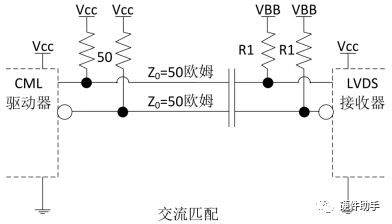

在任何给定的系统设计中,必须设计驱动器侧和接收器侧之间的时钟逻辑转换。通过在它们之间增加衰减电阻和偏置电路来将一个差分时钟转换为其他类型的差分逻辑,来衰减摆幅电平并重新偏置共模输入接收器。

由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平匹配将是电路设计中必须考虑的问题。

差分逻辑电平应用

差分逻辑电平主要应用于时钟信号、高速信号

比如高速信号应用于以太网接口MII:

LVDS电平: SGMI、QSGMI、PSGMII

CML电平:XAUI、XLAUI

HSTL电平: RGMII v2.0 (RGMII v1.3 采用CMOS电平)

差分逻辑电平匹配原则

1、电平关系,驱动器件的输出电压必须处在负载器件所要求的输入电压范围之内,并保证一定的噪声容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax≥0.4V)。

2、驱动能力,驱动器件必须能满足负载器件对灌电流、拉电流最大需求。

3、时延特性,设计中要充分考虑逻辑电平转换带来的延时,保证数据传输能满足负载器件的时序容限,特别是高速信号。

4、上升/下降时间特性,应保证Tplh和Tphl满足电路时序关系的要求和EMC的要求。

5、电压过冲要求,过冲不应超出器件允许的电压绝对最大值,否则有可能导致器件损坏。

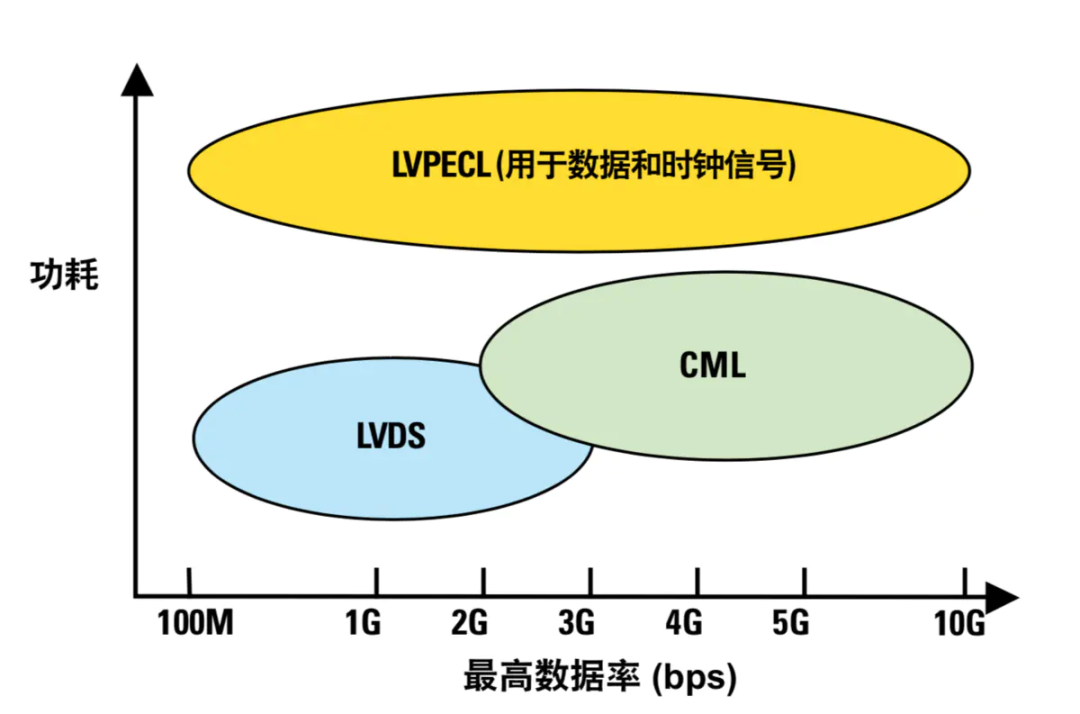

LVDS、LVPECL、CML比较

驱动模式:都属于电流驱动

外部端接:CML最简单,一般无需外部端接,直接连接即可;LVDS次之,需在接收端增加一个100Ω的终结电阻(内置的不需要);LVPECL最复杂,其输出端需偏置到VCC-2V,输入端需偏置到VCC-1.3V。

功耗:LVDS差分对摆幅最小,因此功耗也最小,在相同工作速率下,功耗不到LVPECL的三分之一;CML和LVPECL差分对摆幅相对较大,且内部三极管工作于非饱和状态,功耗较大,基于结构上的差异,CML的功耗低于LVPECL。

工作速率:由于CML和LVPECL内部三极管工作于非饱和状态,逻辑翻转速率高,能支持更高的数据速率;同时,由于LVDS差分对的输入摆幅较小(LVDS为100mV,LVPECL为310mV,CML为400mV;输出摆幅:LVDS为350mV,LVPECL为800mV,CML为800mV),噪声容限较小,不利于高速传输。

耦合方式:都支持直流耦合和交流耦合

同种差分逻辑电平之间的互连

| 输入 | ||||

| CML | LVPECL | LVDS | ||

| 输出 | CML | √ | √直流、交流耦合 | √直流、交流耦合 |

| LVPECL | √直流、交流耦合 | √直流、交流耦合 | √直流、交流耦合 | |

| LVDS | √直流、交流耦合 | √直流、交流耦合 | √ | |

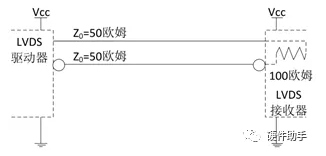

1、LVDS到LVDS的连接

1.1、直流耦合

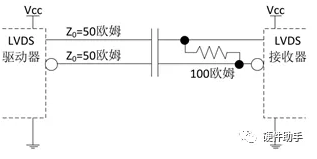

LVDS直接是可以直接连接的,不论是2.5V还是3.3V,无非是否在外部再放一个100欧姆匹配电阻。端接电阻要靠近接收端输入引脚!

内置100Ω端接电阻的连接方式

外接100Ω端接电阻的连接方式

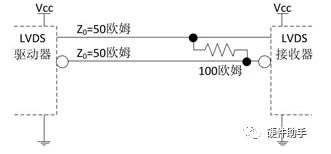

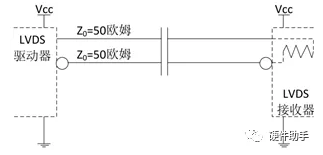

1.2、交流耦合

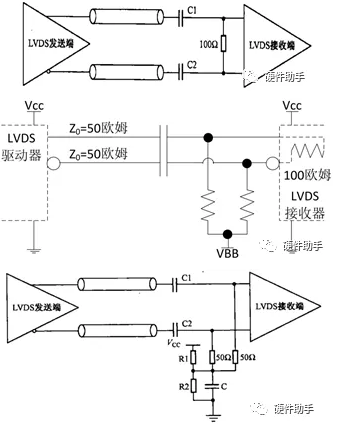

如果接收器输入端内置直流偏置,交流匹配也就是带不带100欧姆匹配的问题。

内置100Ω端接电阻的连接方式

外接100Ω端接电阻的连接方式

如果芯片没有内置直流偏置电压,就需要外接电阻到参考电压(1.2V)。为了支持传输线上的长0和长1数据序列,耦合电容的值不能太小,一般取0.1uF。C1、C2尽量靠近接收端放置,但不用像端接电阻那样紧贴输入管脚。

2、CML到CML的连接

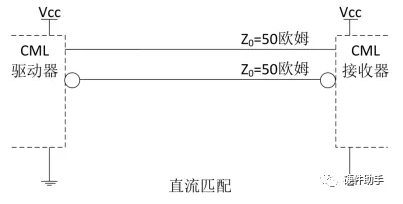

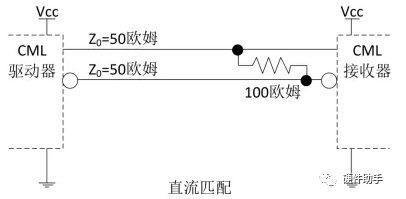

CML到CML之间连接分两种情况,当收发两端的器件使用相同的电源时,CML到CML可以采用直流耦合方式,这时不需加任何器件;当收发两端器件采用不同电源时,一般要考虑交流耦合,注意这时选用的耦合电容要足够大,以避免在较长连0或连1情况出现时,接收端差分电压变小。

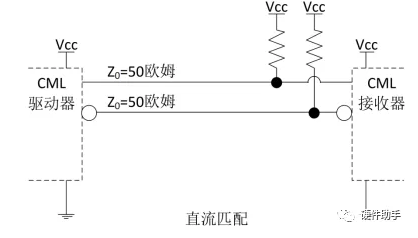

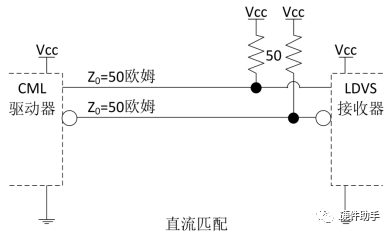

2.1、直流耦合

如果接收器的输入有内置匹配,如果接收器与发送器之间采用相同的VCC电源,CML驱动器输出可以直流耦合到CML接收器输入,无需额外的元件,可以直连。

直流匹配——直连

如果接收器的输入没有内置匹配,则需要在终端并接100欧姆匹配电阻。

直流匹配——100欧姆匹配

如果接收器的输入没有内置匹配,也可以通过在终端上拉50欧姆匹配电阻进行互连。

直流匹配——50欧姆上拉匹配

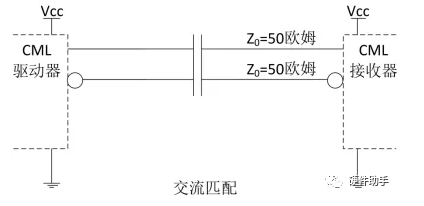

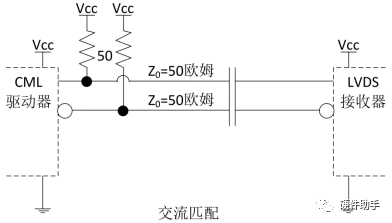

2.2、交流耦合

如果接收器与发送器采用不同的电源,系统需要用交流耦合方式。交流耦合情况下,耦合电容应足够大,以避免信号包含一长串相同数字时导致过大的低频衰减。

交流匹配——直连

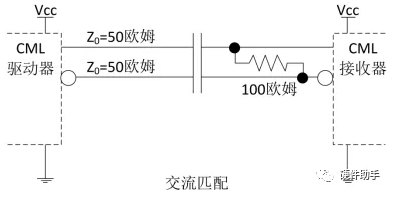

如果接收器的输入没有内置匹配,则需要在终端并接100欧姆匹配电阻。

交流匹配——100欧姆匹配

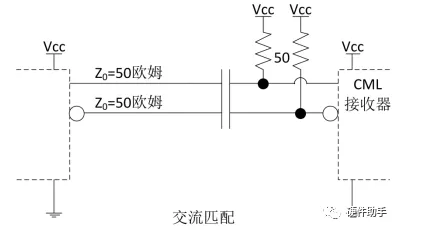

如果接收器的输入没有内置匹配,也可以通过在终端上拉50欧姆匹配电阻。

交流匹配——50欧姆上拉匹配

3、LVPECL到LVPECL的连接

3.1、直流耦合

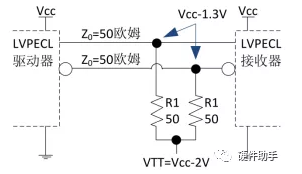

3.1.1、50欧姆匹配到参考电压

最简单的LVPECL匹配方式就是在接收器的输入侧需要一个参考电压,参考电压要比Vcc低2.0V,额外的电源需求会增加电路的复杂度和成本。Vcc-2.0V的偏置电压是考虑到ECL的14mA在50欧姆上的0.7V压降,在总线上的中间电平依然是Vcc-1.3V。

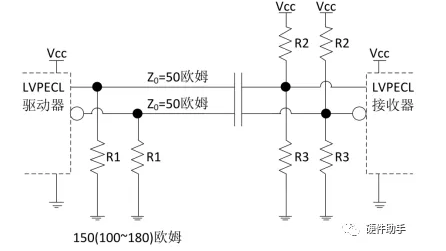

3.1.2、三电阻匹配

一种减少附加成本的方式就是增加一个电阻,两个50欧姆电阻提供信号匹配,另一个电阻连接到地给这两个电阻提供直流偏置到VTT。

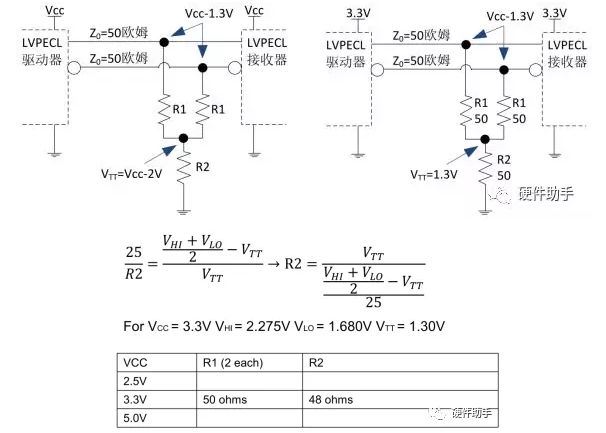

3.1.3、四电阻匹配

这是使用最多的LVPECL匹配方式,采用四电阻戴维南匹配。

四个电阻匹配的计算步骤如下:

a、从阻抗匹配要求可以得出:

R1||R2=50

b、电阻比等于电压比可以得出:

(R1+R2)/R2=VCC/(VCC-2)

Vcc-2.0V的偏置电压是考虑到ECL的14mA在等效50欧姆上的0.7V压降,在总线上的偏置电压依然是Vcc-1.3V。

于是可以得到:

R1=50*Vcc/(Vcc-2)

R2=25*Vcc

4个电阻都必须放在离输入端很近的地方,对PCB布板造成困难。匹配电阻功耗比较大,如果路数很多的话,对单板的功耗来说是一个比较大的问题(静态电阻很小)。所以,在实际的布板过程中,一般不提倡使用这种电路。

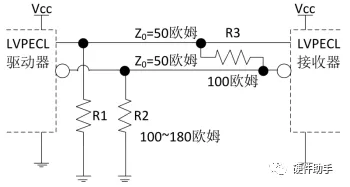

3.1.4、下拉+100欧姆跨接

这是最常用,最简洁的直流匹配方式,特别适合同电压PECL之间的对接。

R1=140~200欧姆(3.3V),R1=270~330欧姆(5V),R2=100欧姆。

R1为输出门提供偏置电流,R2为交流信号提供匹配。输入门的直流电平偏置直接利用输出门的直流电平(Vcc-1.3V),并不需要外来的上下拉电阻来提供。

此匹配电路电阻个数很少,只有3个。只有R2一个电阻必须放在离输入门比较近的地方,R1放置的地方可以比较随便,只要不引入过长的线头(过长的线头会导致反射)就可以了。PCB布板比较容易处理。这种电路是一个优选电路。

3.1.5、下拉+50欧姆匹配到参考电压

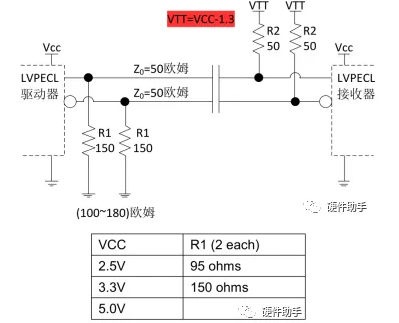

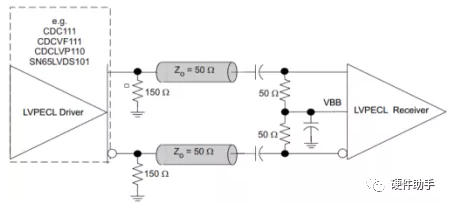

3.2、交流耦合

LVPECL在交流耦合输出到50Ω的终端负载时,要考虑PECL的输出端加一直流偏置电阻。LVPECL的输出共模电压需固定在Vcc-1.3V,在选择直流偏置电阻时仅需该电阻能够提供14mA到地的通路,这样R1=(Vcc-1.3V)/14mA。在3.3V供电时,R1=142Ω,5V供电时,R1=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,3.3V供电时,R1可以从142Ω到200Ω之间选取,5V供电时,R1可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。

R3和R2的选择应考虑如下几点:

a.PECL输入直流偏压应固定在Vcc-1.3V;

b.输入阻抗应等于传输线阻抗;

c.低功耗;

d.外围器件少。

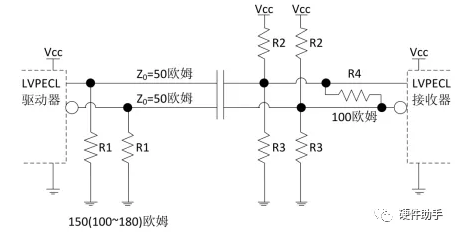

3.2.1、三电阻匹配

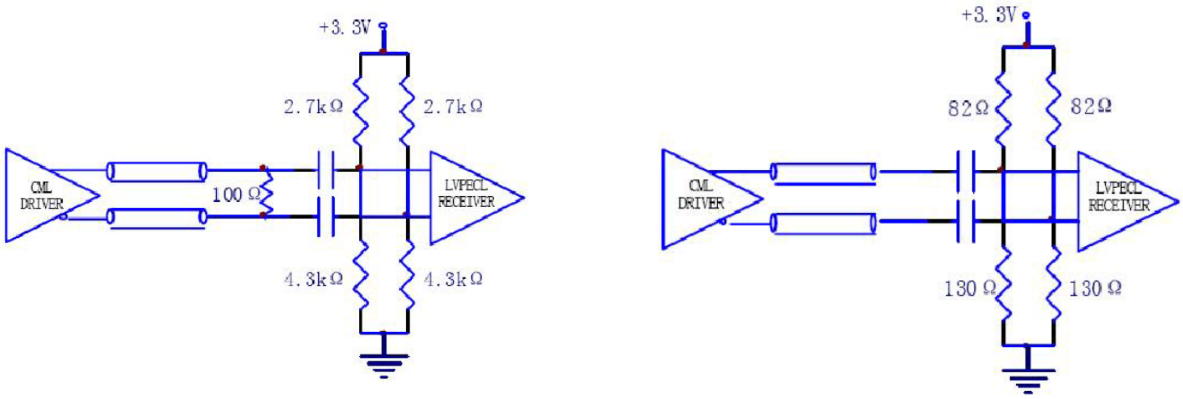

3.2.2、两电阻+100欧姆跨接

这是最常用,最简洁的交流匹配方式,也常用于PECL/LVPECL/2.5VPECL之间的对接,推荐使用。

R1=140~200欧姆,属于直流偏置电阻。

C1为耦合电容,可以放在线上的任何一个地方,不一定在源端,也不一定要在末端。

R4=100欧姆,属于交流匹配电阻,一定要放在末端。

R2、R3为K级别的电阻,必须满足R3/(R2+R3)=(VCC-1.3V)/VCC的比值就可以了,这两个电阻是为输入端提供直流电平,所以对PCB上的位置没有特殊要求,只需要不引入长线头就可以了。

对于交流耦合来说,阻容器件的个数算是比较少的了;只对一个电阻的位置(R4)有要求,其他的没有要求;功耗也比较小。这种电路还带来另外一个优点,那就是当LVPECL输出没有交流信号的时候,那么输入端却可以依靠100欧姆的电阻,使得P/N维持一个电压差,从而保证输入端的稳定。

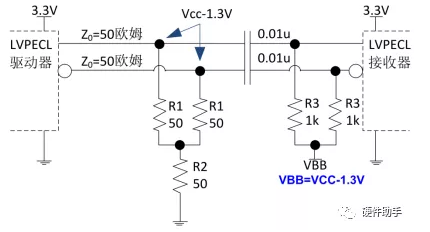

3.2.3、四电阻匹配

3.2.4、五电阻匹配

此处有了100欧姆电阻,R2和R3只是提供直流偏置而已,阻值需要选大一些,从而保证R2||R3||(R4/2)基本上还是50欧姆。3.3V情况下可以选择R2=2.2K,R3=3.3K,参考电压为大约为2V(Vcc-1.3V)。

两个50Ω电阻中点接入一电容,是为了消除差分线上信号偏移而产生的共模噪声(2个50Ω是差模阻抗匹配,VBB电容是共模滤波电容)。

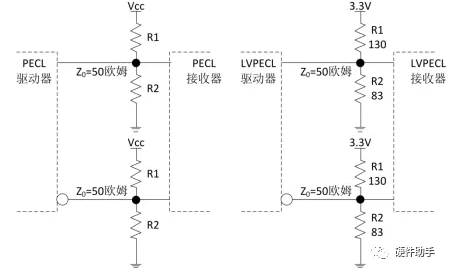

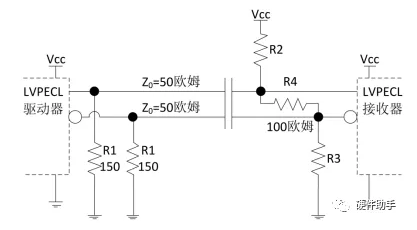

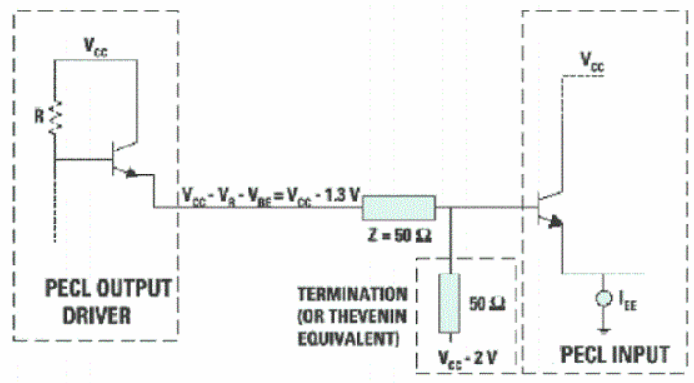

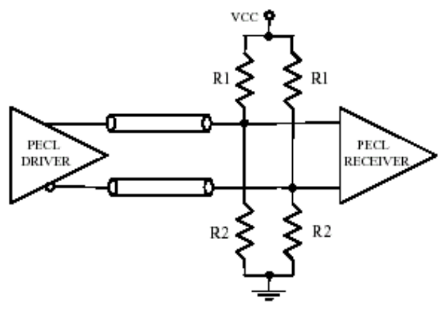

4、PECL到PECL的连接

PECL电平的直流偏置电路要求是戴维南等效终端电路为输出负载通过50Ω电阻接到VCC-2V的电源上,如图所示。在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V,输出电流典型值为14mA。

图、标准PECL终端

4.1、直流耦合

图、PECL直流耦合匹配电路

直流耦合的电路连接如图所示,差分单端线对交流信号的等效电路为连接50Ω阻抗到地;直流偏置的等效电路为连接50Ω电阻到VCC-2V,且通过50Ω电阻的电流为14mA。所以R1、R2满足的公式为:

R1//R2=50

交流等效:电压源短路,电流源开路

R2/(R1+R2)=(VCC-2V)/VCC

直流等效:14mA电流源与VCC电压源共同作用,使线上电压为VCC-1.3V;当只考虑14mA电流源时,负载为R1//R2,所以输出线路上的电压为0.7V;为满足要求,需要电阻分压为VCC-2V。

综合上面两式:

3.3V情况下:R1=130Ω R2=82Ω;

5V情况下:R1=82Ω R2=130Ω;

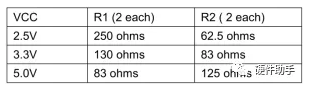

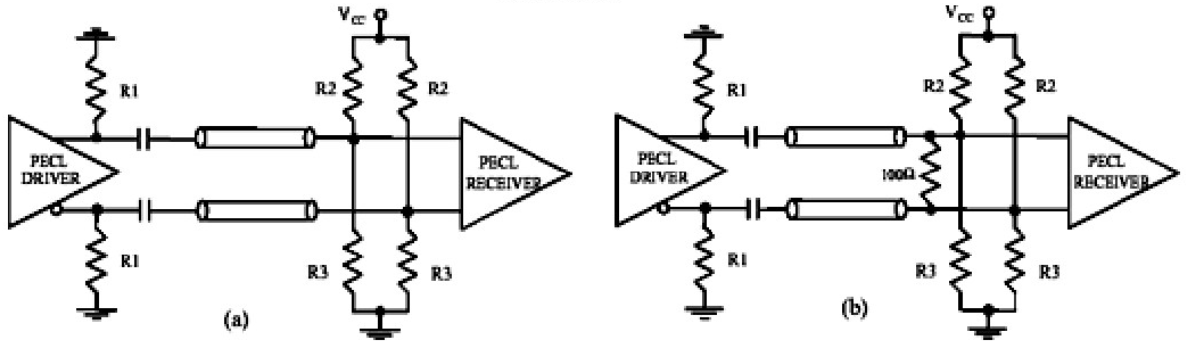

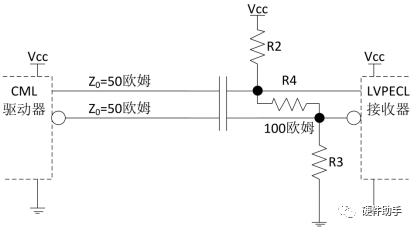

4.2、交流耦合

图、 PECL交流耦合匹配电路

交流耦合的电路连接如图所示,有a和b两种匹配方式;对于图a的匹配电路分析如下:

1.驱动端

交流:交流信号直接通过电容耦合至后级电路,耦合电容和电阻R1靠近输出端;

直流:R1提供14mA到地的通路,且信号线上的等效电压为VCC-1.3V,即R1=(VCC-1.3V)/14mA;(电源为3.3V时,R1=142Ω(一般取142Ω~200Ω);电源为5V时,R1=270Ω)

2.接收端

交流:R2//R3的等效电阻为50Ω;

直流:分压电路使线上电压偏压到VCC-1.3V,即R3*VCC/(R2+R3)=VCC-1.3V;

计算得:R2=50VCC/(VCC-1.3V) R3=50VCC/1.3V;

3.3V情况下:R2=82Ω R3=130Ω;

5V情况下:R2=68Ω R3=180Ω;

图b的匹配电路分析如下:

1.驱动端

交流:交流信号直接通过电容耦合至后级电路,耦合电容和电阻R1靠近输出端;

直流:R1提供14mA到地的通路,且信号线上的等效电压为VCC-1.3V,即R1=(VCC-1.3V)/14mA;(电源为3.3V时,R1=142Ω(一般取142Ω~200Ω);电源为5V时,R1=270Ω)

2.接收端

交流:R2//R3//50的等效电阻约为50Ω;

直流:分压电路使线上电压偏压到VCC-1.3V,即R3*VCC/(R2+R3)=VCC-1.3V;

所以R2和R3通常选如下值:3.3V情况下:R2=2.7K R3=4.3K;

5V情况下:R2=2.7K R3=7.8K;

不同种逻辑电平之间的互连

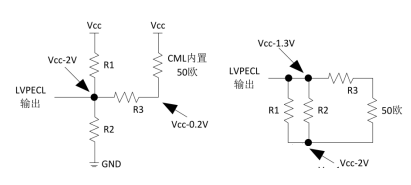

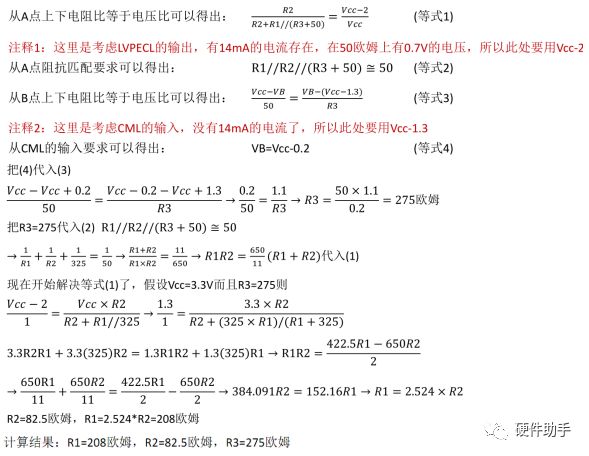

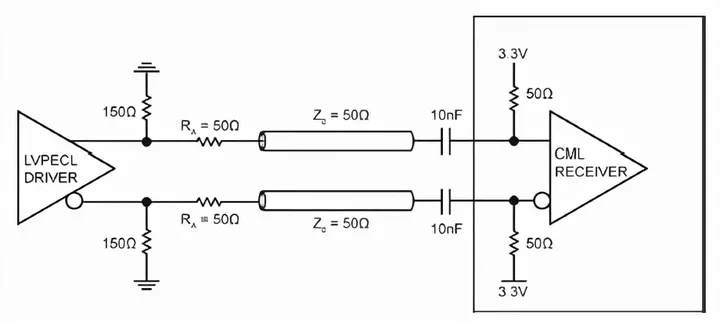

1、LVPECL到CML的连接

一般情况下,两种不同直流电平的信号(即输出信号的直流电平与输入需求的直流电平相差比较大),比较提倡使用AC耦合,这样输出的直流电平与输入的直流电平独立。

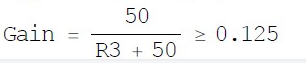

1.1、直流耦合

在LVPECL到CML的直流耦合连接方式中需要一个电平转换网络。

该电平转换网络的作用是匹配LVPECL的输出与CML的输入共模电压。

设计该网络时有几点考虑:

1、一般要求该电平转换网络引入的损耗要小,以保证LVPECL的输出经过衰减后仍能满足CML输入灵敏度的要求;

2、还要求从LVPECL端看到的负载阻抗近似为50Ω。

如果要连接LVPECL到CML,需要增加如上图所示的电阻网络来进行电平转换,从而同时满足LVPECL的输出和CML的输入要求。下一步计算同时满足LVPECL的输出和CML的输入要求的R1、R2和R3的数值。

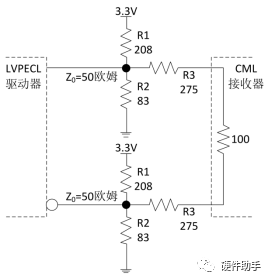

1.2、交流耦合

在LVPECL的两个输出端各加一个到地的偏置电阻,电阻值选取范围可以从142Ω到200Ω。

如果LVPECL的输出信号摆幅大于CML的接收范围,可以在信号通道上串一个25Ω的电阻,这时CML输入端的电压摆幅变为原来的0.67倍。(LVPECL输出摆幅600-1000mV,CML输入摆幅400-1000mV)。

如果LVPECL输出800mV>CML输入400mV,需要用额外的电阻降低电压幅度,此时需要R2≈50Ω,以衰减LVPECL摆幅电平的一半。

由于CML接收器内部一般包含50Ω的自偏置匹配电阻,所以耦合电容输出端直连CML接收器。

如果CML输入端的自偏置不存在,则必须在PCB上放置50Ω的端接电阻到VCC,用于CML偏置和传输线端接。

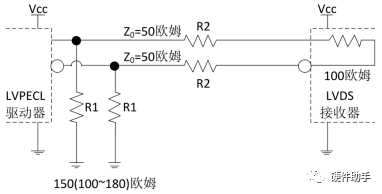

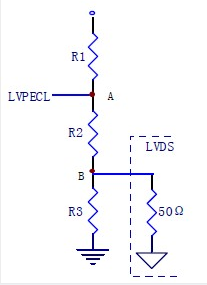

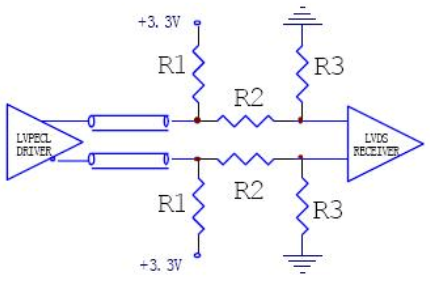

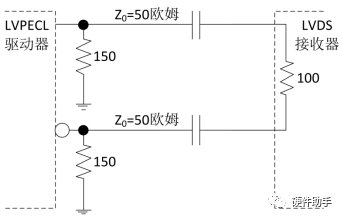

2、LVPECL到LVDS的连接

2.1、直流耦合

LVPECL到LVDS的直流耦合结构需要一个电平转换网络。

设计该网络时有几点考虑:

1、当负载是50Ω接到Vcc-2V时,LVPECL的输出性能是最优的,因此我们考虑该电阻网络应该与最优负载等效;

2、考虑该电阻网络引入的衰减不应太大,LVPECL输出信号经衰减后仍能落在LVDS的有效输入范围内。

3、注意LVDS的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等。

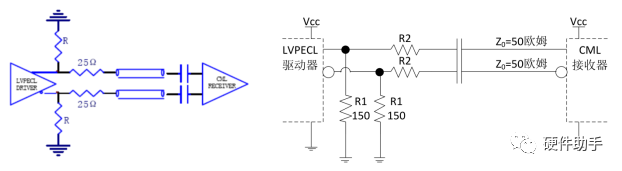

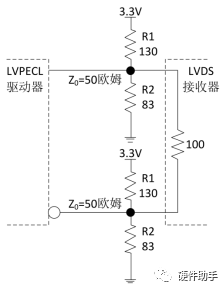

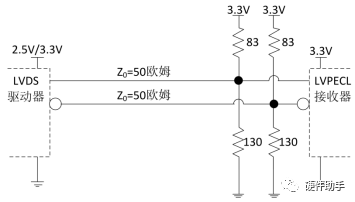

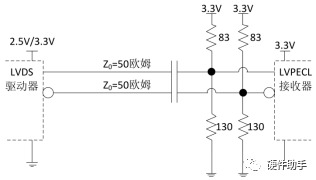

LVDS输入的差分阻抗为100Ω情况下直流耦合:

如果LVDS输入端可以承受比较大得差分电压(大部分LVDS接收器可以承受LVPECL输出的信号幅度),而且能承受VCC-1.3V的直流偏置电压,则不需要电阻分压了。

LVDS输入的差分阻抗每个单端到虚拟地为50Ω情况下直流耦合:

沿用130欧姆和83欧姆的模式,由于LVPECL的差分幅度一般大于LVDS的输入要求,所以对83欧姆进行了分压。这个电路既减少了交流摆幅到LVDS能承受的范围,也把直流偏置电压到LVDS需要的1.2V左右。

还有一种分压方式如下,摆幅被压缩了,但是直流偏置电压依然是LVPECL的VCC-1.3V。

(a) 等效电路 (b) LVPECL到LVDS的连接

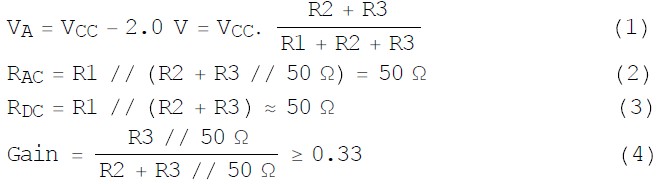

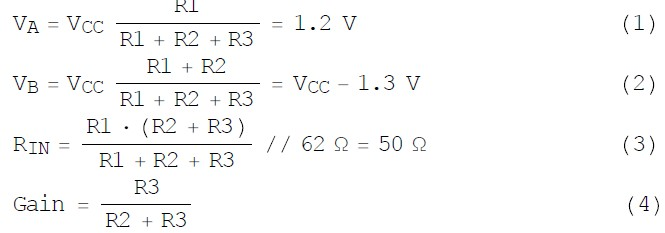

LVPECL 到LVDS 的直流耦合所需的电阻网络需满足下面方程组:

考虑Vcc=0.3V 情况,解上面的方程组得到:R1=182Ω,R2=48Ω,R3=48Ω,VA=1.14V,RAC=51.8Ω,RDC=62.8Ω,Gain=0.337。电路连接好,实测得VA=2.1V,VB=1.06V。

假定LVPECL单端最小输出电压为300mV,在LVDS 的输入端可达到100mV,能够满足其灵敏度要求。考虑信号较大时,如果LVPECL 的最大输出为1V,LVDS 的单端输入电压则为337mV,同样可以满足指标要求。

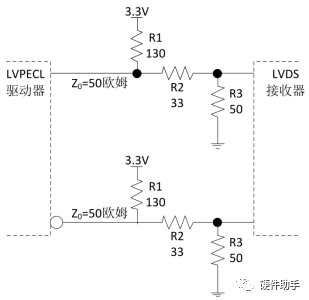

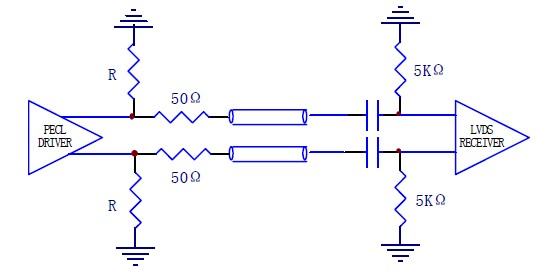

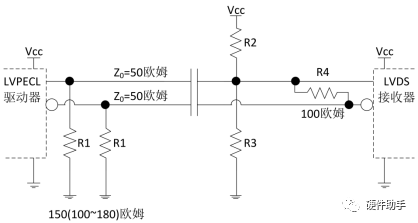

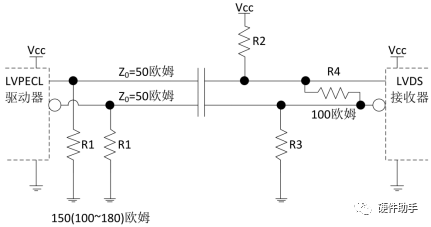

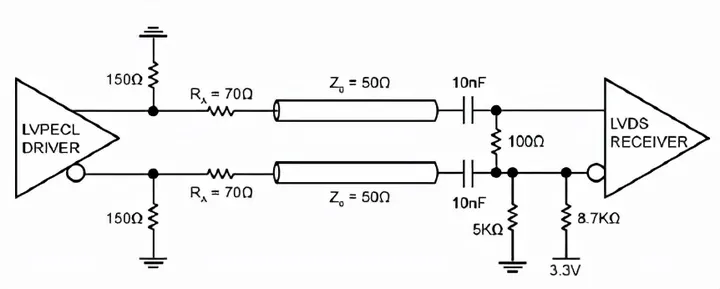

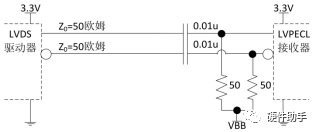

2.2、交流耦合

在LVPECL的两个输出端各加一个到地的直流偏置电阻,电阻值R选取范围可以从142Ω到200Ω。同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS的输入端到地需加5KΩ电阻,以提供近似0.86V 的共模电压。(LVDS输入端并联100Ω电阻,对于交流来说没有地电平,只有虚拟地电平,所以加5K电阻到地,确定实际地电平)。

LVPECL到LVDS交流耦合方式

由于LVDS芯片一般内置100欧姆匹配和偏置,直接下拉后加电容即可。

如果LVDS接收端没有内置偏置和匹配电阻,就需要外接提供100欧姆匹配和K级别电阻提供1.25V的直流偏置。若LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

为了将800mV LVPECL摆幅衰减到325 mV LVDS摆幅,必须在150Ω电阻器之后放置一个70Ω的衰减电阻。应在LVDS接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。LVDS输入需要重新偏置,可以通过向GND放置8.7KΩ电阻连接到3.3V和5KΩ电阻到GND来实现LVDS接收器输入共模的1.2V直流电平。

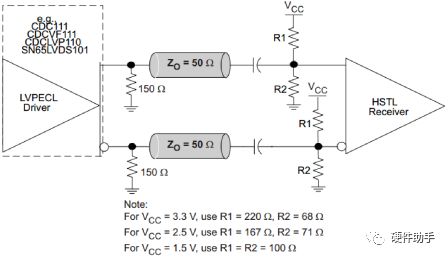

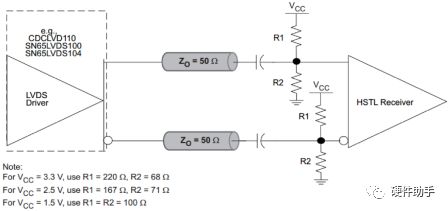

3、LVPECL到HSTL的连接

150Ω电阻用作LVPECL输出的直流偏置(VCC-1.3V),也提供了一个源电流的直流通路。在HSTL接收端,R1和R2被用作戴维南端接,阻抗为50Ω(R1//R2),同时也设定了共模电压(VCM=0.75V)。

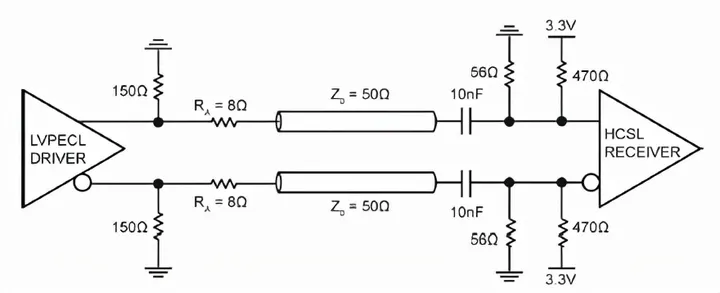

4、LVPECL到HCSL的连接

在LVPECL驱动器输出端向GND放置一个150Ω电阻对于开路发射极提供直流偏置以及到GND的直流电流路径至关重要。为了将800mV的LVPECL摆幅衰减到700mV的HCSL摆幅时,必须在150Ω电阻之后放置一个衰减电阻(RA =8Ω)。应在HCSL接收器前面放置一个10nF交流耦合电容,以阻止来自LVPECL驱动器的直流电平。放置交流耦合电容后,HCSL输入需要重新偏置,可以通过将470Ω电阻连接3.3V和56Ω电阻到GND上来实现HCSL接收机输入共模的350 mV直流电平。

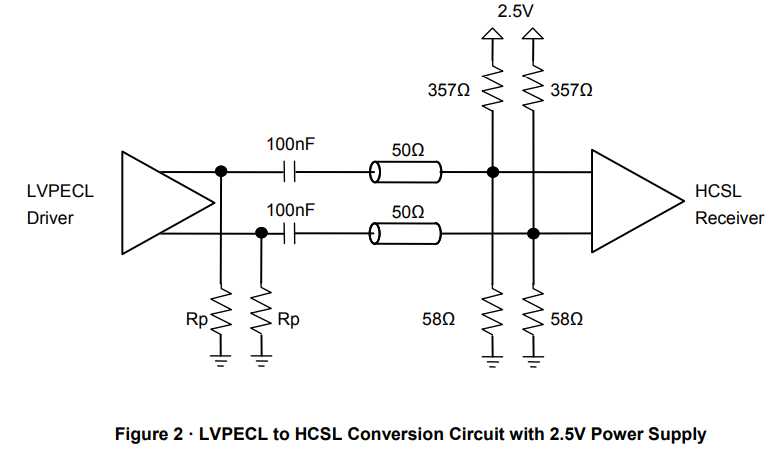

终端电路连接到2.5V电源的情况下,357 Q电阻器与58Q电阻器并联提供一个50Q端接电阻来匹配50Q传输线。由357 Q电阻串联而成的分压器将接收器的直流偏置点设置为0.35V,如上图所示,Rp是LVPECL驱动器推荐的下拉电阻。对于带有3.3V电源Microsemi厂家的clock buffer,RP为120 Q。对于2.5V电源Microsemi厂家的clock buffer,RP为60Q。

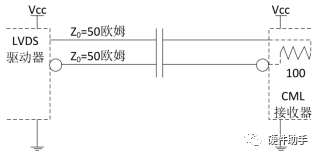

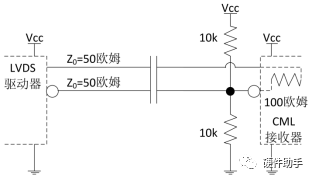

5、LVDS到CML的连接

一般情况下,不会存在LVDS与CML之间的对接,因为CML电平一般用在高速信号,如2.5G/10G等场合。而LVDS一般很难用在那么高的速率。

通常情况下,建议LVDS驱动CML时采用交流耦合。确保输出的交流幅度是否落在输入交流幅度之内。

CML一般都内置了匹配电阻。如果CML的输入没有直流偏置,则需要2个10K电阻。

LVDS输出通过100Ω电阻终端驱动±3.5mA电流,在CML接收器前面产生350mV摆幅电平。因为CML的标准摆幅是400mV,所以CML接收器能够接收350mV摆幅电平。此外,还必须确认CML接收器输入内部的自偏置。如果CML输入端的自偏置不存在,则必须在PCB上放置一个50Ω的电阻到VCC,用于CML偏置和传输线端接。

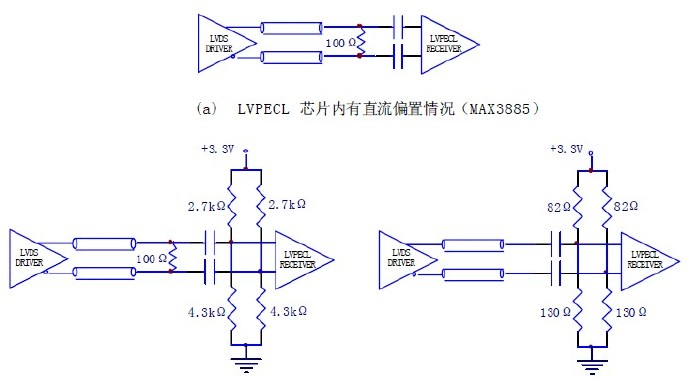

6、LVDS到LVPECL的连接

LVDS的输出幅度比较小,如果后端LVPECL的输入能够接受才可以连接,否则要加转换芯片。

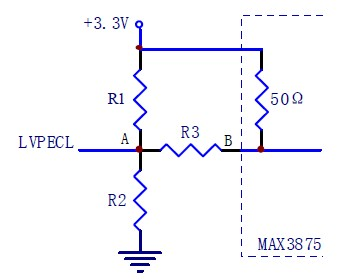

6.1、直流耦合

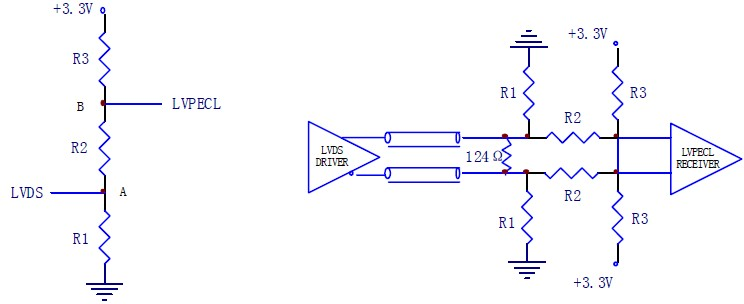

LVDS到LVPECL的直流耦合结构中需要加一个电阻网络,该电阻网络完成直流电平的转换。LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V。LVDS的输出是以地为基准,而LVPECL的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS的输出电位不应对供电电源敏感;另一个问题是需要在功耗和速度方面折中考虑,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS的输出性能容易受电源的波动影响;还有一个问题就是要考虑电阻网络与传输线的匹配。

电阻值可以通过下面的方程导出。

图、 LVDS到LVPECL直流耦合方式

要完成LVDS到LVPECL的逻辑转换,需要满足如下方程式:

在Vcc 电压为3.3V 时,解上面的方程得:R1=374Ω,R2=249Ω,R3=402Ω,VA=1.2V,VB=2.0V,RIN=49Ω,Gain=0.62。

LVDS 的最小差分输出信号摆幅为500mV,在上面结构中加到LVPECL 输入端的信号摆幅变为310mV,该幅度低于LVPECL 的输入标准,但对于绝大多数MAXIM 公司的LVPECL 电路来说,该信号幅度是足够的,原因是MAXIM 公司LVPECL 输入端有较高的增益。

如图所示,设计该网络时需考虑:

1.LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V;

2.LVDS的输出是以地为基准,而LVPECL的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS的输出电位不应对供电电源敏感;

3.需要折中考虑功耗和速度,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS的输出性能容易受电源的波动影响;

4.考虑电阻网络与传输线的阻抗匹配问题;

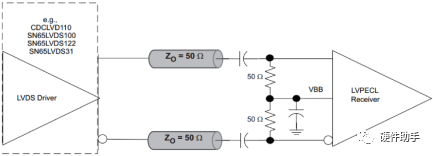

6.2、交流耦合

接收端电阻网络中间接入一电容到地,这样可以消除差分线上的共模噪声。

(b)LVPECL 芯片内没有直流偏置情况(MAX3867)

交流耦合

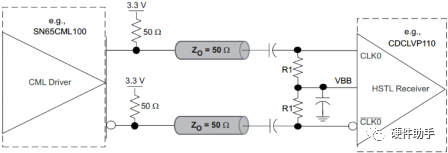

7、LVDS到HSTL的连接

CML和HSTL的互连推荐采用交流耦合。

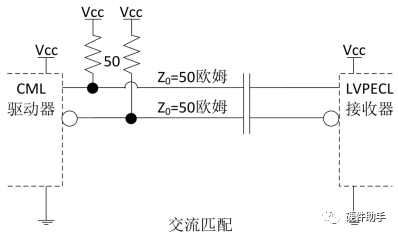

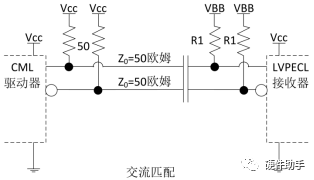

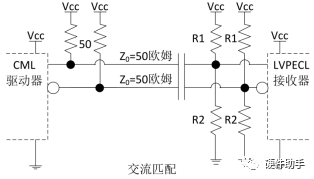

8、CML到LVPEL的连接

通常情况下,建议CML驱动LVPECL时采用交流耦合,不采用直流匹配。

8.1、50欧姆上拉匹配

如果LVPECL接收器的输入带有偏置,则可以通过电容直连。CML输出上拉50欧姆作为直流偏置。

8.2、50欧姆上拉+偏置

如果LVPECL接收器的输入不带有偏置,则需要用外部电阻提供偏置电压。

推荐使用的交流匹配方式如下:

9、CML到LVDS的连接

9.1、直流耦合

LVDS的输入侧支持1.25±1V的直流电平,如果CML的输出在这个范围内则可以直接连接。

9.2、交流耦合

如果LVDS输入内置直流偏置则如图连接。

如果LVDS输入没有内置直流偏置则需要增加直流偏置。

一般情况下,在光传输系统中没有CML和LVDS 的互连问题,因为LVDS 通常用作并联数据的传输,数据速率为155MHz,622MHz或1.25GHz,而CML 常用来做串行数据的传输,数据速率为2.5GHz 或10GHz。需注意CML 的输出信号摆幅应落在LVDS 的有效工作范围内。

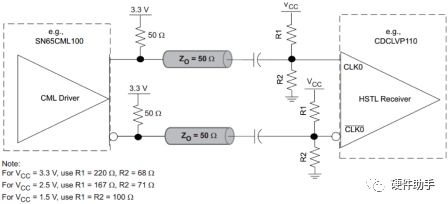

10、CML到HSTL的连接

CML和HSTL的互连推荐采用交流耦合。

11、HCSL到LVDS的转换

在图中,每个HCSL输出引脚在0和14mA之间切换。当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为48Ω,与50Ω并联,相当于23.11Ω。LVDS输入的摆幅为14mAx23.11Ω= 323mV。

应在LVDS接收器前放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。放置交流耦合电容后,LVDS输入需要重新偏置,可以通过将一个8.7KΩ电阻连接到3.3V和5KΩ电阻连接到GND来实现LVDS接收器输入共模的1.2V直流电平。如果LVDS接收器差分输入引脚上已经存在有100Ω电阻,则不需要外部100Ω电阻。

12、HCSL到CML的转换

在图中,每个HCSL输出引脚在0和14mA之间切换, 当一个输出引脚为低电平(0)时,另一个为高电平(驱动14mA)。HCSL驱动器的等效负载电阻为68Ω,与50Ω电阻并联,相当28.81Ω。CML输入的摆幅为14mAx28.81Ω= 403mV。

应在CML接收器前面放置一个10nF交流耦合电容,以阻止来自HCSL驱动器的直流电平。另外,必须确认CML接收器输入内部的自偏置。如果没有CML输入端的自偏置,则必须在CML偏置和传输线端接的PCB上放置一个50Ω的端接电阻到VCC。

如何选择交流耦合电容

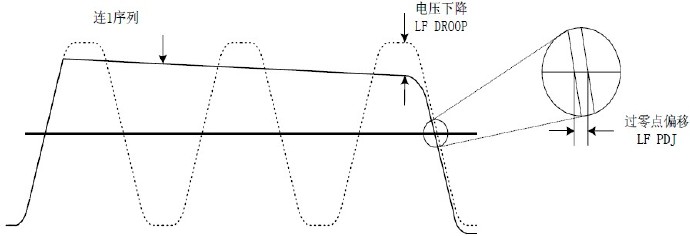

当利用交流耦合结构时,耦合电容的选取应特别小心,该电容与负载阻抗一起构成高通滤波结构,非归零的连0 或连1 出现时,电容会造成接收端电压下降,过零点偏移,通过下面的图形可以很好地理解这一点。

交流耦合造成低频分量损失,过零点漂移

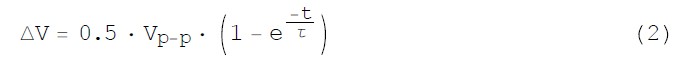

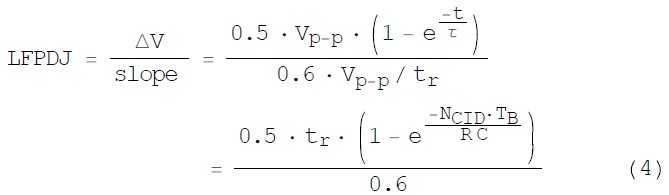

为防止连零和连1 序列造成负载电压有较大下降,我们可以把耦合电容与负载组成的高通网络的3dB 转角频率降低,下面主要从时域对此进行分析,我们知道一级高通RC 网络的时域响应为:

![]()

NRZ 数据信号经过电容耦合至50Ω的负载上,信号这时的摆动则以0 为基准。我们把信号幅度以VP-P进行归一化处理,电压幅度归一化为±0.5VP-P。假定负载最初充电电压为V0+=0.5VP-P,最终电压为V∞=0。τ为HPF 的时常数,则经过一段时间t 后,负载电压下降ΔV为:

如允许在时间t 时,功率下降0.25dB,则ΔV/ VP-P = 6%;

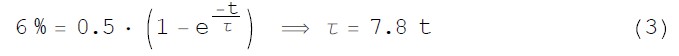

如果我们定义TB为数据每比特周期,NCID为最大容许的连零或连1 数目,负载阻抗R=50 Ω,C 为耦合电容,则t=NCID·TB,τ=R·C,C 可通过下面式子估算:

![]()

我们以2.488Gbps 的系统为例,TB = 400ps,NCID = 100bit,通过计算得C =6.2nF。下面计算该电容造成的过零点偏移大小:

tr在这里指NRZ 信号幅度从20%到80%的上升时间,一般可通过下式估算:

![]()

BW 指系统带宽,通常为0.6~1 倍数据速率,对于2.5Gbps 系统,如果取tr=120ps,C=6.2nF,计算得LFPDJ等于13ps,如果把C 增加到100nF,这时LFPDJ将小于1ps,可以忽略不计。

偏置和终端电路

1.偏置

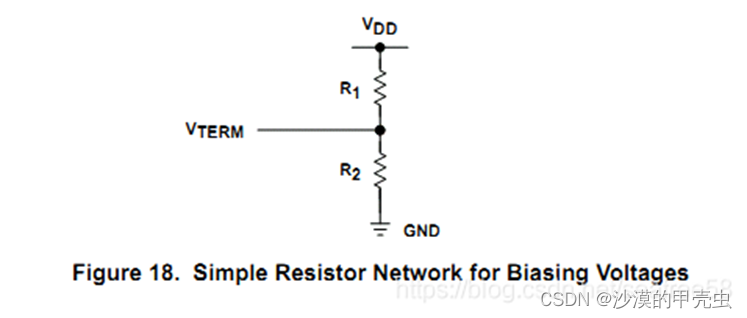

最简单的偏置电压使用分压电阻网络即可。

举个LVPECL的例子,3.3V的LVPECL的偏置电压为2V,所以:3.3*(R2/(R1+R2))=2

可以根据这个算式,算出R1与R2的关系,R1=0.65R2

2.终端匹配

对于差分电路,有四种典型的终端和偏置方式,他们有各自的优缺点。

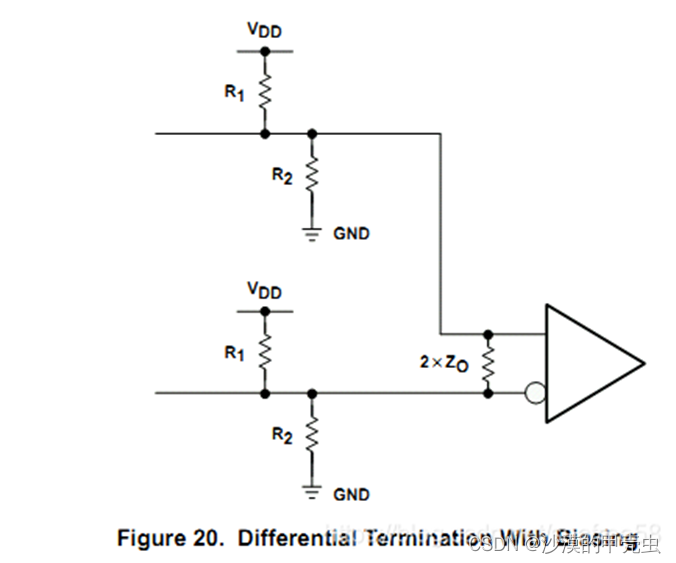

2.1.差分匹配

这是最简单的一种,R1和R2用以分压,他们的值在k级别,使得输入共模电平在接收端允许的范围。

该方式的主要的缺点是元器件的数量以及电源的消耗通过分压网络。然而,这种方式可以通过选择更大阻值的R1,R2来降低功耗。

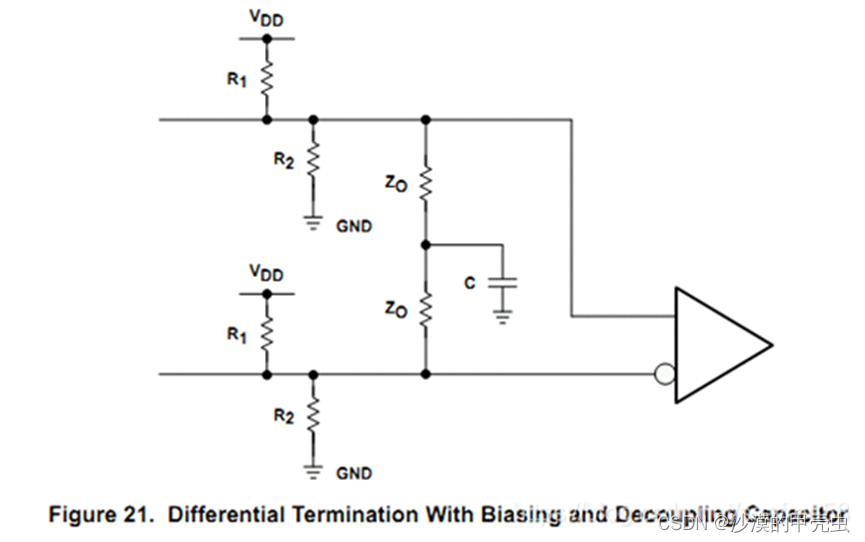

2.2.带有去耦电容的差分匹配

第二种方法是和第一种很相似,但终端匹配电阻采用50欧姆,且两个匹配电阻间通过一个去耦电容接地。

这种差分匹配,主要的缺点在于元器件数量和电源消耗;然而,电源消耗可以通过调整R1,R2的值。优点在于,当出现传输线造成的信号歪斜时,比如差分信号并不是同时到达时,该电容可以成为一个对小信号的低阻对地路径。

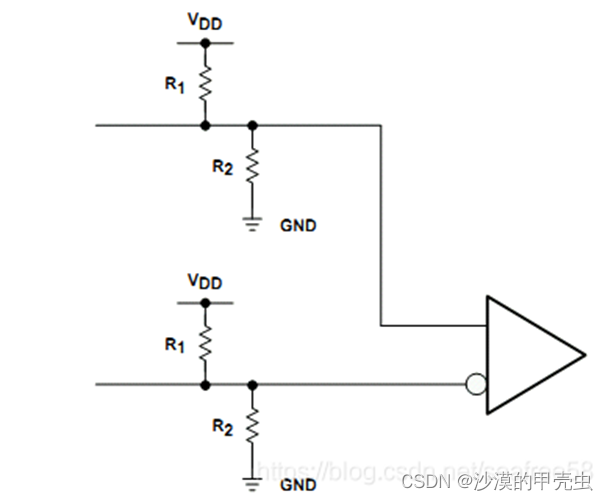

2.3.简化电路

第三种方法如下图

理想的配置是使得R1||R2等于Z0。同时满足电阻分压。

可以继续举LVPECL的例子。

算得R1||R2 = 50 又根据上文的关系,可得,R1=82,R2=130

显然,在这个例子里,有更少的R1和R2,但是由于R1和R2的电阻较小,所以功耗比较大。

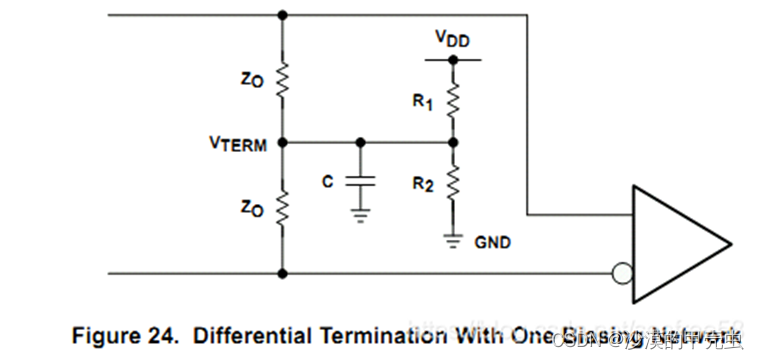

2.4.带一个偏置电阻网络的差分匹配

最后一种方式将偏置网络合并为一个,如图

这是一个非常简洁的电路,易于只存在一个分压网络用于两个差分线,减少了电源消耗。去耦电容和匹配电阻消减了电路噪声,和信号歪斜。

当芯片不存在内部的偏置电路时,这种方法是最好的终端和偏置电路之一。

R1和R2在k级的电阻中选,Z0等于传输阻抗。

这种配置时,匹配电阻靠近芯片摆放,偏置电路远离该部分。去耦电容同样必须靠近芯片摆放。

)

的题解)

:客户端接口(一)之 libpq - C 库)

)