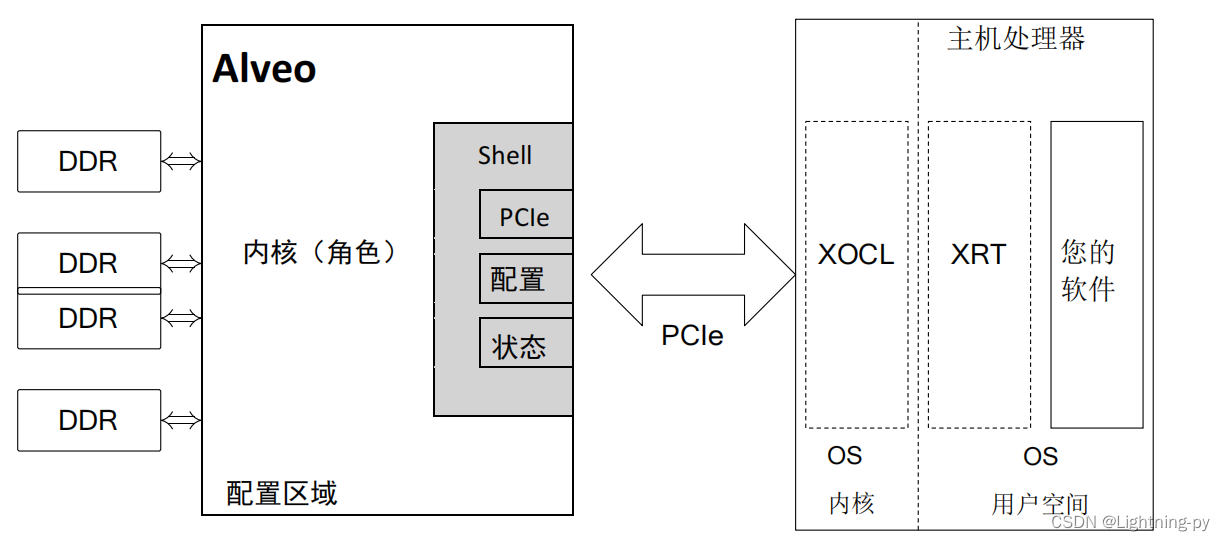

在 Alveo 加速卡中,涉及到的概念拓扑结构主要包括 Alveo 卡上的各个关键组件以及与主机系统之间的通信结构。以下是对这些概念拓扑结构的简要介绍:

1.DDR

即双数据率内存(Double Data Rate memory),是一种常见的计算机内存类型,用于存储和提供处理器所需的数据和指令。DDR 内存与传统的SDR(Single Data Rate)内存相比,在同样的工作频率下,可以实现双倍的数据传输速率,因此在相同频率下 DDR 内存的传输速度是SDR 内存的两倍,这也是“双数据率”名称的由来。DDR 内存已经成为了现代计算机系统中最常见的内存类型之一。

在 FPGA 加速卡中,DDR 内存通常被用来存储需要进行高速处理的数据、指令,以及加速应用程序的中间结果等。通过将数据存储在DDR 内存中,FPGA 加速卡可以更快地获取和处理数据,从而提高数据处理效率和性能。

对于 FPGA 加速应用程序开发者来说,合理地利用和管理DDR 内存是非常重要的。开发者需要考虑如何将数据有效地存储在DDR 内存中,如何通过FPGA 设备与DDR 内存进行高效的数据交互,以及如何通过合理的数据流设计和管道优化来最大程度地发挥DDR 内存的性能优势。

2.Alveo

- Shell(外壳):Shell 是 Alveo 加速卡上的外围逻辑,用于管理 PCIe 数据传输、配置 FPGA 设备以及监控设备状态等功能。通过 Shell,用户可以与 FPGA

![macos m1 arm芯片 使用jpype报错 FileNotFoundError: [Errno 2] JVM DLL not found](http://pic.xiahunao.cn/macos m1 arm芯片 使用jpype报错 FileNotFoundError: [Errno 2] JVM DLL not found)

文件转换为HTML)

)

正式更名枢纽云)

)