文章目录

- 本篇概要

- Vivado Vitis 环境搭建

- Vivado 免费标准版 vs 企业版

- Vivado Windows 安装

- Vivado 安装更新

- Vivado 工程操作

- GUI 创建工程

- 打开已有工程

- 从已有工程创建, 重命名工程

- GUI导出TCL, TCL复原工程

- TCL命令

- Vivado 版本控制

- Blink

- Tcl脚本新建导出重建工程

- 纯Verilog Blink

- Tcl脚本生成位流文件

- Tcl脚本编程运行

- MicroBlaze 简介

- MicroBlaze 软核点灯

- Vivado IP 连线

- Vitis 2023.2 代码编写

- Vitis HLS 自定义IP Blink

- Vitis HLS 2023.2 GUI操作

- Vivado 使用自定义IP

- HLS自定义IP含AXI接口连接MicroBlaze

- Tcl脚本创建HLS工程 综合导出RTL 版本控制

- Vivado 连接自定义IP和MicroBlaze

- Vitis 2023.2 代码编写

本篇概要

- 首先是 Vivado Vitis 2023.2 版本的安装, 使用的是在线安装的方式, 演示使用的 Aritx-7, 所以免费的标准版是足够的

- Vivado 工程的创建, 打开, 从Xpr导出Tcl脚本, 从Tcl再次复原工程, 便于Git的版本控制

- Tcl命令可以实现类似Vivado GUI的效果, 给出了创建导出重建工程, 生成位流文件, 编程运行的脚本

- 用了4种方式来点灯, 纯Verilog, 基于MicroBlaze+GPIO的现有IP方式, HLS使用Cpp写自定义IP方式, HLS添加AXI接口接入MicroBlaze的纯Cpp开发方式.

Vivado Vitis 环境搭建

Vivado 免费标准版 vs 企业版

当前(2024-02-20)最新版本是Vivado 2023.2, 常用的如Artix-7使用免费的标准版即可, 来源

下面是支持的器件, 来源

| 类别 | 产品系列 | Vivado ML 标准版 | Vivado ML 企业版 |

|---|---|---|---|

| SoC | Versal | AI Core 系列自适应 SoC 无 AI Edge 系列自适应 SoC 无 Prime 系列自适应 SoC 无 Premium 系列自适应 SoC 无 HBM 系列自适应 SoC 无 | AI Core 系列自适应 SoC 所有 AI Edge 系列自适应 SoC 所有 Prime 系列自适应 SoC 所有 Premium 系列自适应 SoC 所有 HBM 系列自适应 SoC 所有 |

| Zynq | Zynq 7000 SoC XC7Z007S, XC7Z010, XC7Z012S, XC7Z014S, XC7Z015, XC7Z020, XC7Z030 Zynq UltraScale+ MPSoC XCZU1CG, XCZU1EG, XCZU2CG, XCZU2EG, XCZU3CG, XCZU3EG, XCZU3TCG, XCZU3TEG, XCZU4CG, XCZU4EG, XCZU4EV, XCZU5CG, XCZU5EG, XCZU5EV, XCZU7CG, XCZU7EG, and XCZU7EV Zynq UltraScale+ RFSoC 无 | Zynq 7000 SoC 所有 Zynq UltraScale+ MPSoC 所有 Zynq UltraScale+ RFSoC 所有 | |

| FPGA | Virtex™ | Virtex 7 FPGA 无 Virtex UltraScale FPGA 无 Virtex UltraScale+ FPGA 无 Virtex UltraScale+ HBM 无 Virtex UltraScale+ 58G 无 | Virtex 7 FPGA 所有 Virtex UltraScale FPGA 所有 Virtex UltraScale+ FPGA 所有 Virtex UltraScale+ HBM 所有 Virtex UltraScale+ 58G 所有 |

| Kintex™ | AMD Kintex 7 FPGA XC7K70T, XC7K160T Kintex UltraScale FPGA XCKU025, XCKU035 Kintex UltraScale+ FPGA XCKU025, XCKU035 | AMD Kintex 7 FPGA 所有 Kintex UltraScale FPGA 所有 Kintex UltraScale+ FPGA 所有 | |

| Artix™ | Artix 7 FPGA 所有 XC/XA Artix UltraScale+ FPGA 所有 XC/XA | Artix 7 FPGA 所有 Artix UltraScale+ FPGA 所有 | |

| Spartan™ | Spartan 7 FPGA 所有 XC/XA Spartan UltraScale+ FPGA 即将推出 | Spartan 7 FPGA 所有 Spartan UltraScale+ FPGA 即将推出 | |

| 加速器卡 | Alveo™ | Alveo 所有 | Alveo 所有 |

| SoC | Kria™ | Kria 所有 | Kria 所有 |

Vivado Windows 安装

步骤如下:

-

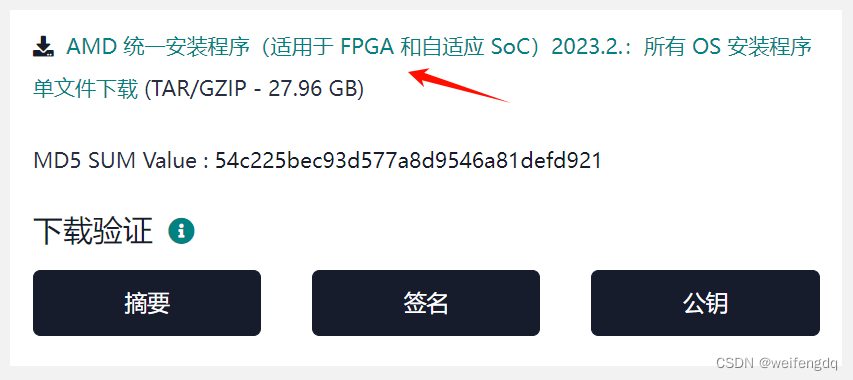

下载 (xilinx.com) 页面下载 AMD 统一安装程序(适用于 FPGA 和自适应 SoC)2023.2:Windows Self Extracting Web Installer (EXE - 203.13 MB)

-

点击后会提示登入AMD, 没有的注册一个

-

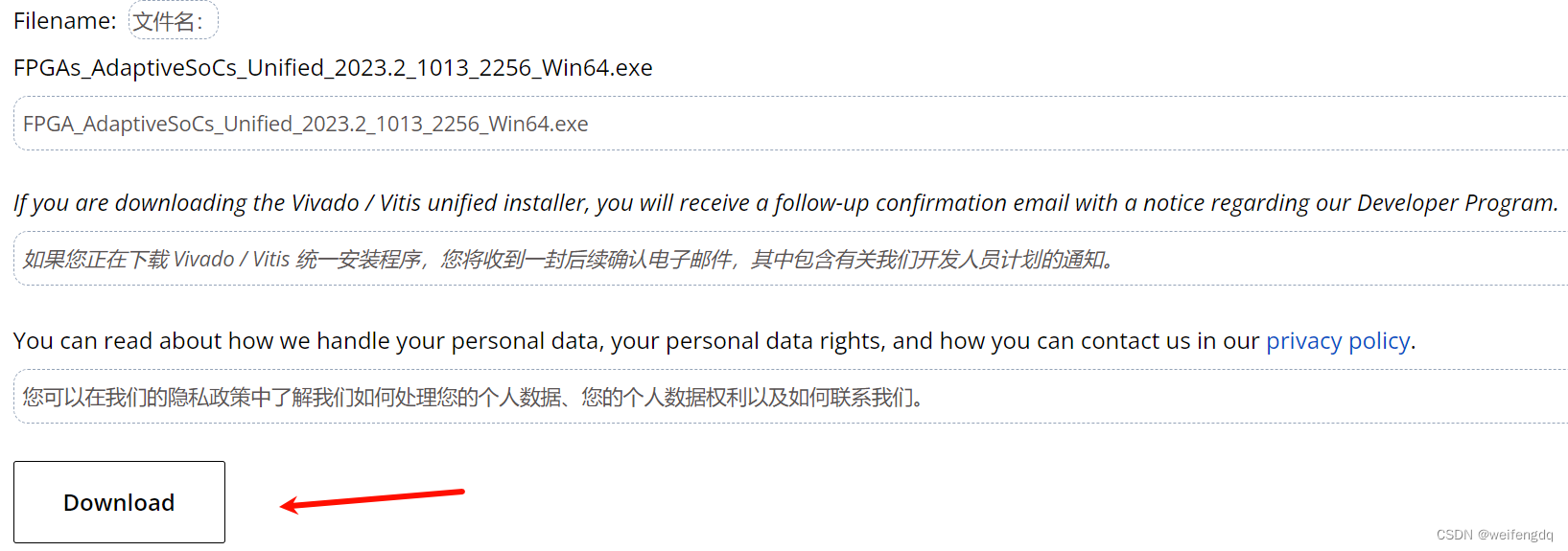

点击 Download 按钮

-

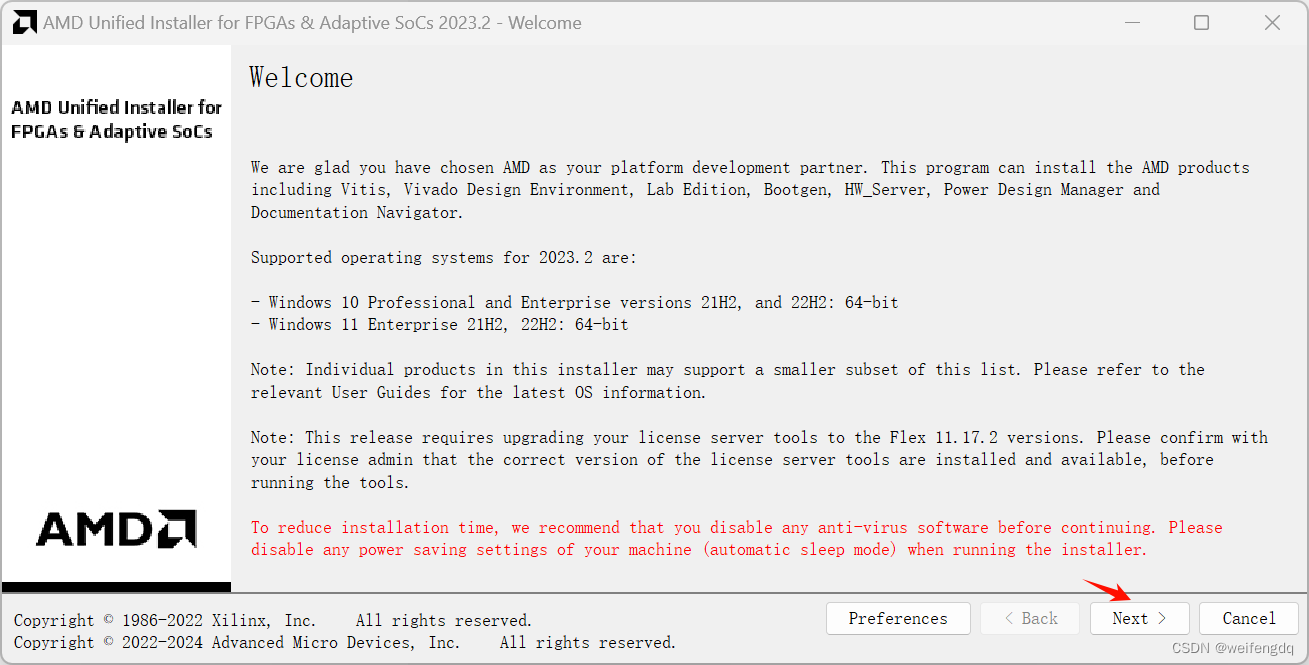

下载完后双击打开, 弹窗允许应用对设备更改

-

选 Next

-

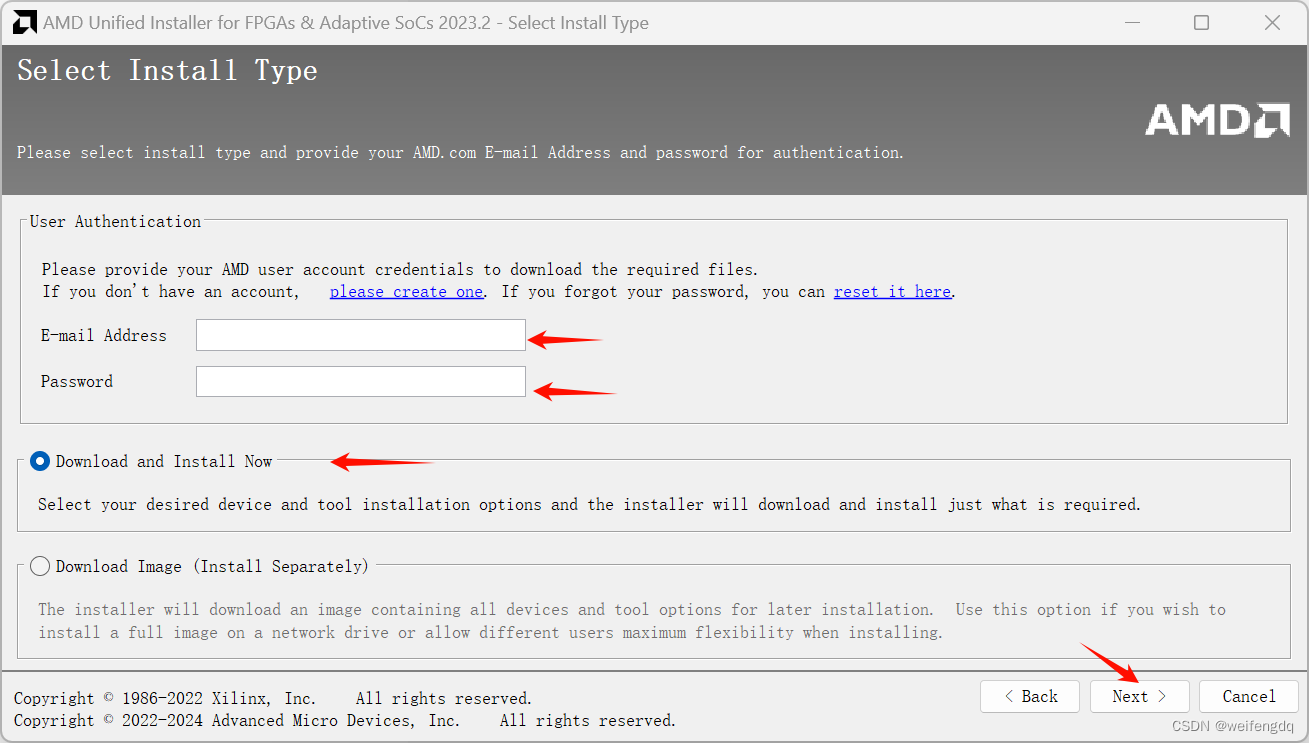

输入上面注册的AMD的邮箱和密码

-

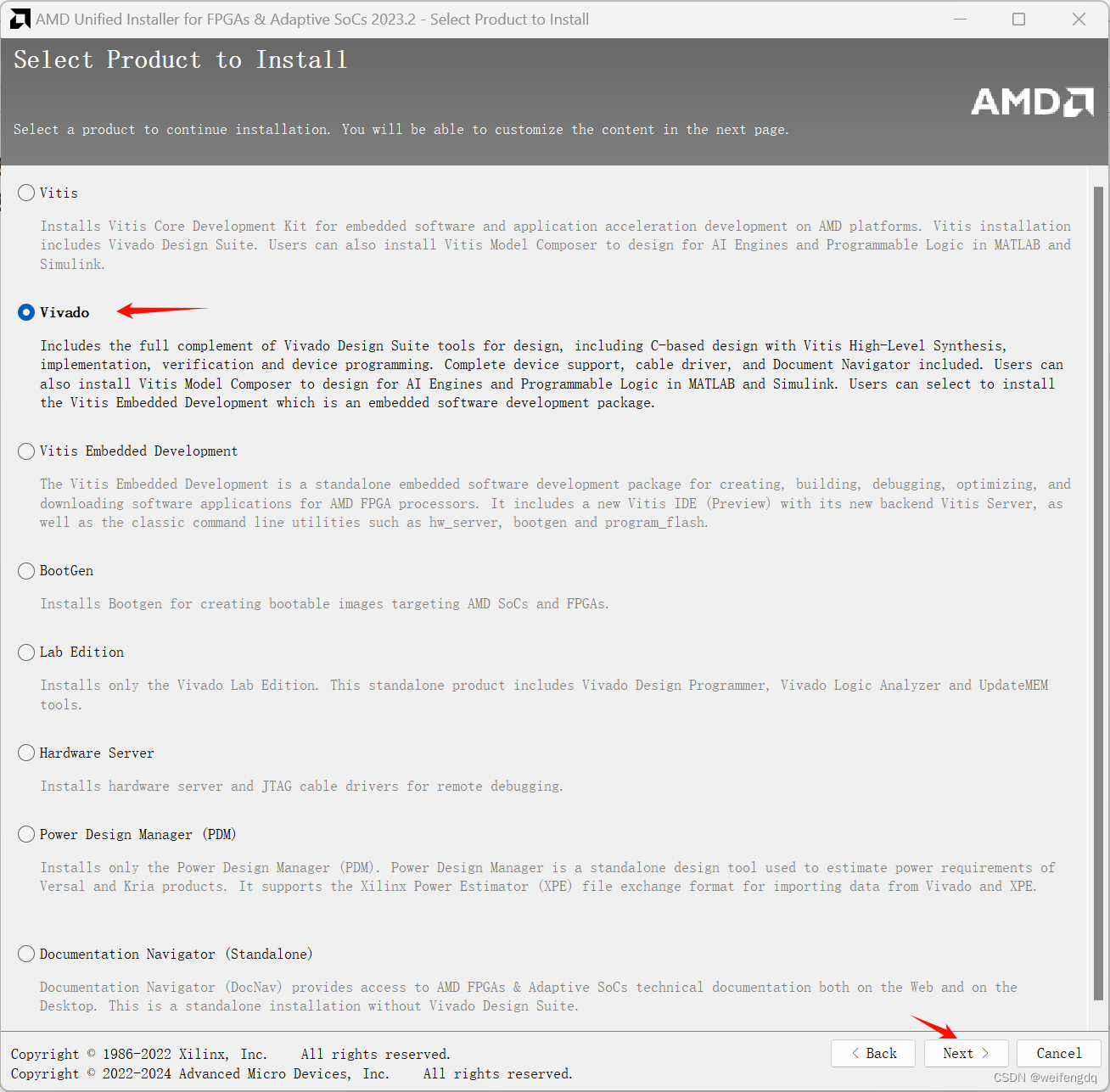

选 Vivado

-

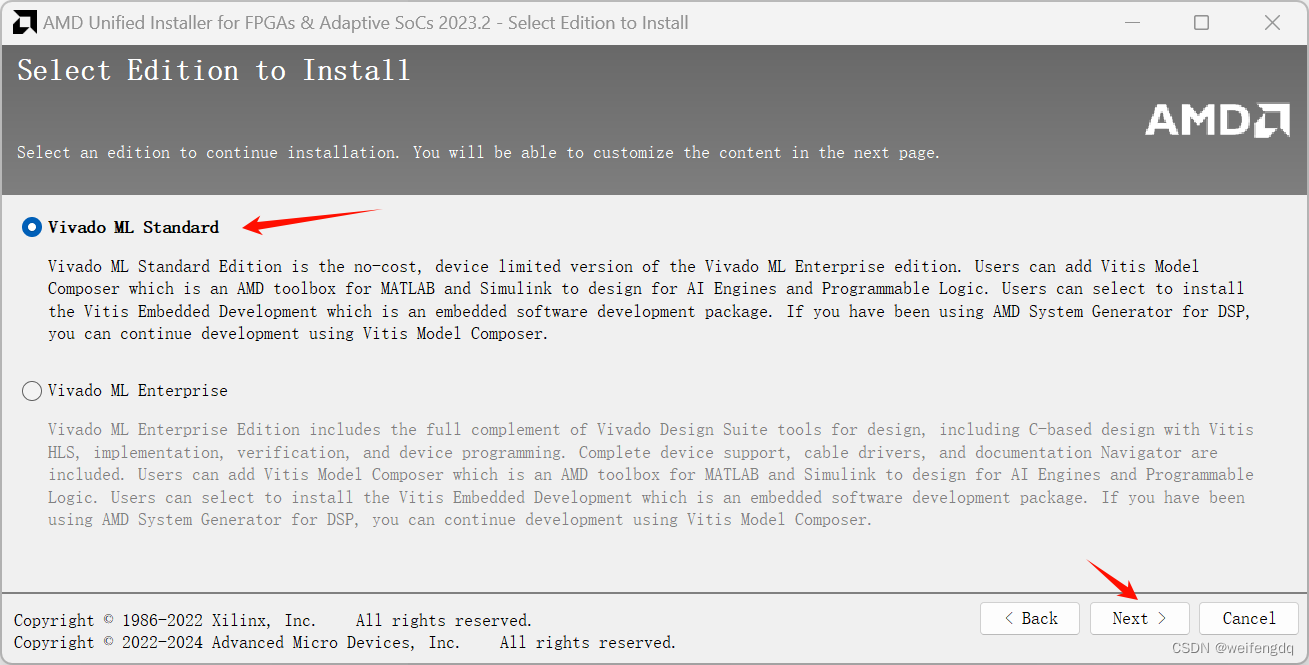

选免费的标准版

-

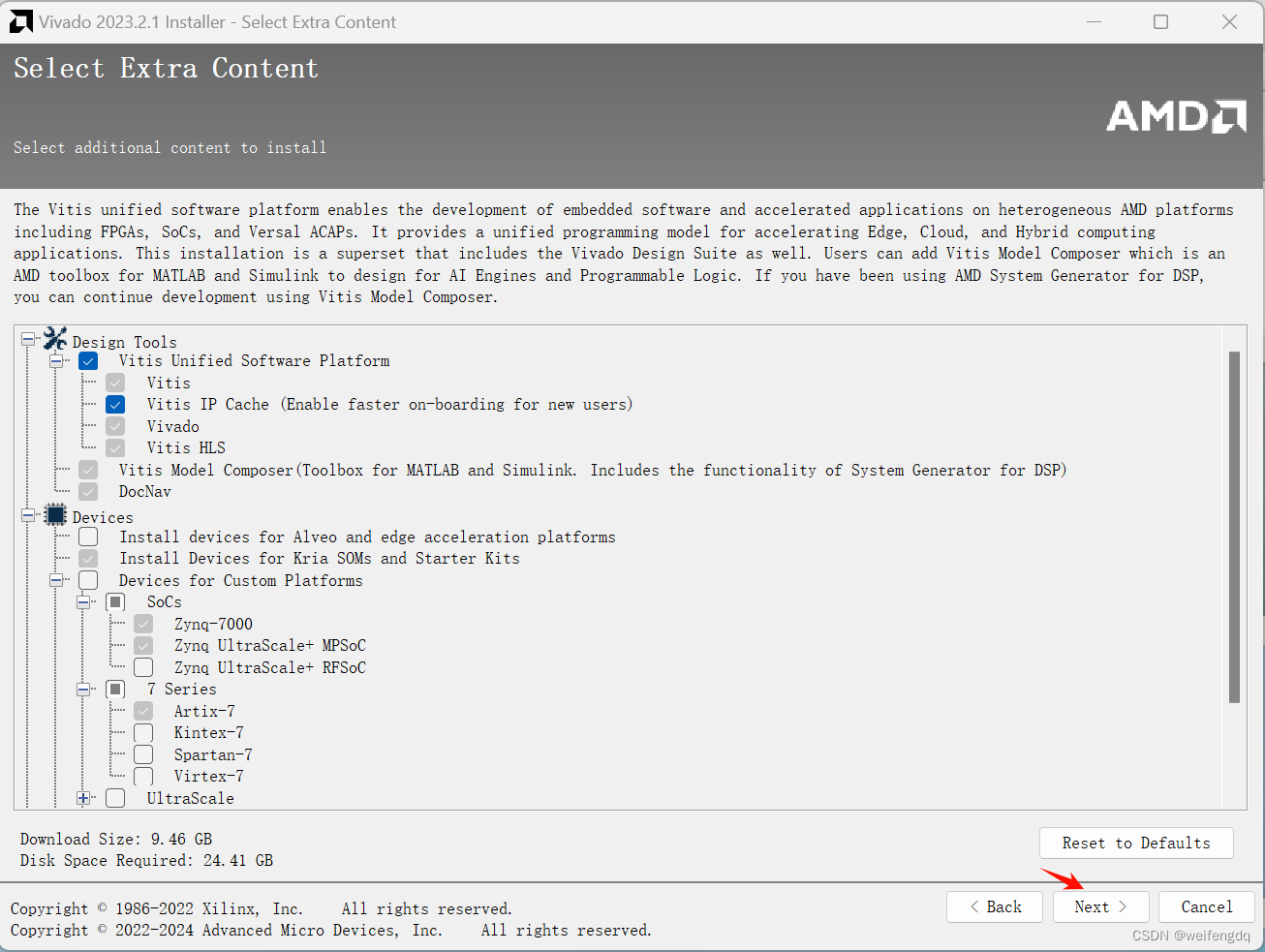

可能会用到的勾上, 用不上的可以先不装

-

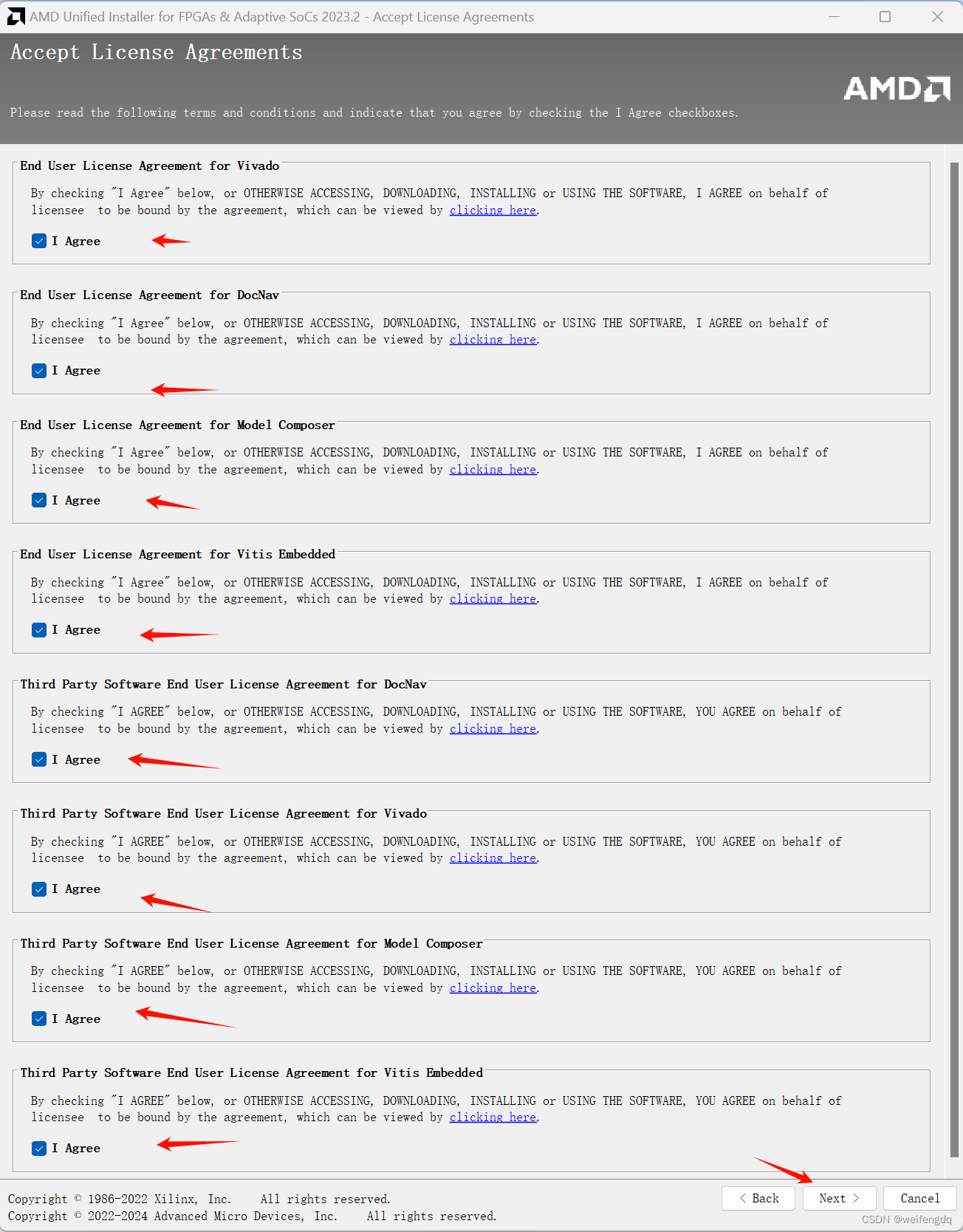

同意许可

-

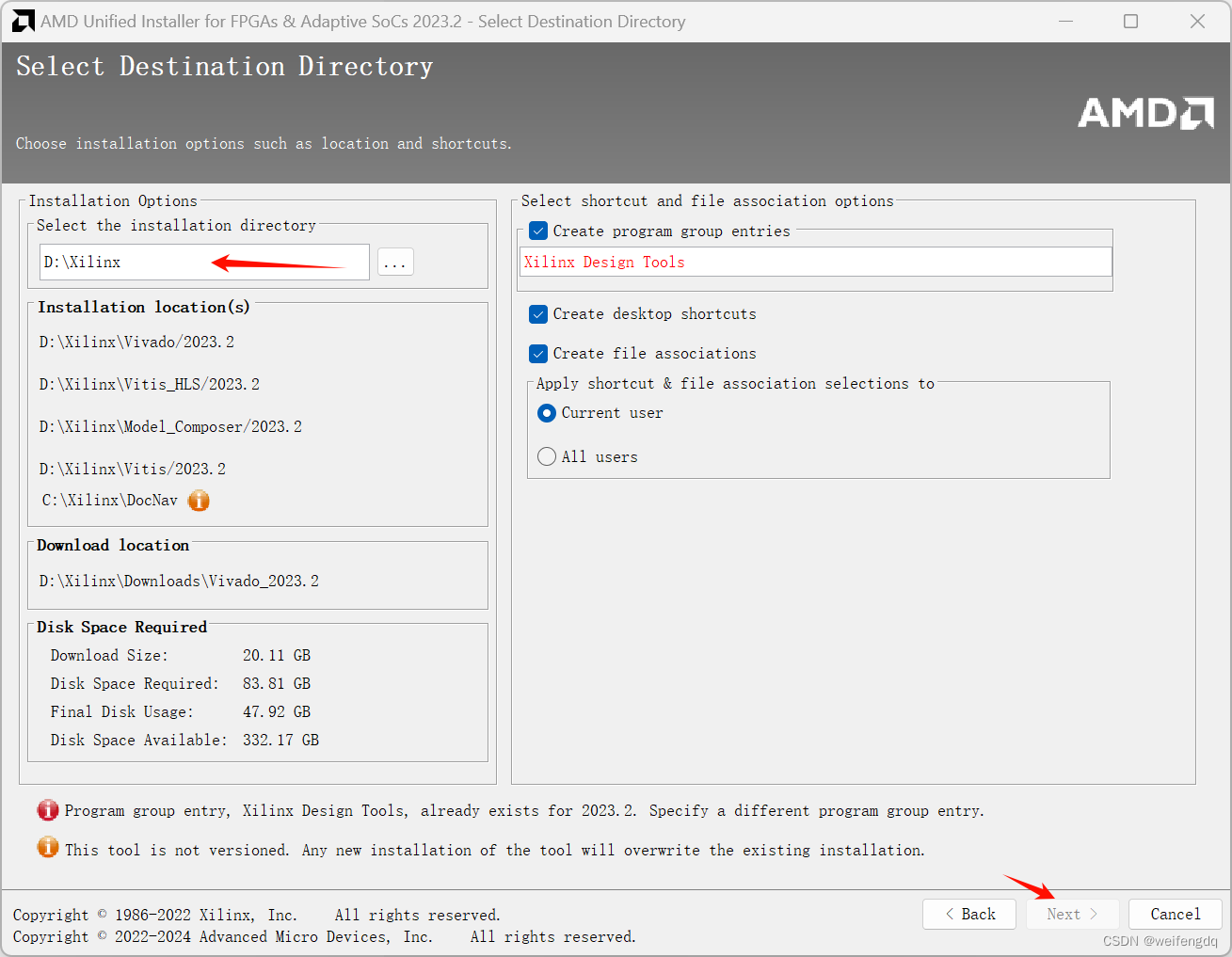

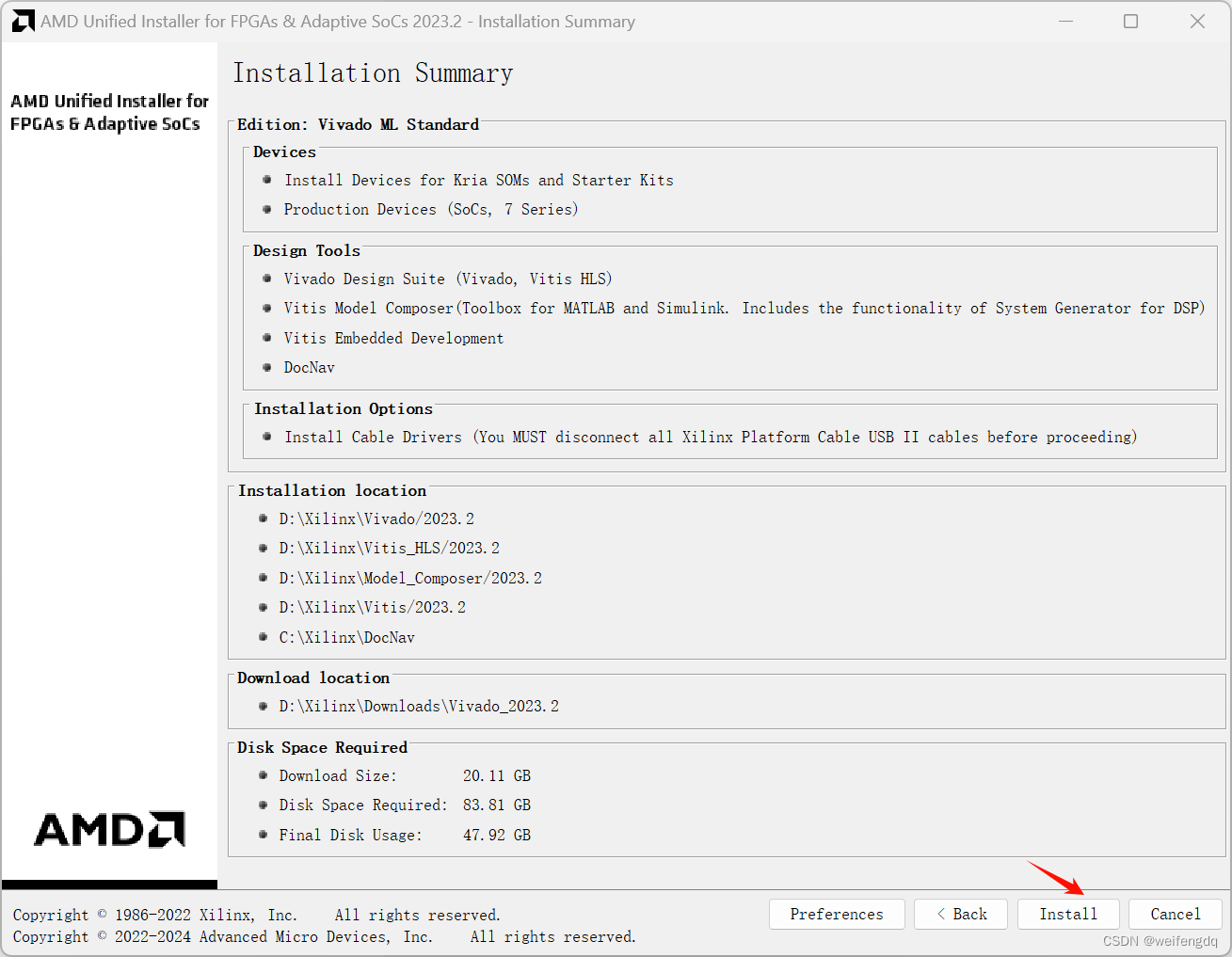

选择安装路径(图中D, 实际装了C)

-

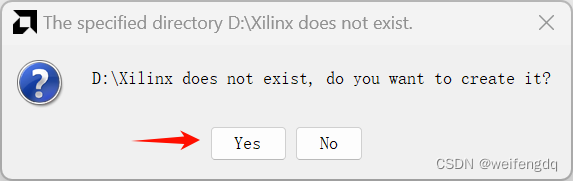

选 Yes 创建文件夹

-

安装

-

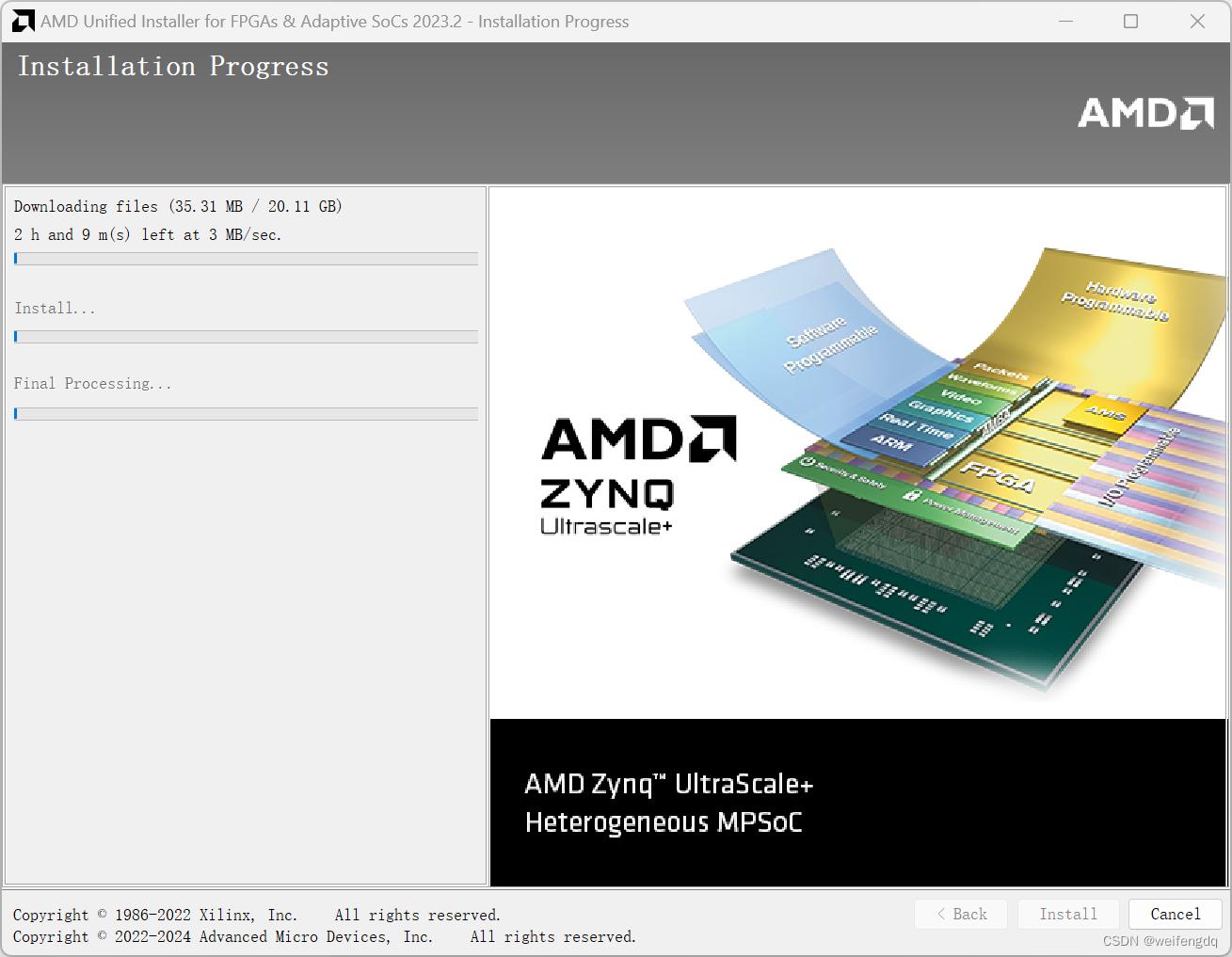

等下载和安装完就好了

-

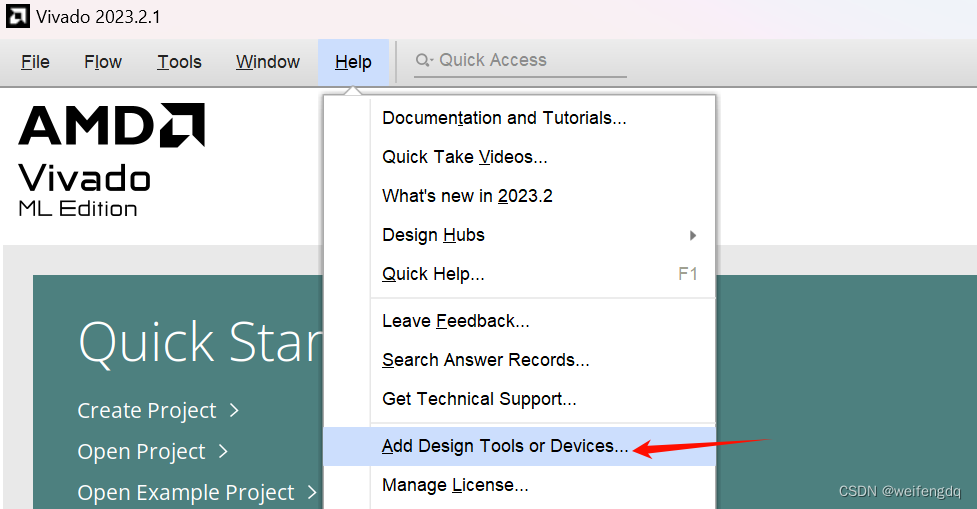

如果想安装更多的FPGA型号支持, 可以从Vivado的Help菜单栏中重新打开安装页面, 会自动弹出上面的Welcome页面

-

登入账户后可以 安装想要的型号

-

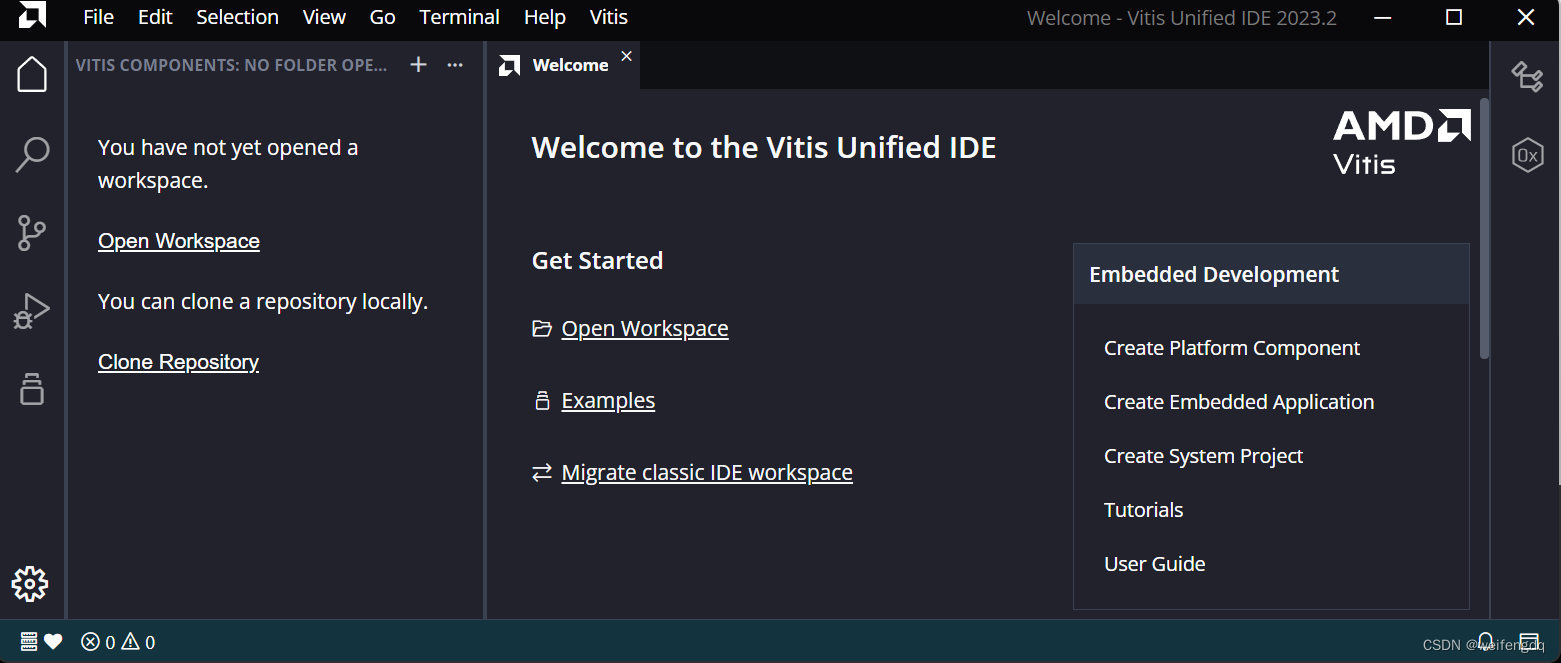

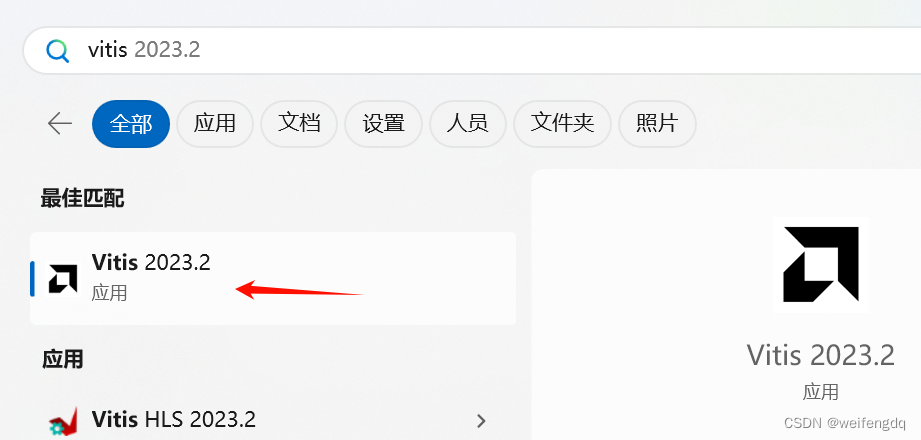

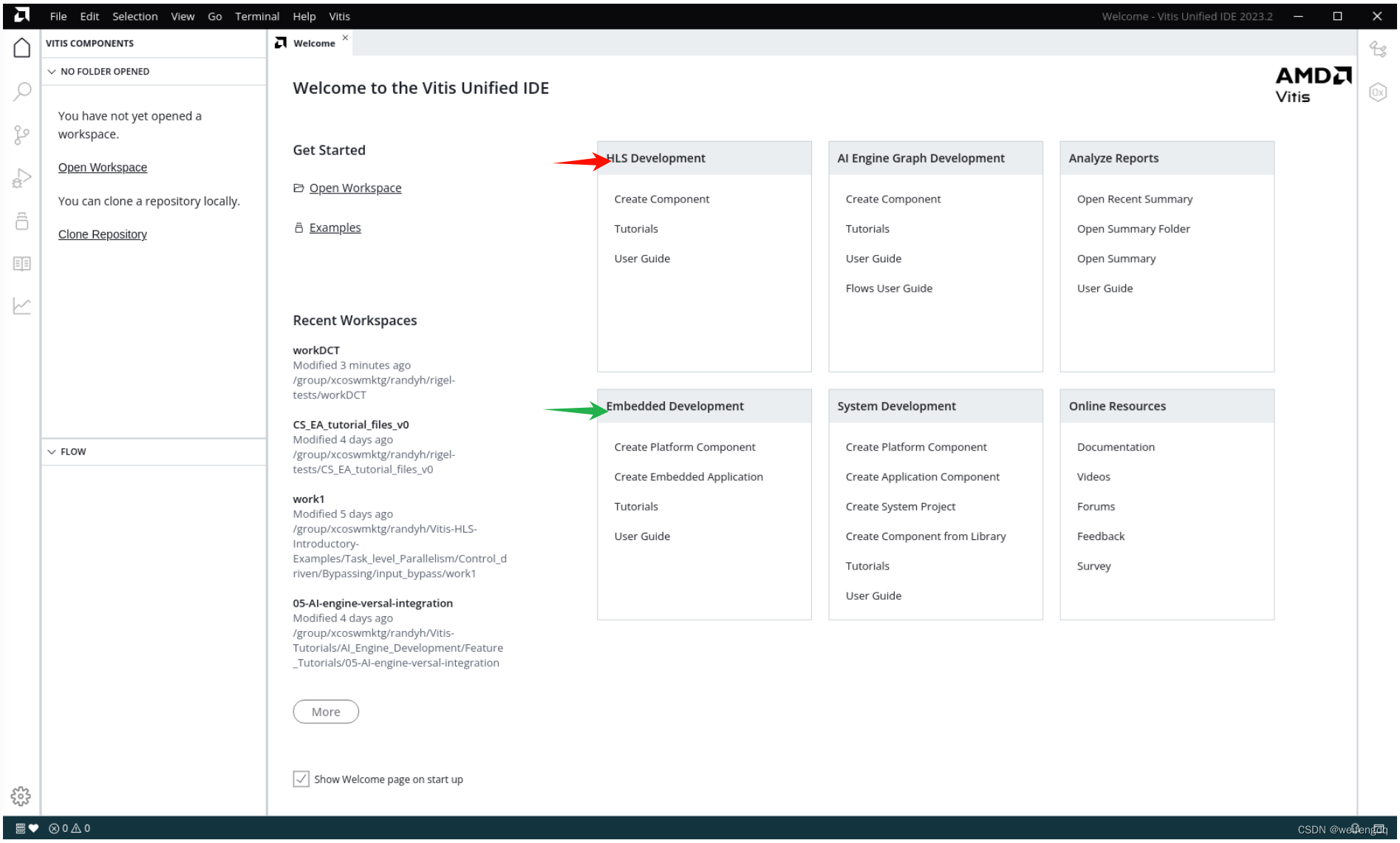

打开 Vitis 2023.2, 发现已经是 类 VSCode 页面了

-

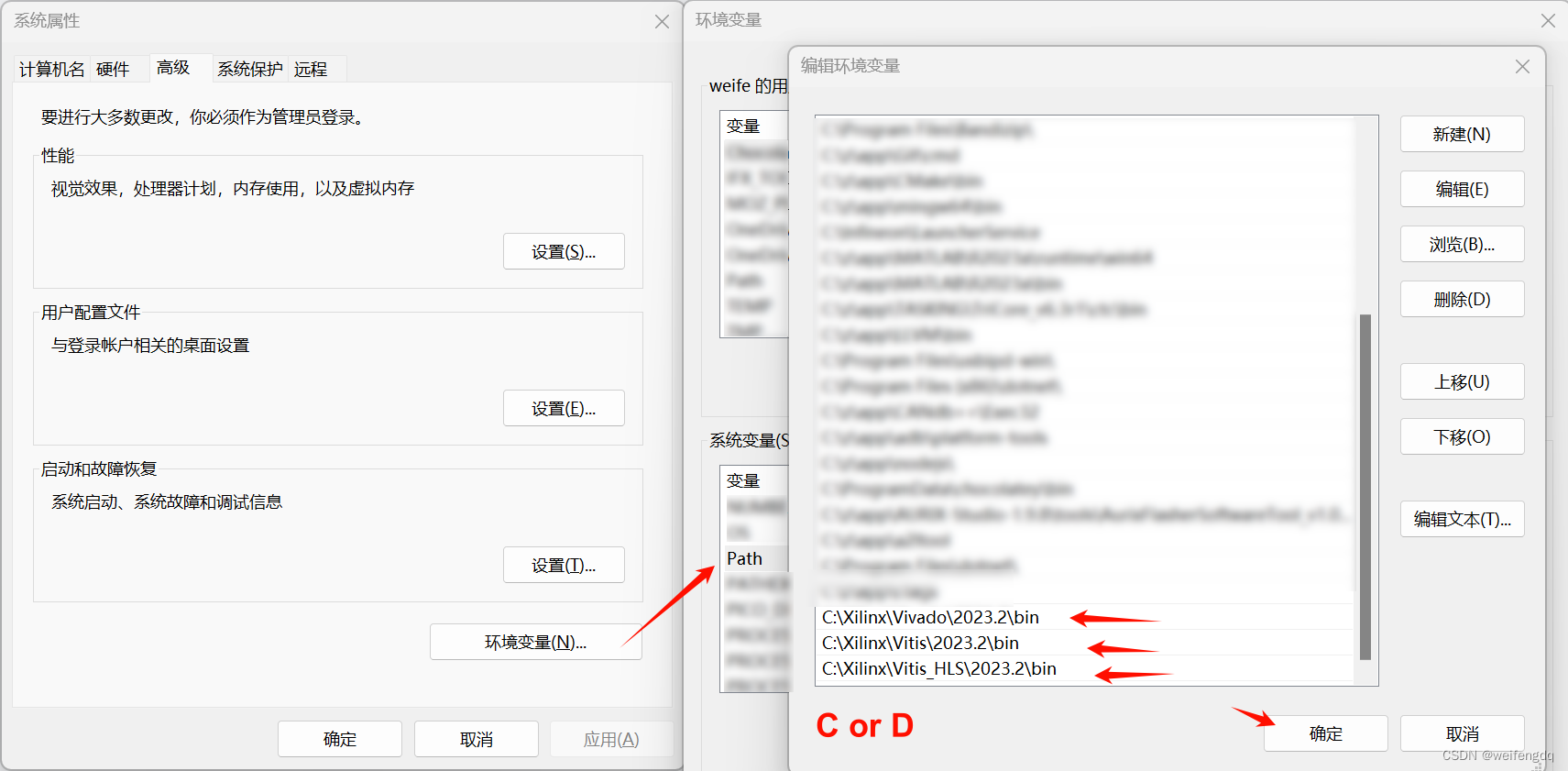

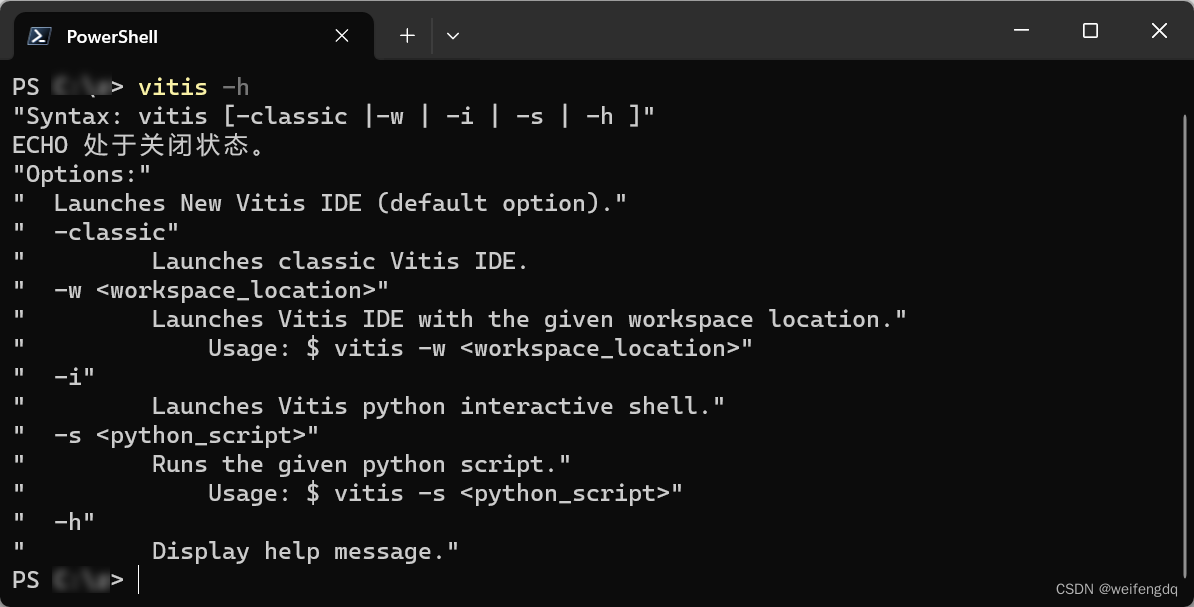

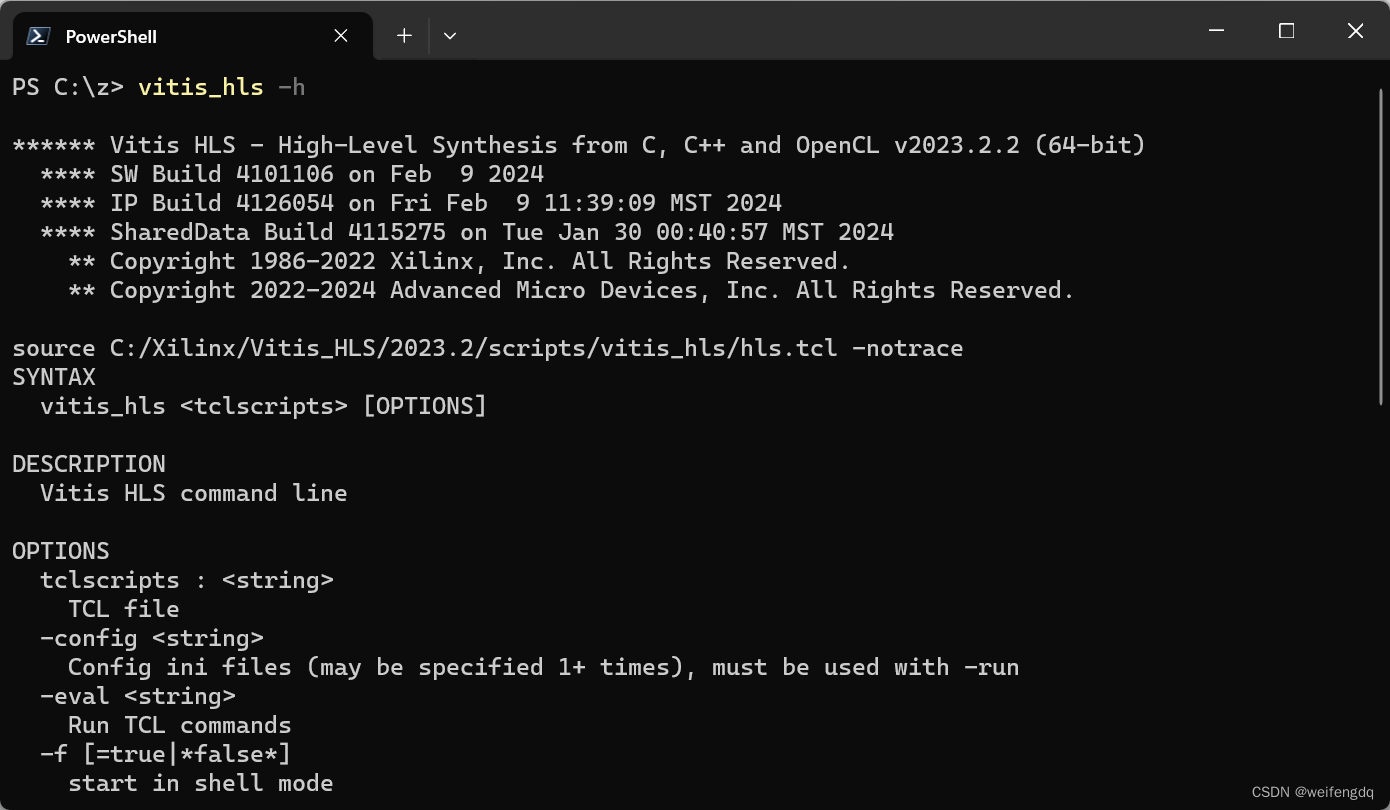

把 Vivado 和 Vitis, vitis_hls的安装路径填入系统环境变量

-

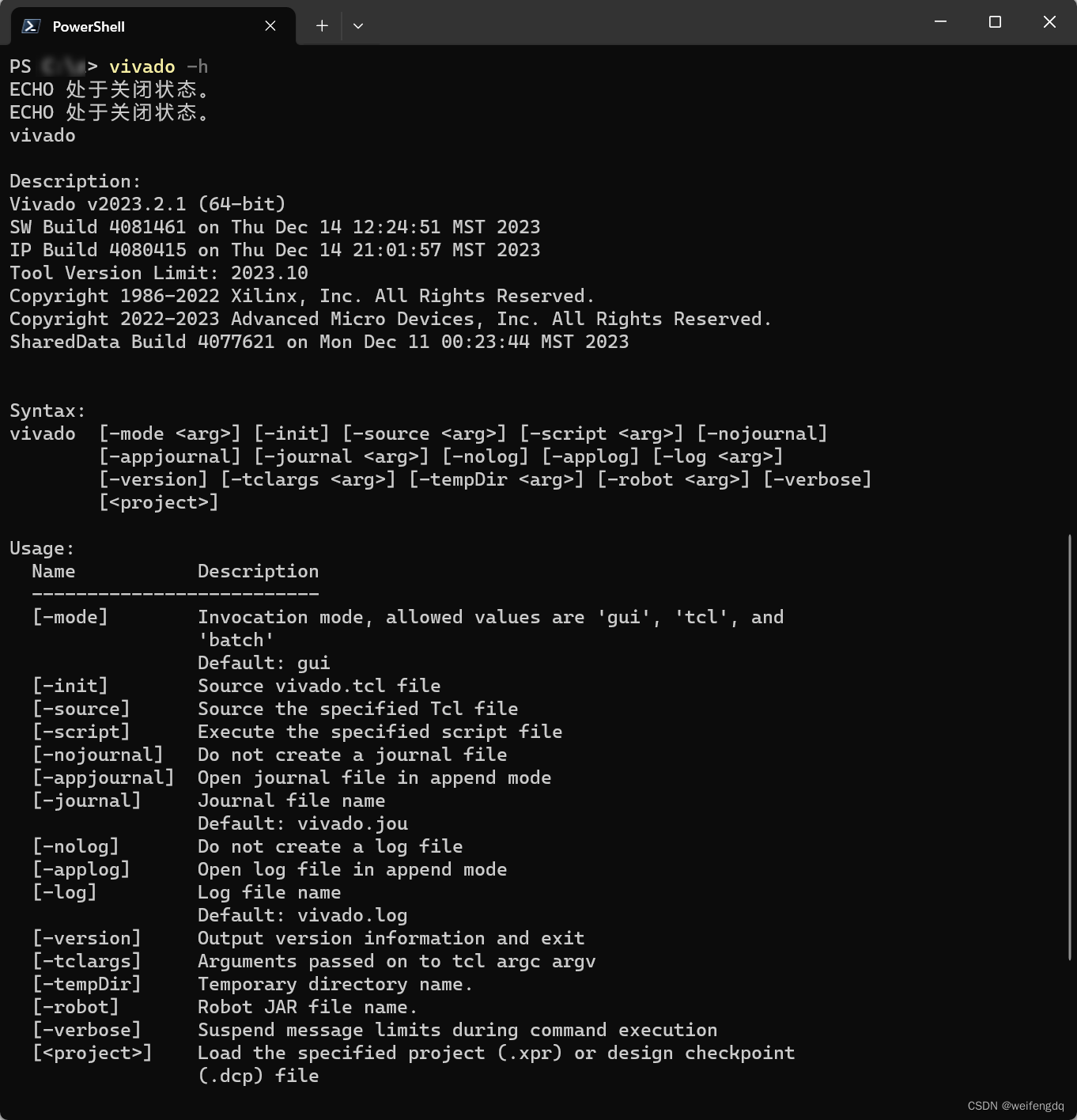

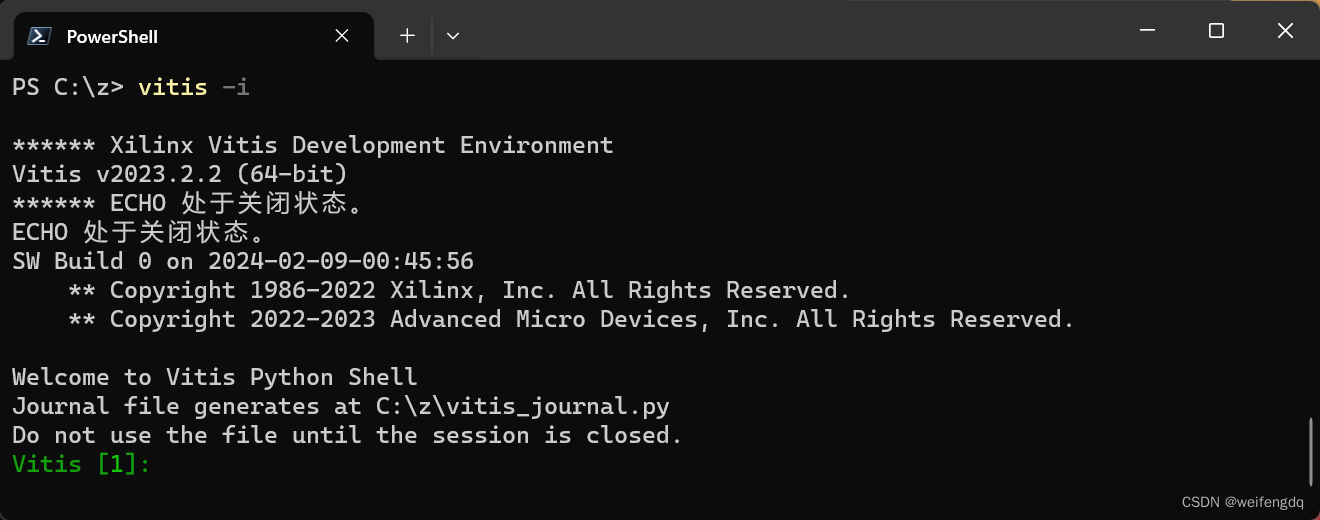

终端验证

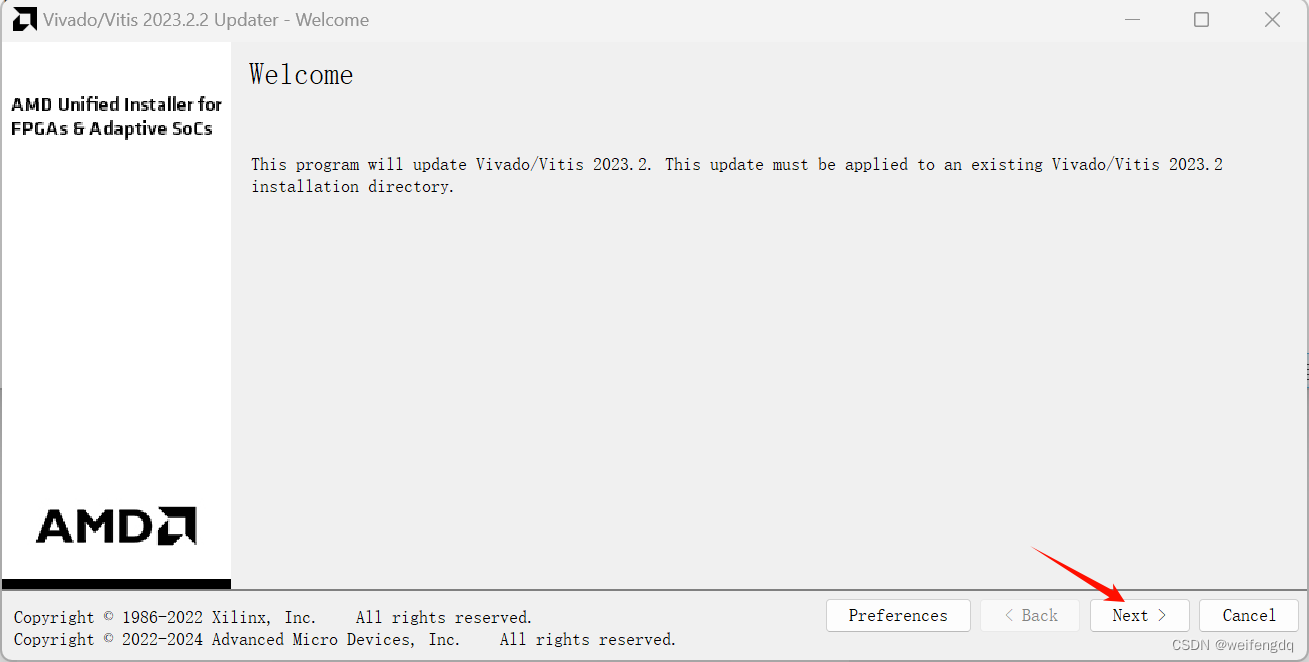

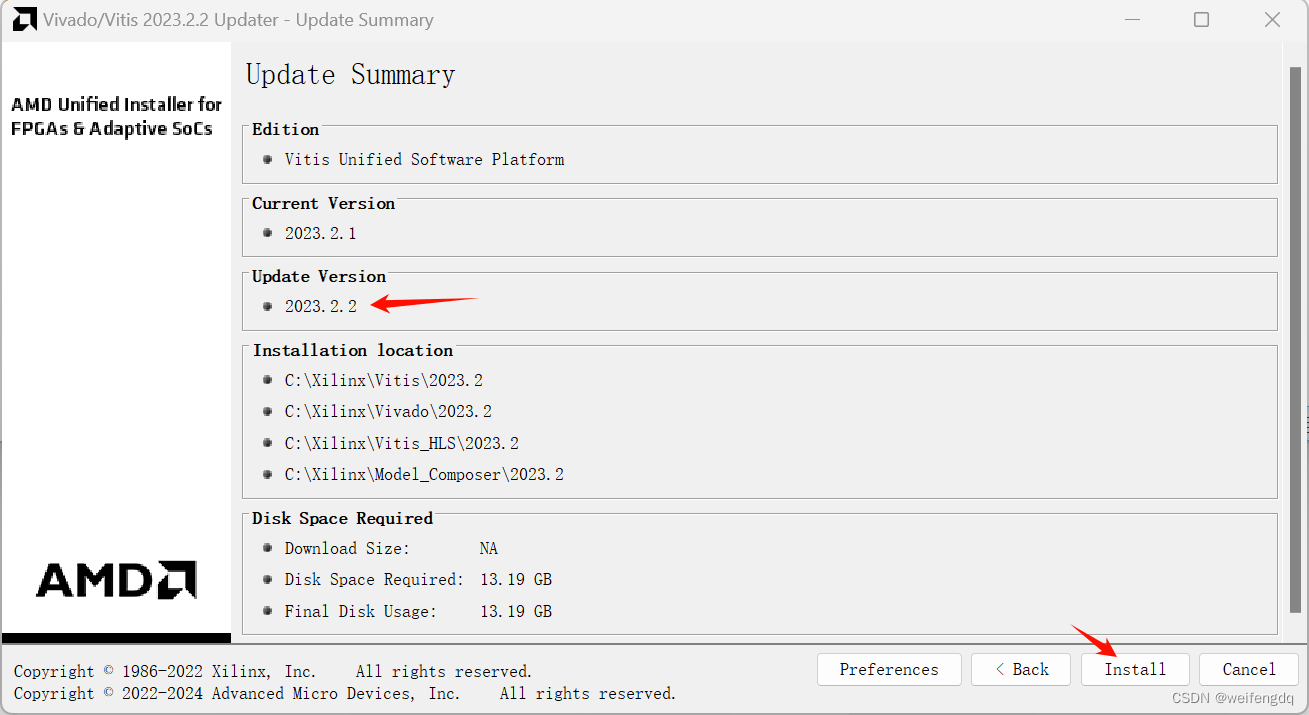

Vivado 安装更新

如果之前安装过Vivado, 现在想安装最新的更新, 如下:

-

可以直接去 下载 (xilinx.com) 中下载最新的更新

-

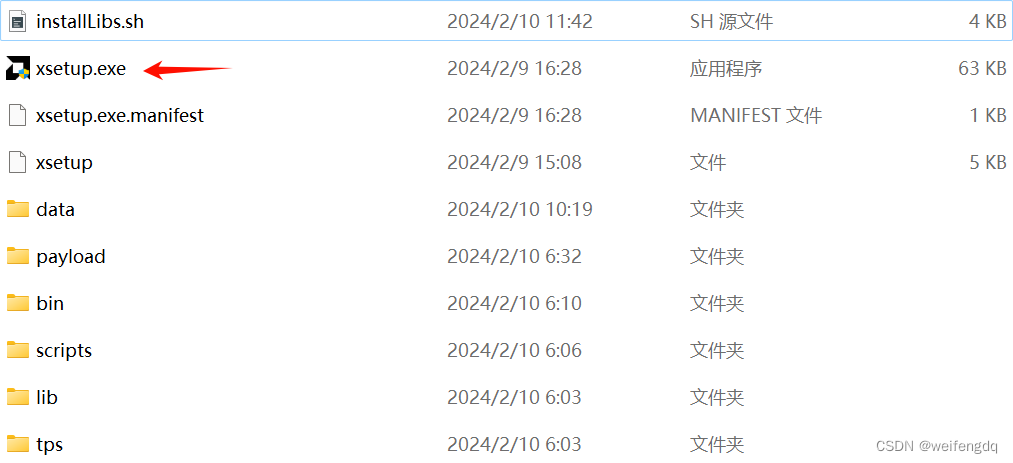

下载完后解压, 双击 xsetup.exe 安装

-

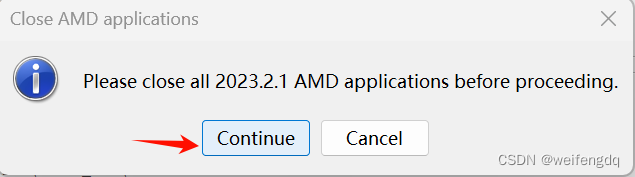

按提示关闭所有的AMD应用后点击Continue

-

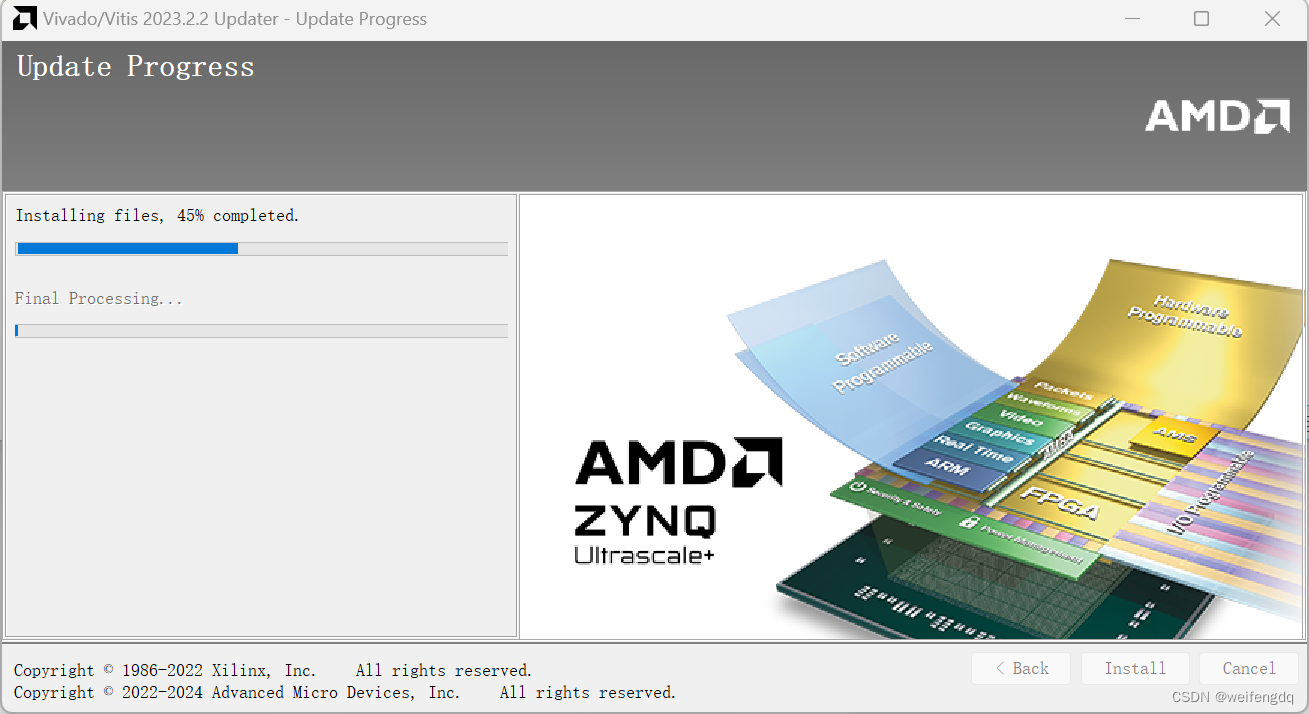

提示更新完成. 新开终端检验版本是 v2023.2.2

Vivado 工程操作

Vivado工程有以下几种方式:

- GUI, Vivado GUI创建的工程也可以导出为Tcl文件, 之后可以用该Tcl文件复原工程

- Tcl命令或脚本.

实时上GUI的几乎每次确认操作会在Tcl Console窗口(可以Collapse all折叠查看)中打出相应的Tcl命令, 二者的操作是等价的.

注: vivado可以用tcl脚本管理工程, vitis是tcl,各种实用工具,python和cmake脚本管理工程, 可参考logs文件夹下的builder.py以及.log文件. 可参考 Vitis 交互式 Python Shell Vitis 命令和实用工具 本篇不作赘述. Vitis的工程操作部分放到了下面的 Blink -> Vivado MicroBlaze Vitis 2023.2 小节.

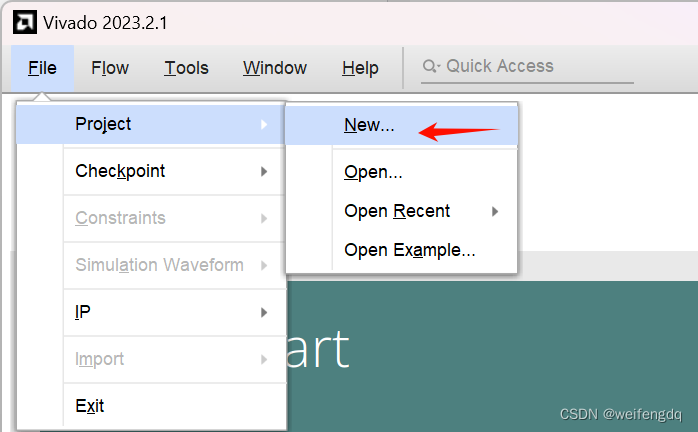

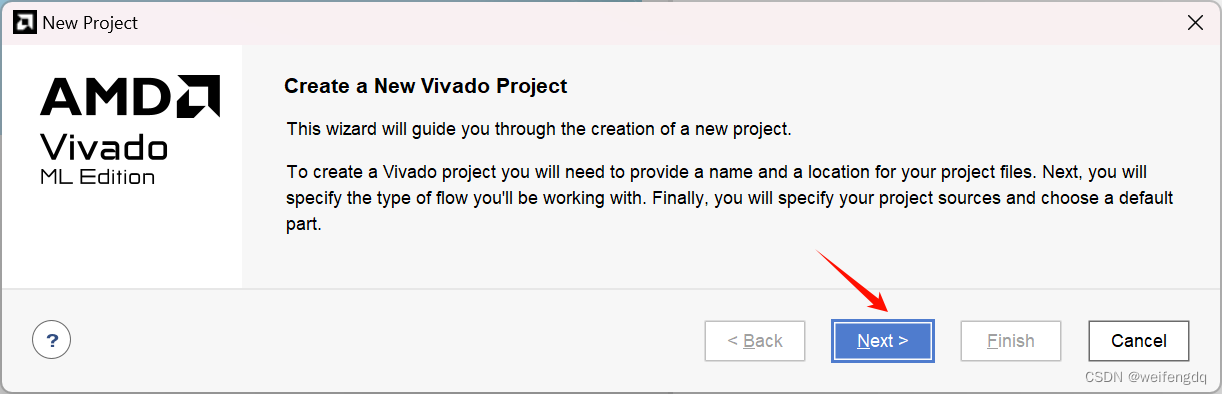

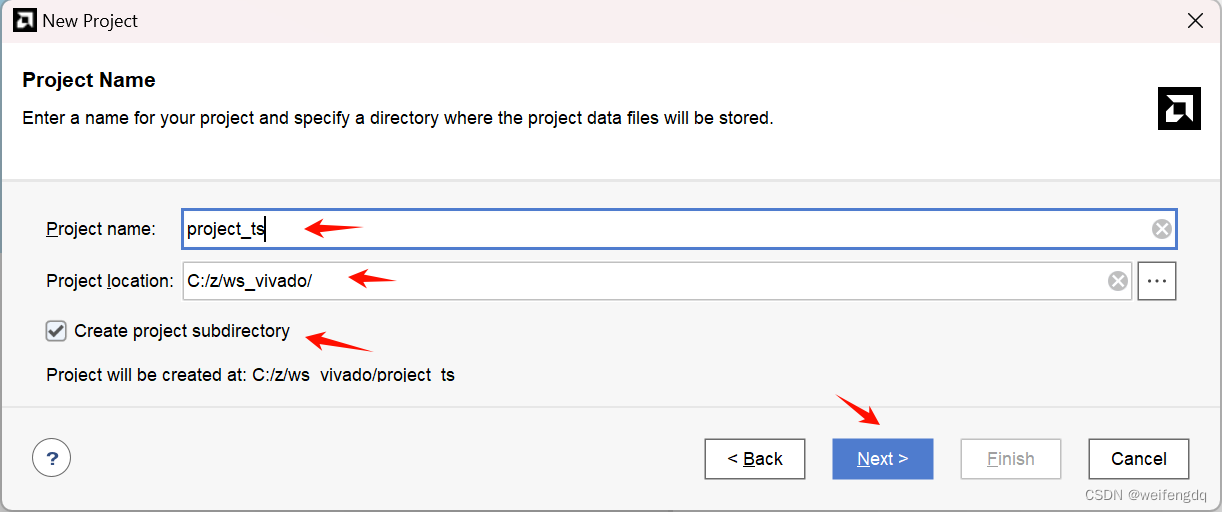

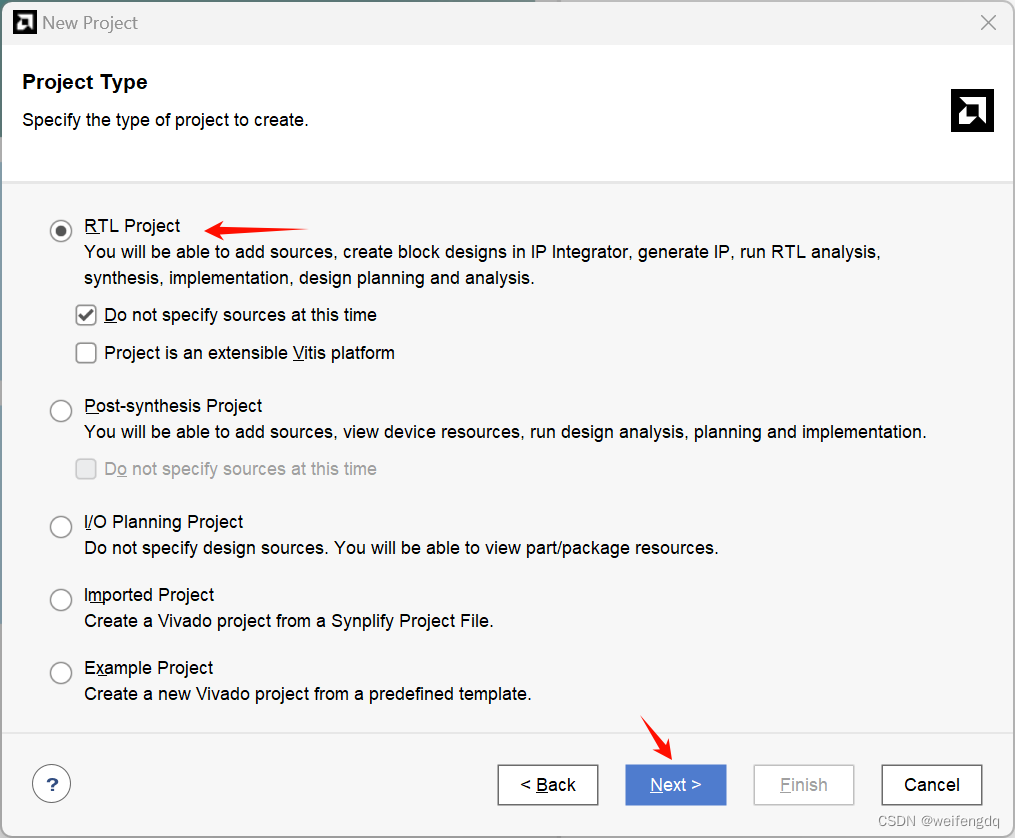

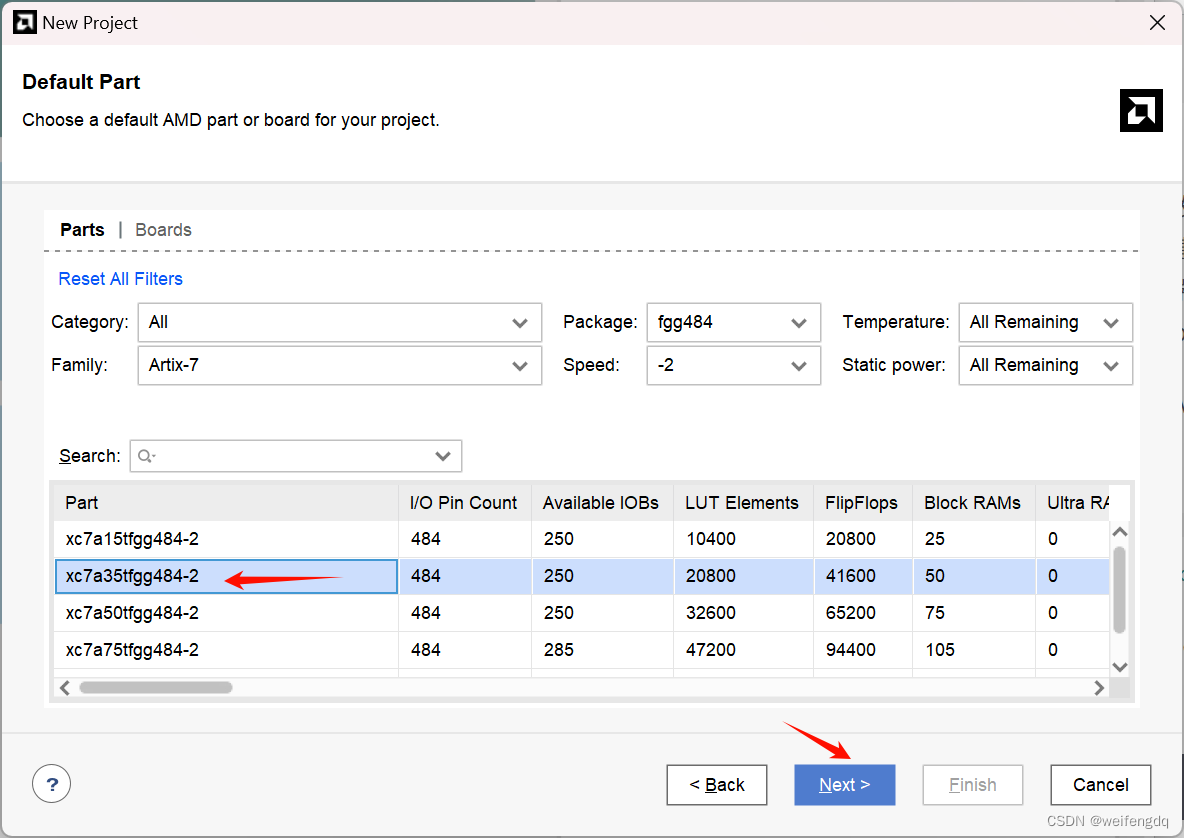

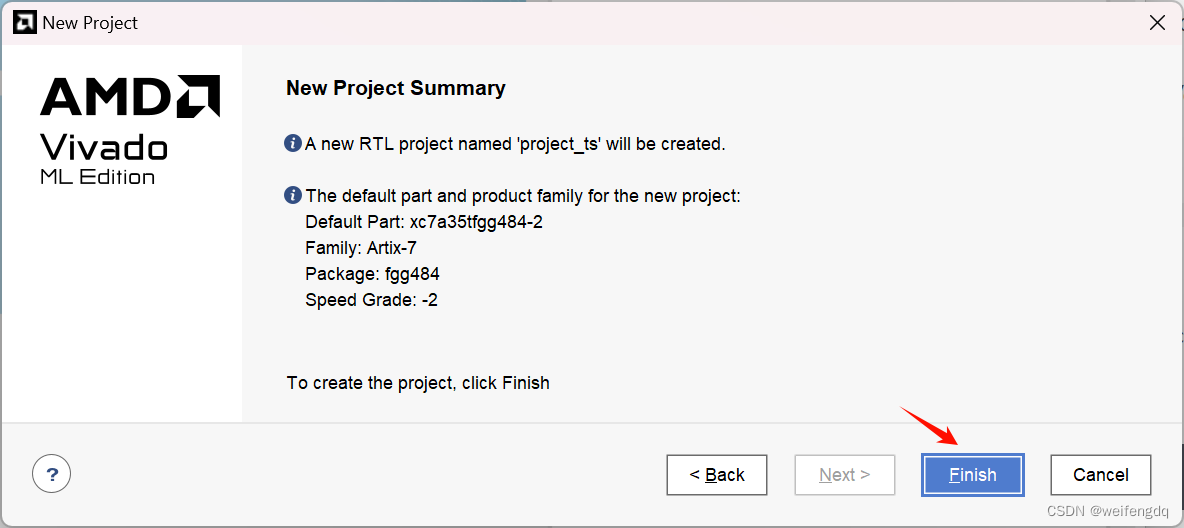

GUI 创建工程

如下:

打开已有工程

打开工程:

- 方法一, 可以 File -> Project -> Open -> 选择.xpr文件打开

- 方法二, 双击 .xpr 文件打开

- 方法三, 命令行

vivado *.xpr

从已有工程创建, 重命名工程

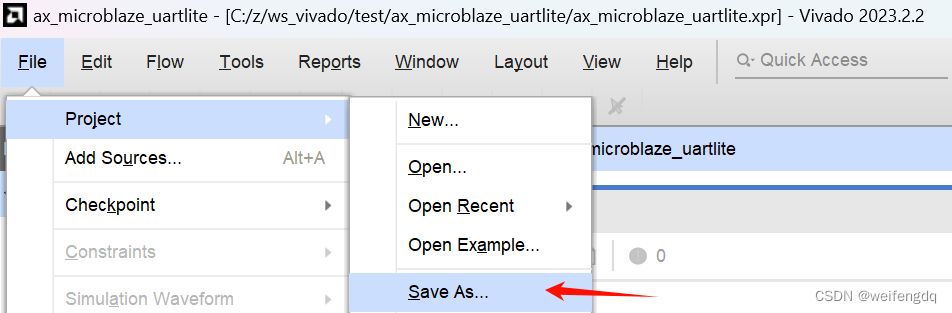

使用另存为实现, 如图

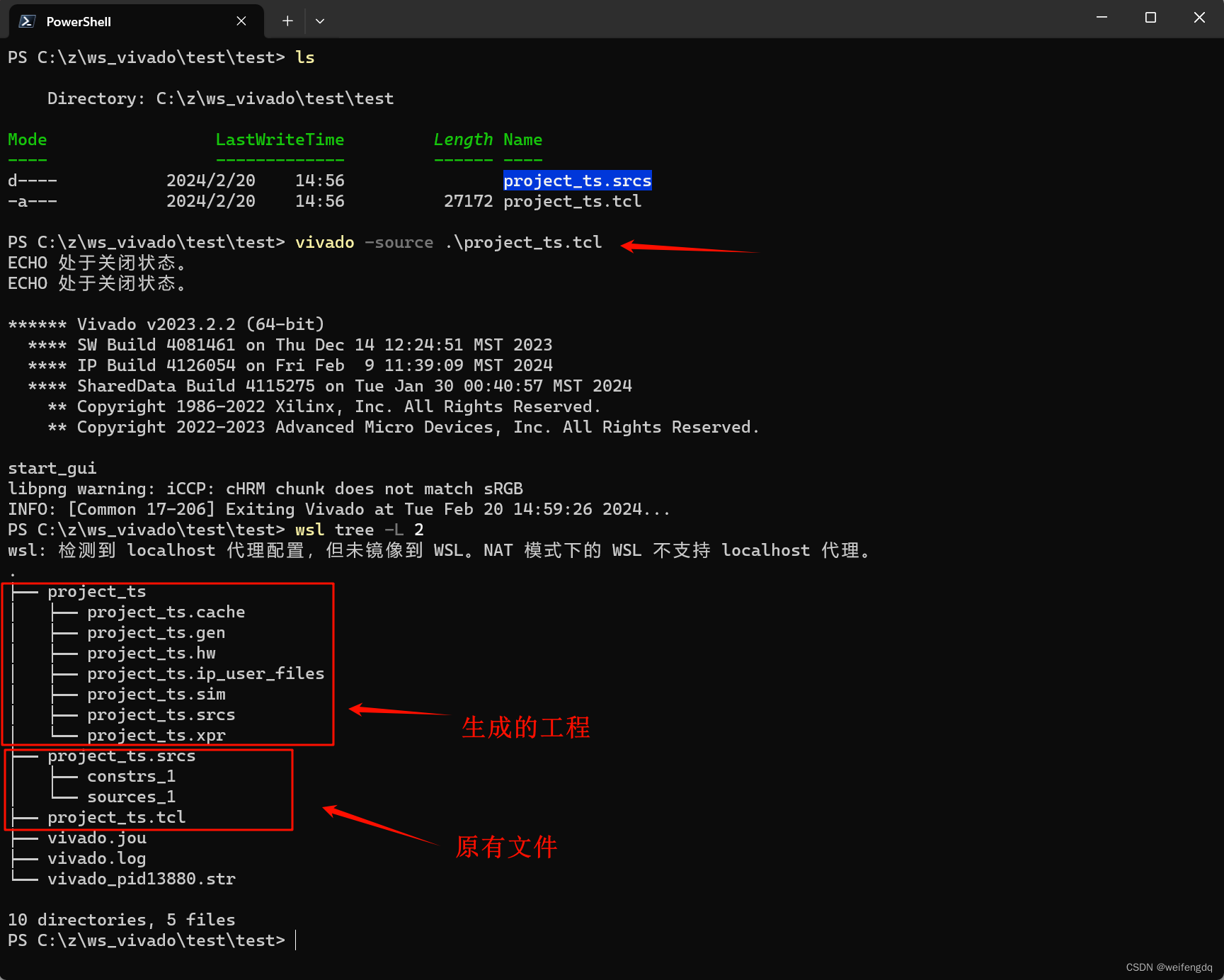

GUI导出TCL, TCL复原工程

参考 Creating a Tcl Script to Recreate the Project • Vivado Design Suite User Guide: Design Flows Overview (UG892) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

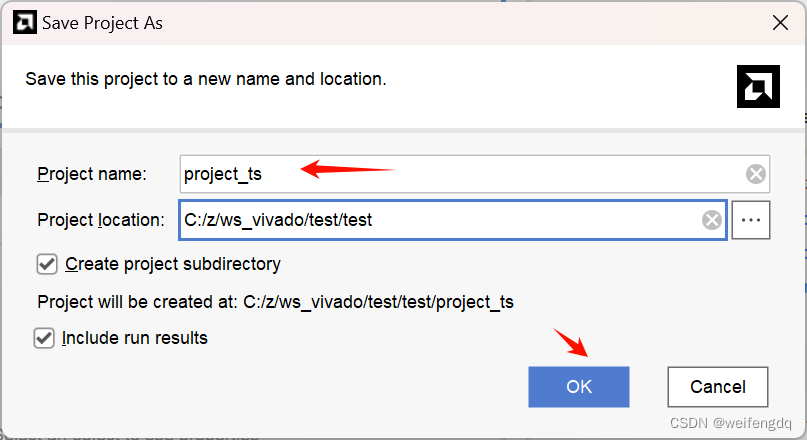

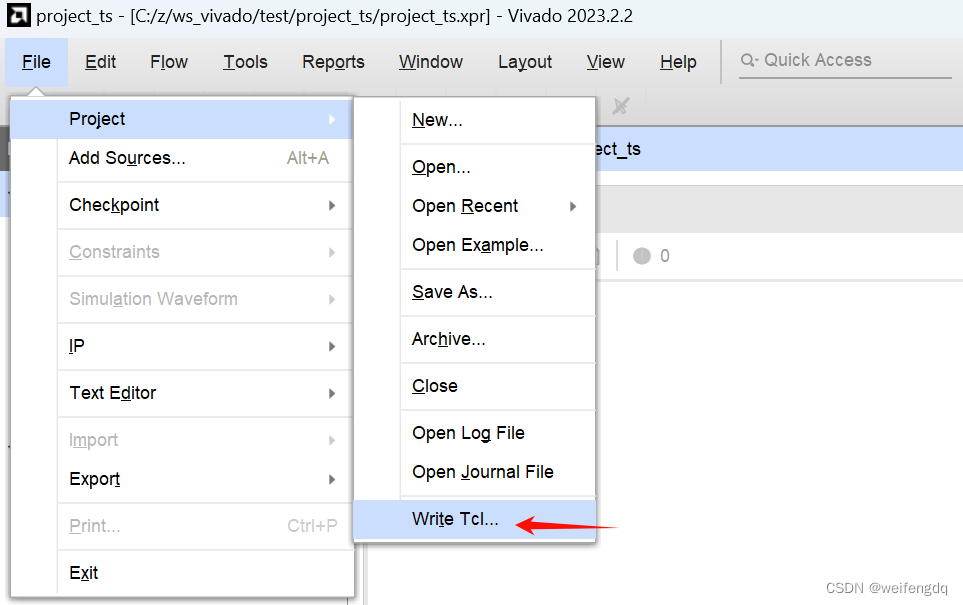

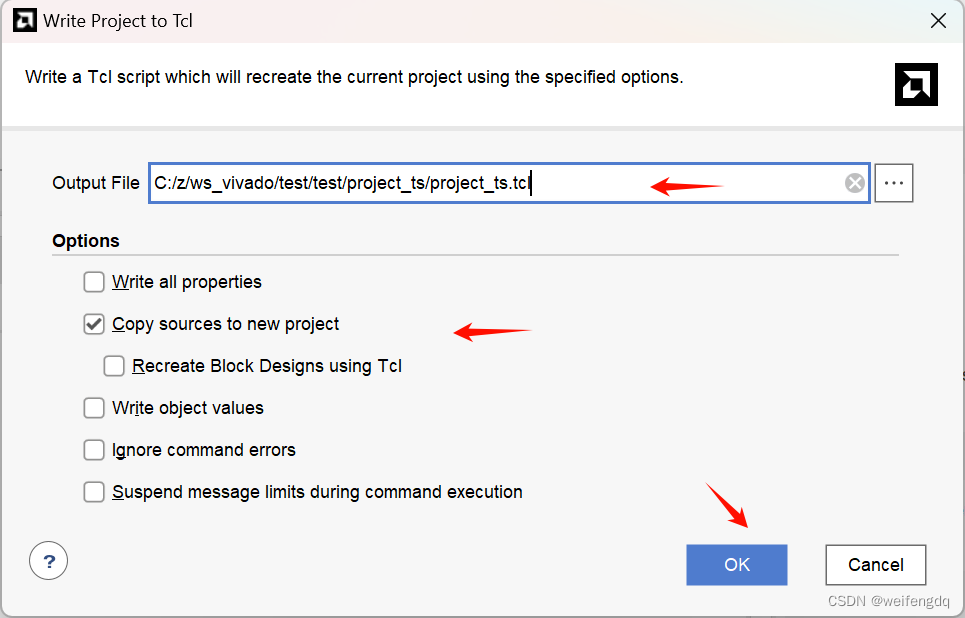

File -> Project -> Write Tcl

现在我们关掉Vivado, 拷贝出 .tcl文件, .srcs文件夹 必要时还可以拷贝 .gen文件夹以加快速度, 删掉整个工程文件夹, 打开终端, 使用 vivado -source *.tcl 生成工程, 文件夹中可以看到重新生成了整个工程文件夹

Tips: 这对于使用git管理工程是有利的, 基本上 tcl 文件和 srcs 文件夹都是文本文件, 避免了二进制文件不容易管理的缺点, 又能完整的复现整个工程.

TCL命令

Tcl是很常用的编程语言, 不止应用在FPGA开发上.

Xilinx官方的Vivado Tcl命令参考指南: 简介 • Vivado Design Suite Tcl 命令参考指南 (UG835)

示例参考 Creating a Project Using a Tcl Script • Vivado Design Suite User Guide

常用的TCL命令:

# 打开 Vivado Tcl shell

vivado -mode tcl# 批处理Tcl脚本

vivado -mode batch -source <your_Tcl_script># 启动Vivado

vivado

start_gui# 创建RTL项目

create_project my_project C:/team/designs/my_project -part xc7a35tfgg484-2

set_property DESIGN_MODE RTL [current_fileset]

# set_property PART xc7a35tfgg484-2 [current_project]

# set_property target_language Verilog [current_project]# 打开项目

open_project c:/projects/project_1.xpr# 另存为

save_project_as new_project c:/projects/project_1.xpr# 关闭

close_project# 打包项目

archive_project -exclude_run_results proj3.zip# add_files 命令从当前位置引用该文件。 import_files 命令将文件复制到项目中

add_files top.v

import_files -fileset constrs_1 C:/projects/sources/timing.xdc

add_files -norecurse source_dir

import_files source_dir# 添加现有 IP 源, add_files or import_ip

import_ip C:/projects/sources/char_fifo/char_fifo.xci# Synthesis 合成

launch_runs synth_1

wait_on_run synth_1

open_run synth_1 -name netlist_1# Implementation 实施

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1# 导出tcl脚本, 更多命令参考 write_project_tcl -h

open_project test/test.xpr

write_project_tcl recreate.tcl

close_project

source recreate.tclVivado 版本控制

说明: 本节是Vivado工程的版本控制, 不完全适用于Vitis工程

参考:

- 使用源代码控制系统 • Vivado Design Suite 用户指南:系统级设计输入 (UG895) • 阅读器 • AMD 计算文档门户 — Working with Source Control Systems • Vivado Design Suite User Guide: System-Level Design Entry (UG895) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

以下是机翻.

为什么使用版本控制?

- 自动化关键开发管理

- 里程碑 “备份”

- 必要时可还原到上一个里程碑

- 记录更改

- 缩短编译时间

- 依赖性跟踪–仅在输入发生变化时编译

- 利用并行优势–独立步骤并行运行

- 大多数客户使用某种形式的版本控制

The UltraFast Design Methodology Guide(UG949) 建议将版本控制与Vivado Design Suite一起使用.

Vivado 版本控制理念

- 设计为“友好”的版本控制

- 没有与特定工具的直接集成

- 通常更喜欢基于ASCII的内部文件(XML项目文件)

- 容忍隐藏的“点”文件和只读源“锁定”在版本控制中

- 在打开项目时尽量减少文件更新,只写入更改

- 工作于不同的使用模式

- GUI(IDE)与 非 GUI(TCL 脚本)

- 项目与非项目流程

- 分布式与集中式版本控制存储库

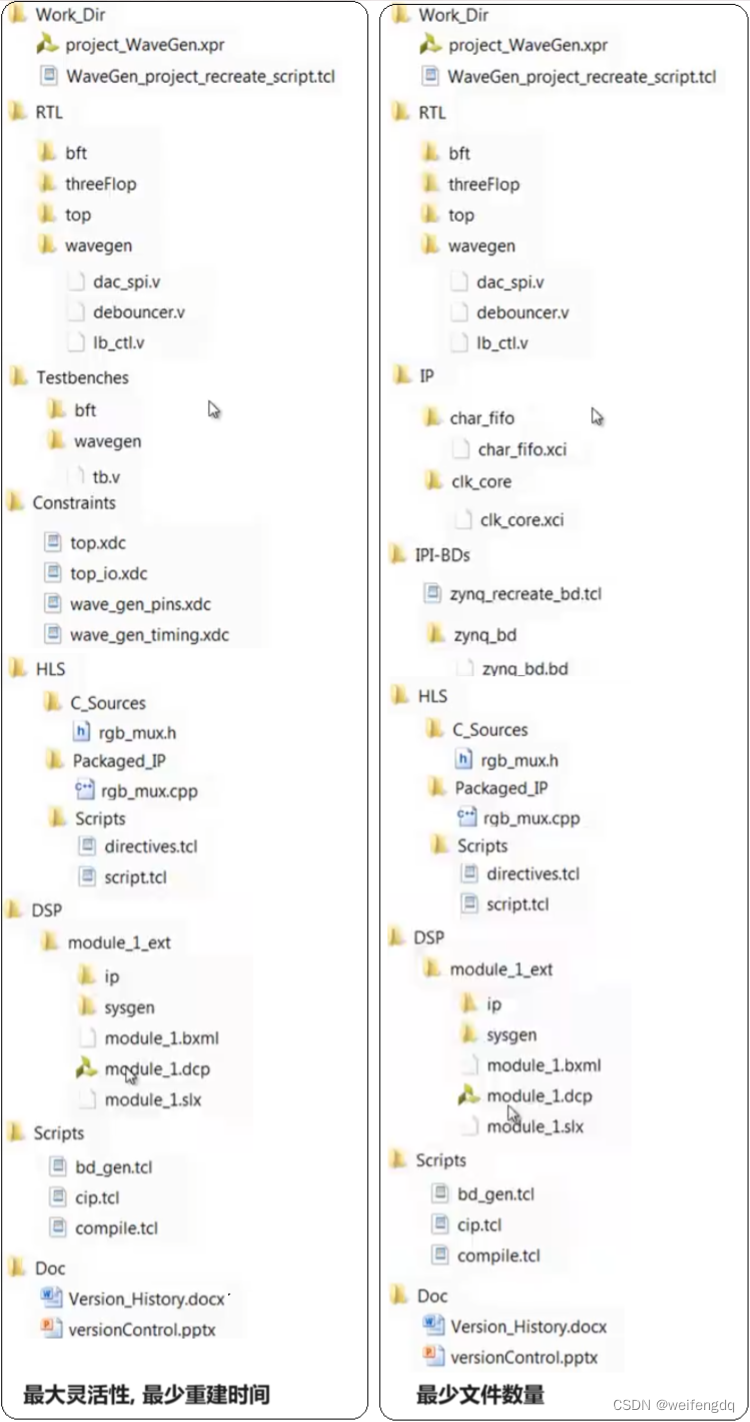

两种版本控制策略

- 最大的灵活性(Xilinx推荐)

- 可选择在 Vivado 的未来版本中使用 IP,而无需升级

- 更短的运行时间以重建项目

- 最少的文件

- 以牺牲灵活性和运行时为代价管理的文件数最少

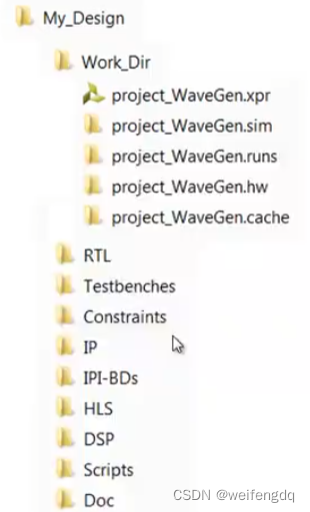

推荐的目录结构

- 在单独的远程目录中管理不同的源类型

- 使用“work”目录编译设计并创建Vivado项目

- 使用来自各个目录的远程源设置Vivado项目

- 选择不将它们复制到项目中

- 要么直接从远程源区域管理修订,要么将其用作项目的本地沙盒

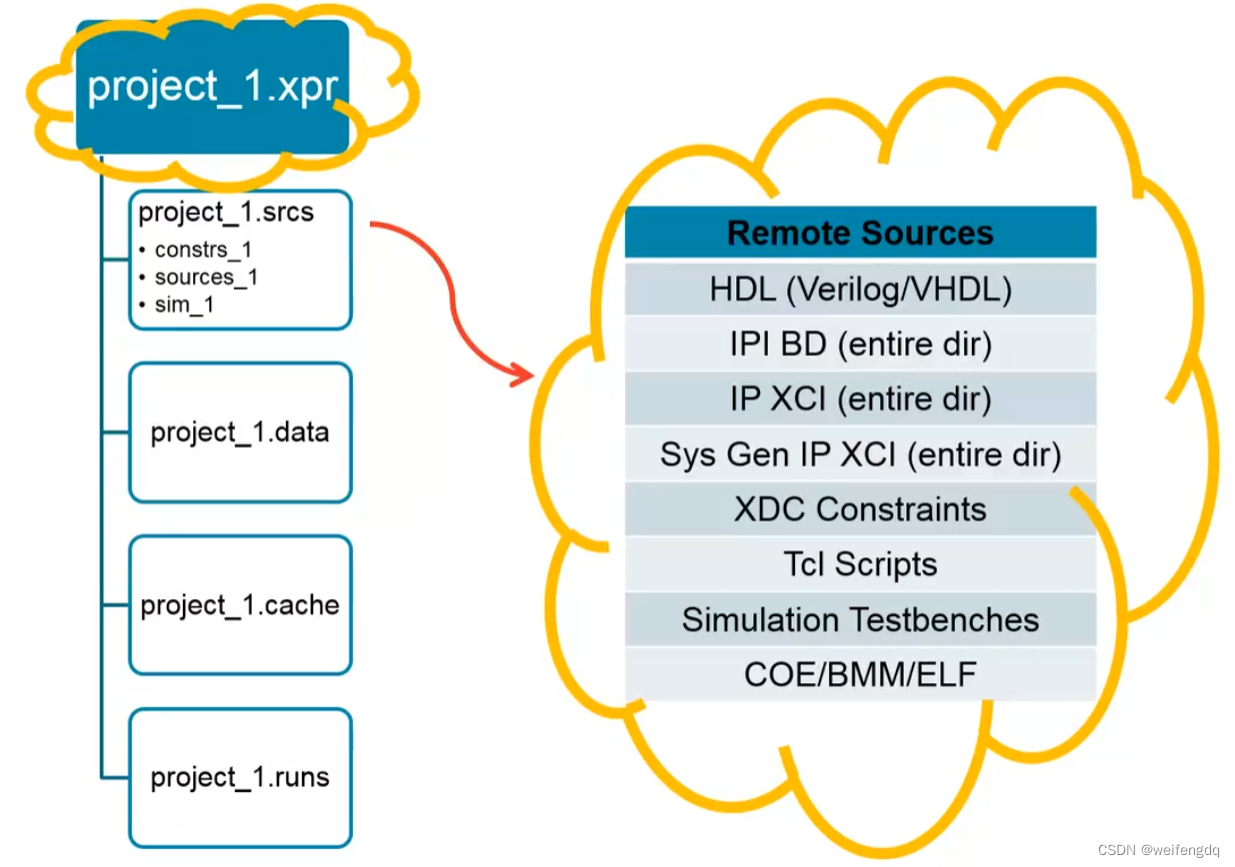

最大的灵活性 - 推荐管理的文件

- 如果使用项目,只需管理 .xpr 文件或 Tcl 脚本用于重新创建

- 使用 write_project_tcl 命令创建一个脚本来重新创建项目

- 不要签入项目子目录

- 自行判断RTL、XDC等目录结构

- 对于 IP 和 IP Integrator 源,管理整个目录树(指的是.gen文件夹???)

- 生成的源代码可用于将来的 Vivado 版本

- 管理Vivado HLS源文件、脚本、示例项目和打包的IP

- 管理 DSP 源的整个 System Generator 目录

- 根据需要管理脚本和文档

- 对于 SDK,管理 .hdf 文件

最少的文件 - 推荐管理的文件

- 如果使用项目,只管理.xpr 文件或 Tcl 重新创建脚本

- 使用 write_project_tcl 命令创建脚本以重新创建项目

- 不要签入项目子目录

- 对于 IP,只检查.xci 文件

- xci 文件可用于重新创建 IP 输出产品

- 只能使用创建 IP 时使用的 Vivao 版本重新创建 IP。

- 对于 IP Integrator,签入 .BD 文件或 Tcl 重新创建脚本

- 使用 write_bd_tcl 命令为块设计(block design)创建脚本

- 管理 Vivado HLS 源文件、脚本、示例项目和打包的IP

- 管理 DSP 源的整个 System Generator 目录

- 根据需要管理脚本和文档

- 对于SDK,管理.hdf文件

摘要/补充信息

- 有两种记录在案的方法可用于决定管理哪些文件

- 最大灵活性/最少重建时间,Xilinx 建议

- 管理的文件数量最少

- 关键是使用远程源,而不是管理项目目录

- 查看 UG949-UltraFast Design Methodology Guide for the Vivado Design Suite 中的第 3 章

UG949的最新官方中文版参考 简介 • 适用于 FPGA 和 SoC 的 UltraFast 设计方法指南 (UG949) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

视频 使用具有版本控制功能的 Vivado Design Suite — Using Vivado Design Suite with Revision Control (xilinx.com) 附图

本地文件夹

推送到远程的文件

推荐的管理目录举例(注: 左边应另含IP生成的整个文件目录, 右边仅含IP的xci文件)

Blink

板载硬件:

- FPGA: xc7a35tfgg484-2

- 时钟: 50MHz, 有源, 单端, 3V3, 引脚Y18

- 复位: 低电平复位, 3V3, 引脚F20

- LED: 低电平点亮, 3V3, 引脚F19

功能: - 亮1.8s, 灭0.2s, 循环

- 这里不细致区分 Blink, Breath, Flashing. 一般Breath牵涉PWM, 更难一些. 这里仅演示Blink.

下面用几种常用方式点灯: - 纯 Verilog

- Embedded: 基于现有IP MicroBlaze, GPIO等, 使用 Vitis 编写C或Cpp代码, 这里裸机跑, 不使用FreeRTOS或Linux. 偏向常见的嵌入式方式

- HLS: 使用Vitis HLS做一个LED的IP, 在Vivado中直接使用(或配合Verilog用).

- HLS + Embedded, 使用HLS做带AXI接口的IP, 连到MicroBlaze进行Embedded开发, 相当于全局Cpp开发

其它的如 SystemVerilog 这里先不赘述了. 由于GUI的操作资料很常见, 这里Verilog部分演示下不要GUI, 纯Tcl脚本和命令行的工作流(暂时省去了综合实现等). 测试部分篇幅原因都省去了.

Tcl脚本新建导出重建工程

上面有GUI新建工程的示例, 这里给一个Tcl脚本新建工程的示例

create_project.tcl

set prj_name "blink"

set prj_dir "$prj_name/$prj_name"

set src_dir "$prj_name/rtl"

set constrs_dir "$prj_name/constrs"

set top_file "$src_dir/$prj_name.v"

set constrs_file "$constrs_dir/$prj_name.xdc"file mkdir $prj_name

create_project $prj_name $prj_dir -part xc7a35tfgg484-2

file mkdir $src_dir

file mkdir $constrs_dir

set file [ open $top_file w ]

puts $file "module $prj_name ();"

puts $file "endmodule"

close $file

close [ open $constrs_file w ]

add_files -fileset sources_1 $top_file

add_files -fileset constrs_1 $constrs_file

运行脚本

vivado -mode batch -source create_blink.tcl

生成的工程如下

.

├── blink

│ ├── constrs

│ │ └── blink.xdc

│ ├── blink

│ │ ├── blink.cache

│ │ ├── blink.hw

│ │ ├── blink.ip_user_files

│ │ └── blink.xpr

│ └── rtl

│ └── blink.v

├── create_blink.tcl

├── vivado.jou

└── vivado.log

打开工程

vivado blink/blink/blink.xpr

如果使用git管理, 可以忽略掉 blink和.Xil文件夹, .jou,.str和.log文件, 但是要导出 tcl 文件:

- 方法一 File -> Project -> Write Tcl, 可以保存为 blink/recreate.tcl

- 方法二, 命令行脚本 export.tcl 如下, 使用

vivado -mode batch -source export.tcl命令导出

open_project blink/blink/blink.xpr

write_project_tcl -force blink/recreate.tcl

close_project

从tcl文件恢复(重建)工程

cd blink && vivado -source recreate.tcl

纯Verilog Blink

blink.v

module blink(input wire clk, // 50MHz input clockinput wire rst, // Reset inputoutput reg led // LED output

);// 1.8s on, 0.2s off at 50MHz is 90M cycles on, 10M cycles offlocalparam ON_CYCLES = 90_000_000;localparam OFF_CYCLES = 10_000_000;reg [31:0] counter = 0; // 32-bit counteralways @(posedge clk or negedge rst) beginif (!rst) begincounter <= 0; // Reset the counterend else beginif (counter < ON_CYCLES + OFF_CYCLES - 1) begincounter <= counter + 1; // Increment the counterend else begincounter <= 0; // Reset the counterendendendalways @(posedge clk or negedge rst) beginif (!rst) beginled <= 1; // Turn off the LEDend else beginif (counter < ON_CYCLES) beginled <= 0; // Low level turns on the LEDend else if (counter < ON_CYCLES + OFF_CYCLES) beginled <= 1; // High level turns off the LEDend else beginled <= led; // Keep the LED stateendendendendmodule

约束文件 blink.xdc

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports rst]

set_property PACKAGE_PIN Y18 [get_ports clk]

set_property PACKAGE_PIN F19 [get_ports led]

set_property PACKAGE_PIN F20 [get_ports rst]

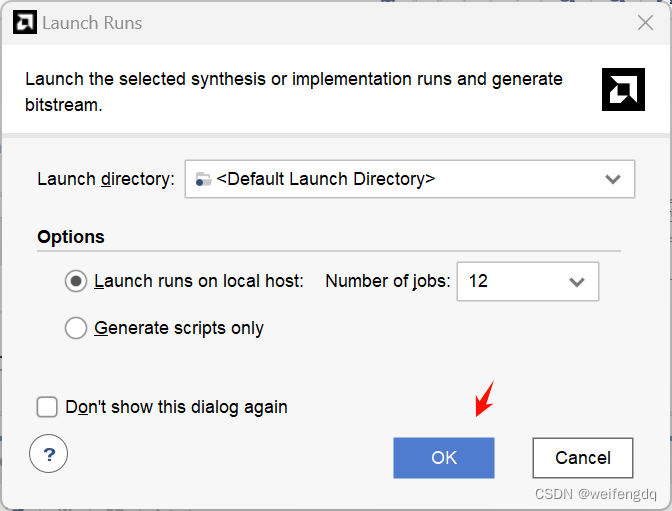

Tcl脚本生成位流文件

bitstream.tcl

open_project blink/blink/blink.xpr

launch_runs impl_1 -to_step write_bitstream -jobs 12

wait_on_run impl_1

close_project

运行

vivado -mode batch -source .\bitstream.tcl

Tcl脚本编程运行

参考GUI运行时的Tcl提示, 给出 program.tcl

set bitstream_file "blink/blink/blink.runs/impl_1/blink.bit"

puts "Programming bitstream file: $bitstream_file"

open_hw_manager

connect_hw_server -allow_non_jtag

open_hw_target

set_property PROGRAM.FILE $bitstream_file [get_hw_devices xc7a35t_0]

current_hw_device [get_hw_devices xc7a35t_0]

refresh_hw_device -update_hw_probes false [lindex [get_hw_devices xc7a35t_0] 0]

set_property PROBES.FILE {} [get_hw_devices xc7a35t_0]

set_property FULL_PROBES.FILE {} [get_hw_devices xc7a35t_0]

set_property PROGRAM.FILE $bitstream_file [get_hw_devices xc7a35t_0]

program_hw_devices [get_hw_devices xc7a35t_0]

refresh_hw_device [lindex [get_hw_devices xc7a35t_0] 0]

运行

vivado -mode batch -source .\program.tcl

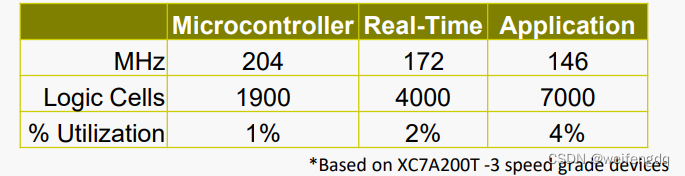

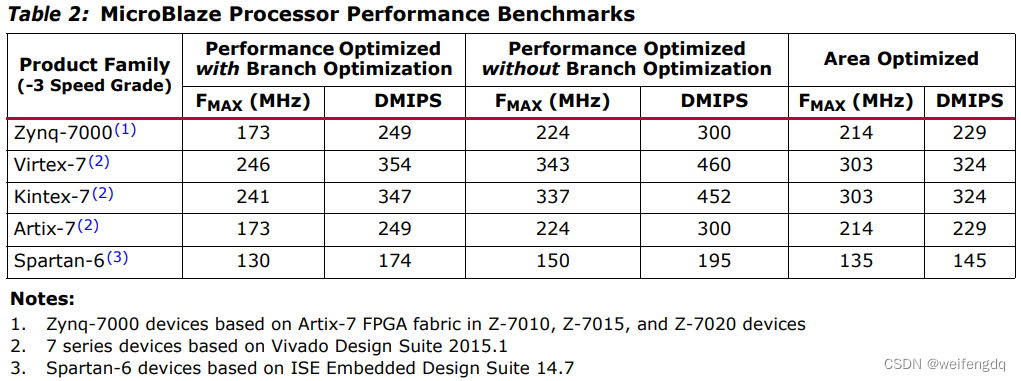

MicroBlaze 简介

AMD MicroBlaze™ 处理器 (xilinx.com), AMD MicroBlaze™ 处理器基于高效的 RISC Harvard 架构,提供一系列可定制、易于集成的 32/64 位微处理器配置。

MicroBlaze三种配置:

- Microcontroller, 微控制器, 执行裸机代码(bare-metal 或 standalone)的理想选择

- Real-time processor, 实时处理器, 确保 RTOS 上的确定性实时处理, 如FreeRTOS

- Application processor, 应用处理, 能够在嵌入式Linux上运行

这个软核可以当单片机耍, 也能跑FreeRTOS, 还能跑Linux, 甚至可以配置32/64bit, 3/5级流水线, 浮点单元, 锁步核, 多核等, 但需要的资源不一样. 参考 MicroBlaze Processor Quick Start Guide (XMP467)

参考 Using the MicroBlaze Processor to Accelerate Cost-Sensitive Embedded System Development (WP469)

MicroBlaze 软核点灯

使用现有的 MicroBlaze Gpio Clk 等IP核, 像开发MCU那样点灯.

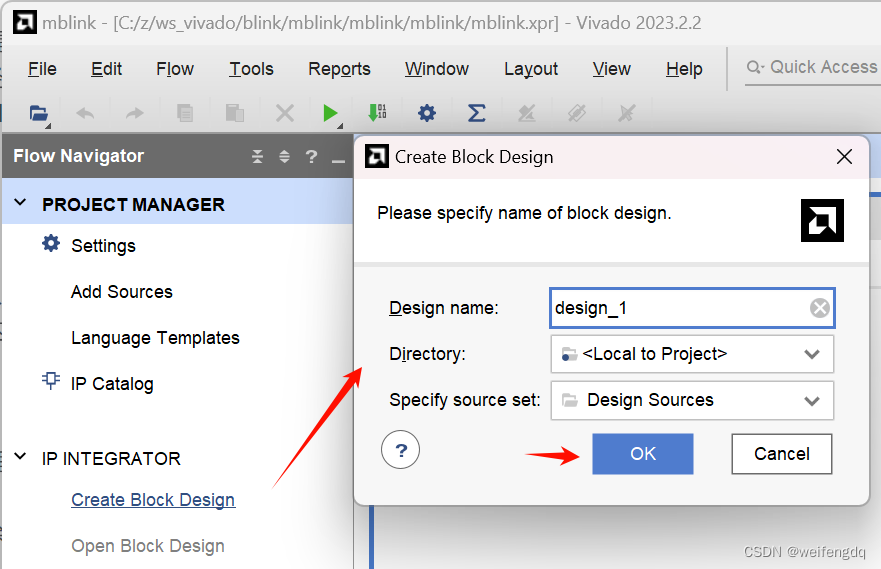

Vivado IP 连线

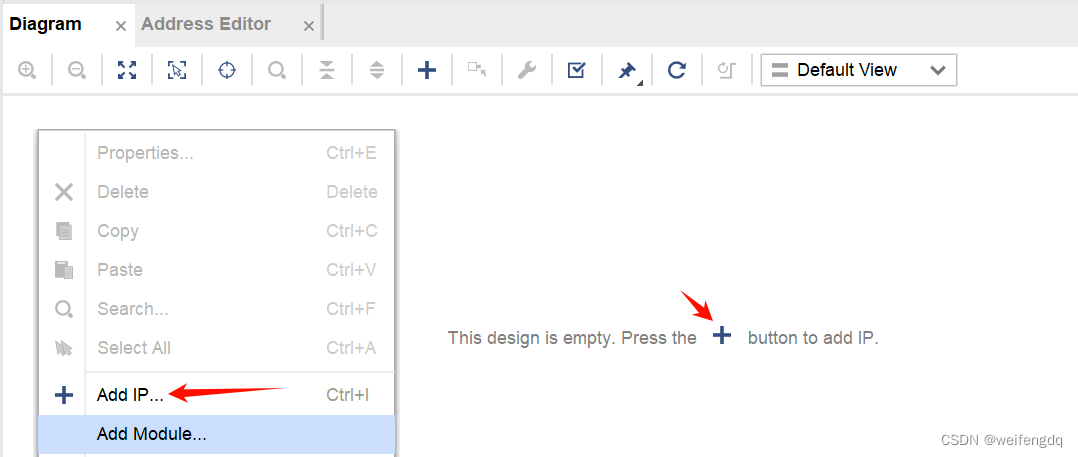

先在Vivado上搭出硬件, 从上面的GUI创建工程后开始

加号或右键添加IP

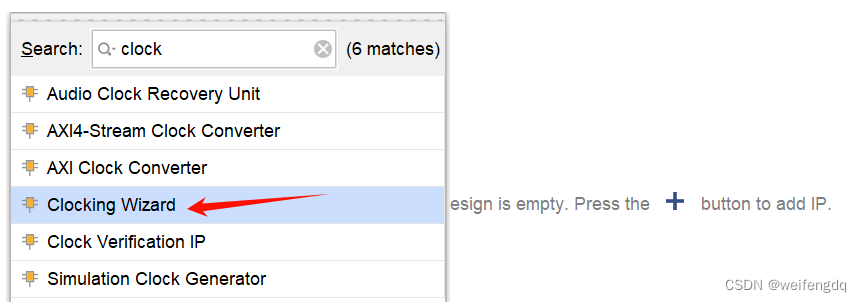

首先就是时钟, 双击放置

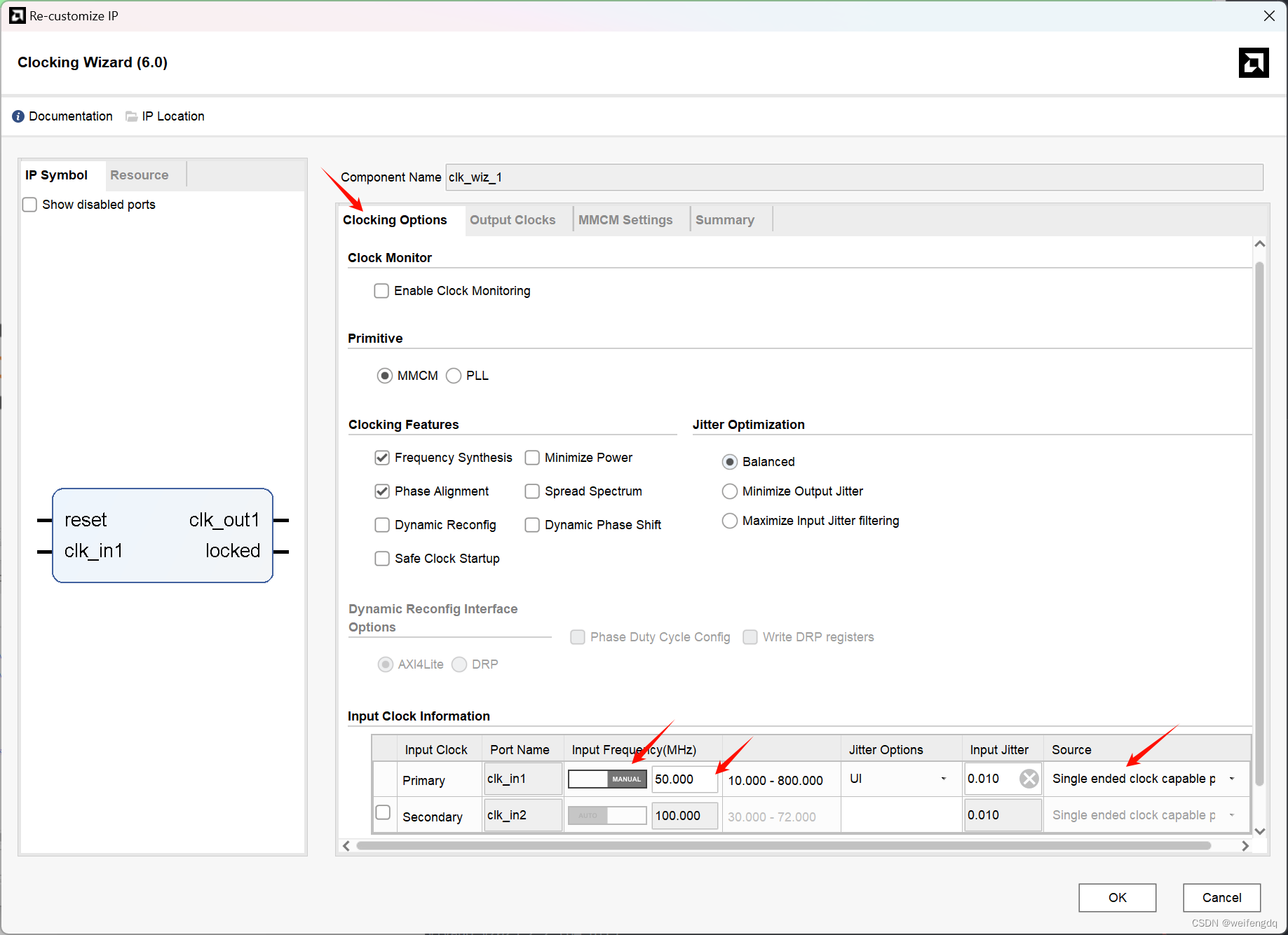

双击Clocking Wizard配置50MHz输入, 单端

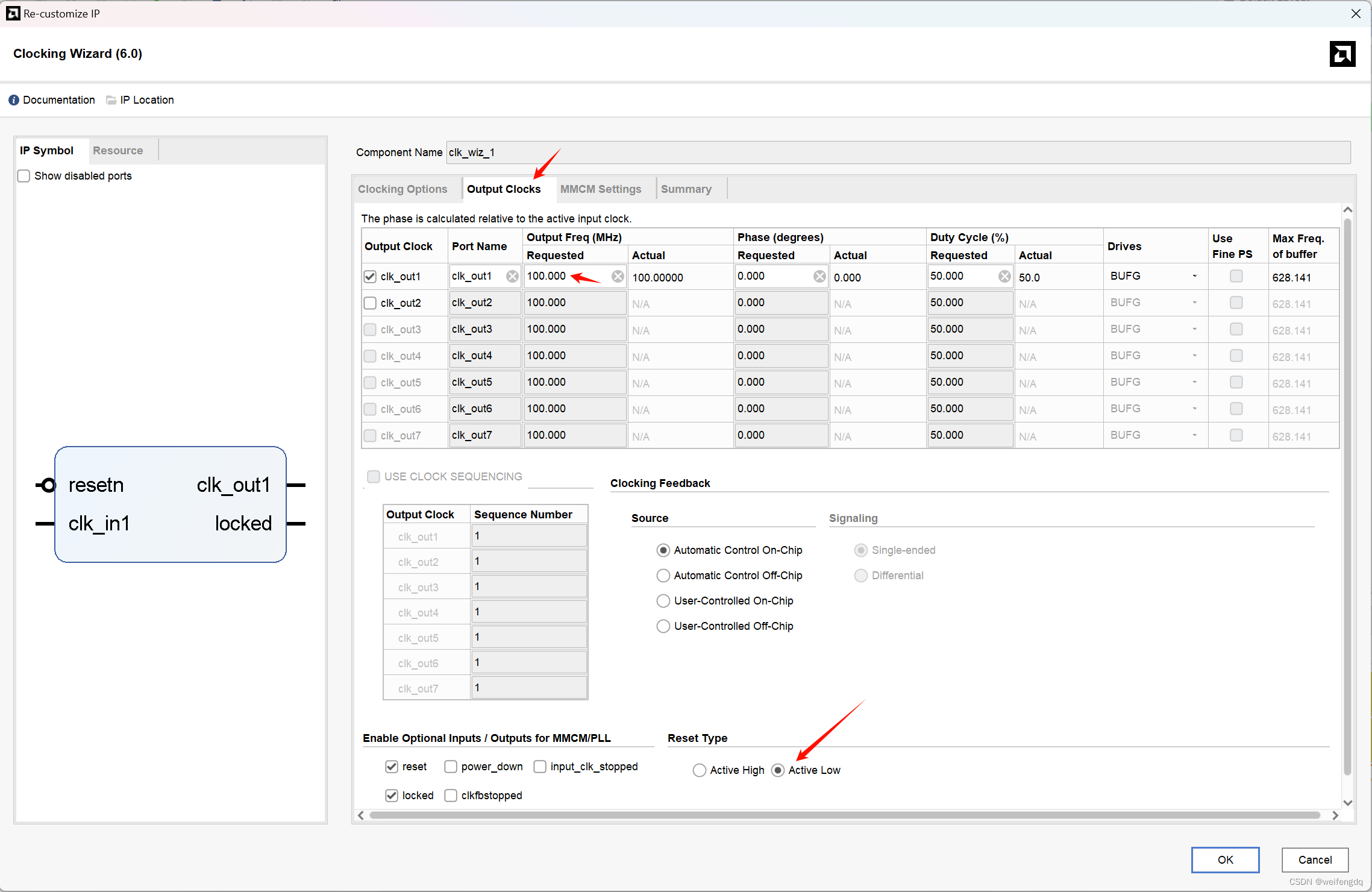

输出100MHz, 低电平复位

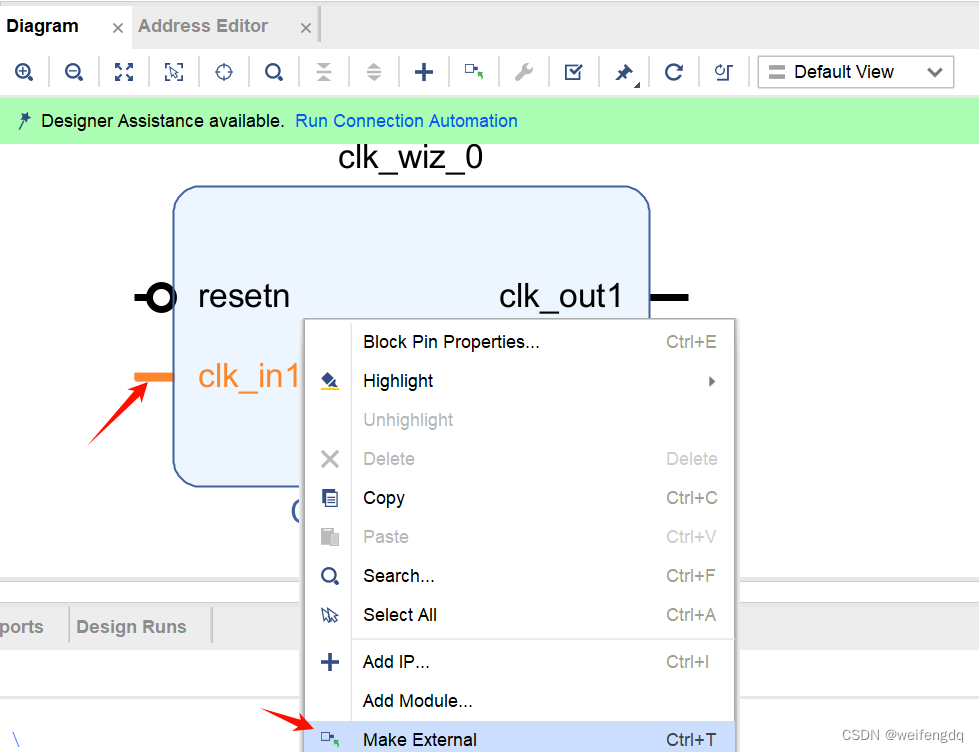

选中并引出clk_in1引脚

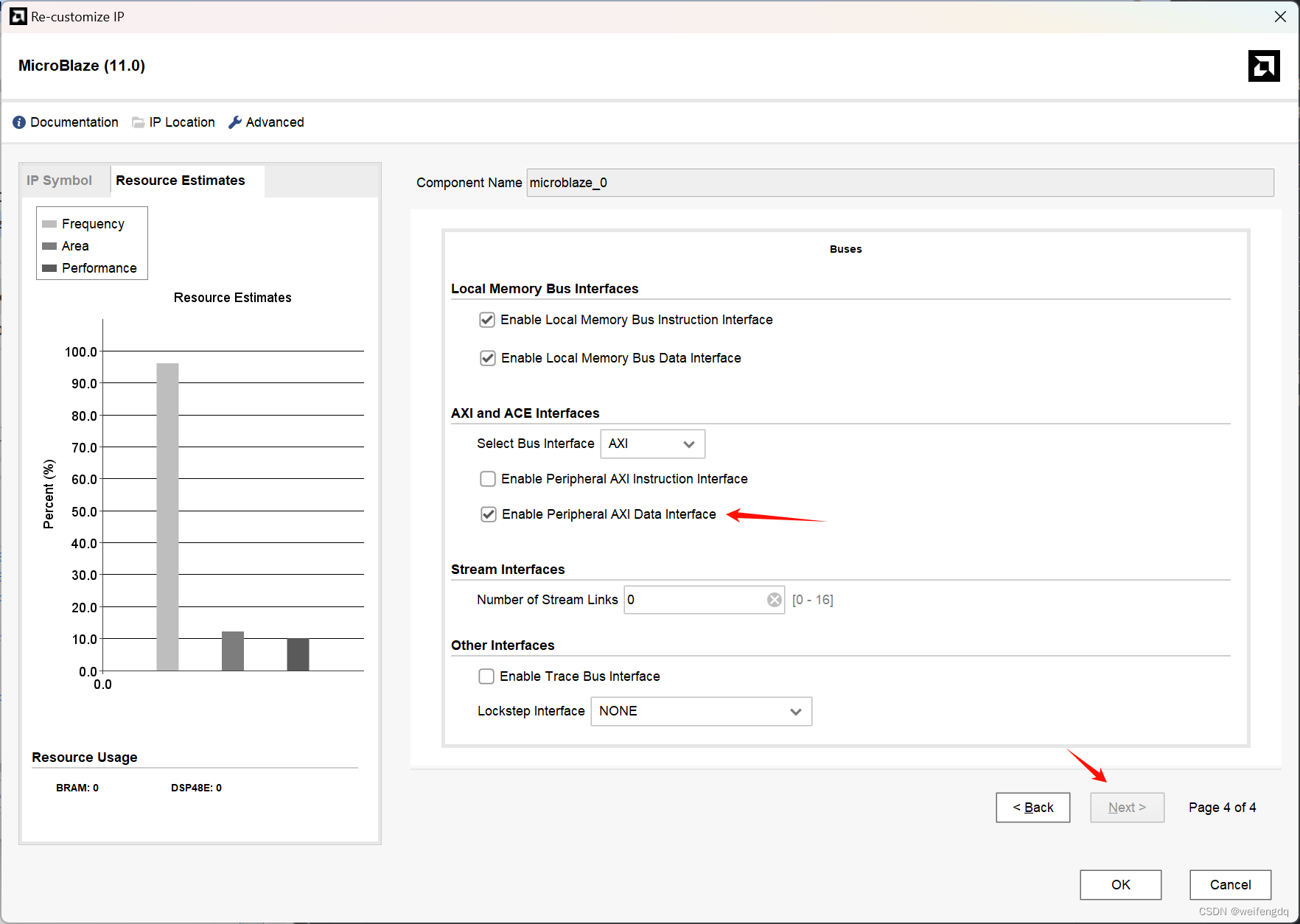

继续右键IP添加Microblaze, 双击设置, Next到第4页, 一般会选一下, Enable Peripheral AXI Data Interface

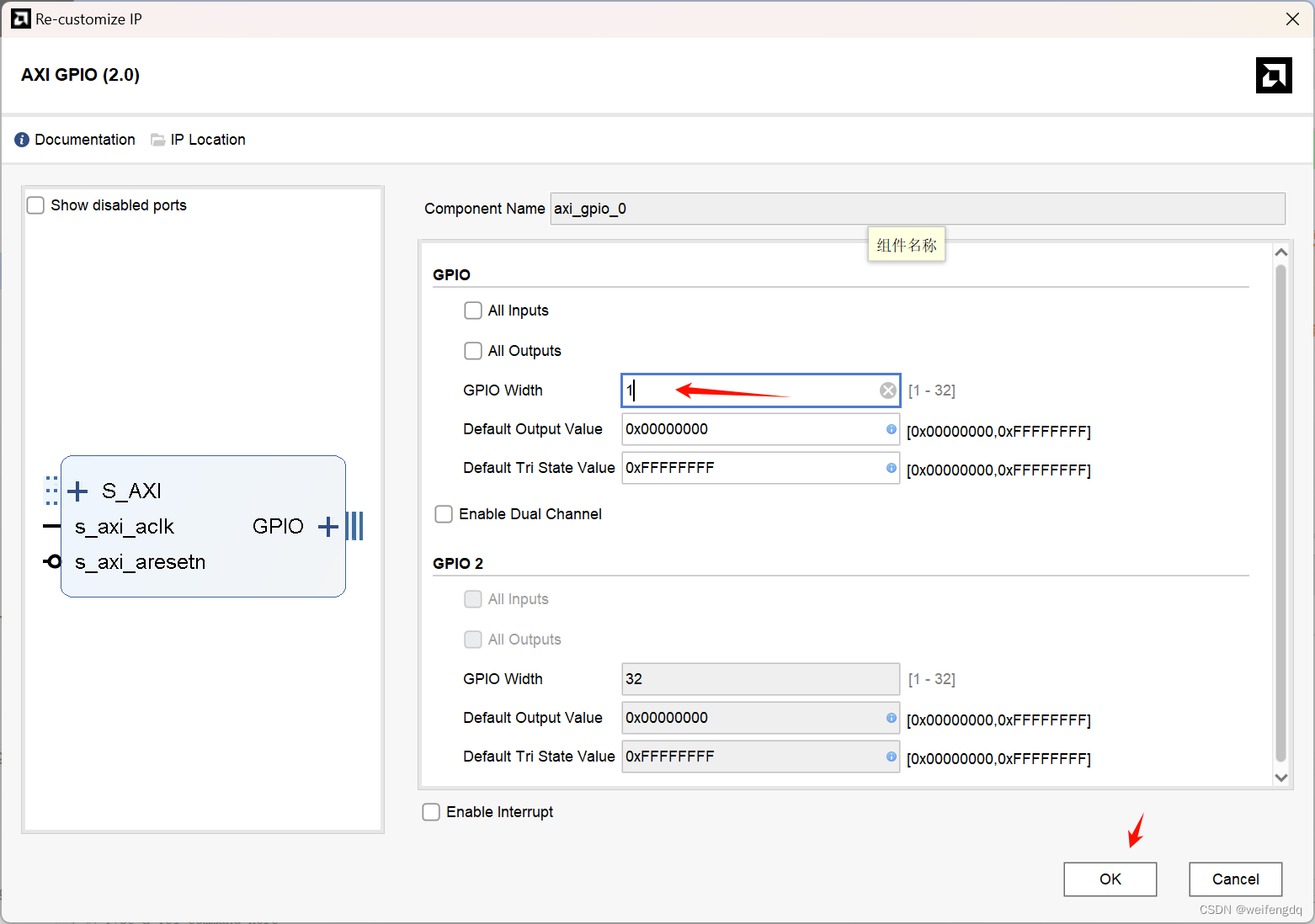

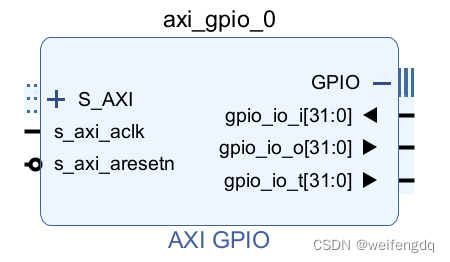

继续右键IP添加GPIO, 双击GPIO, 一个LED, 用1bit宽度就够了

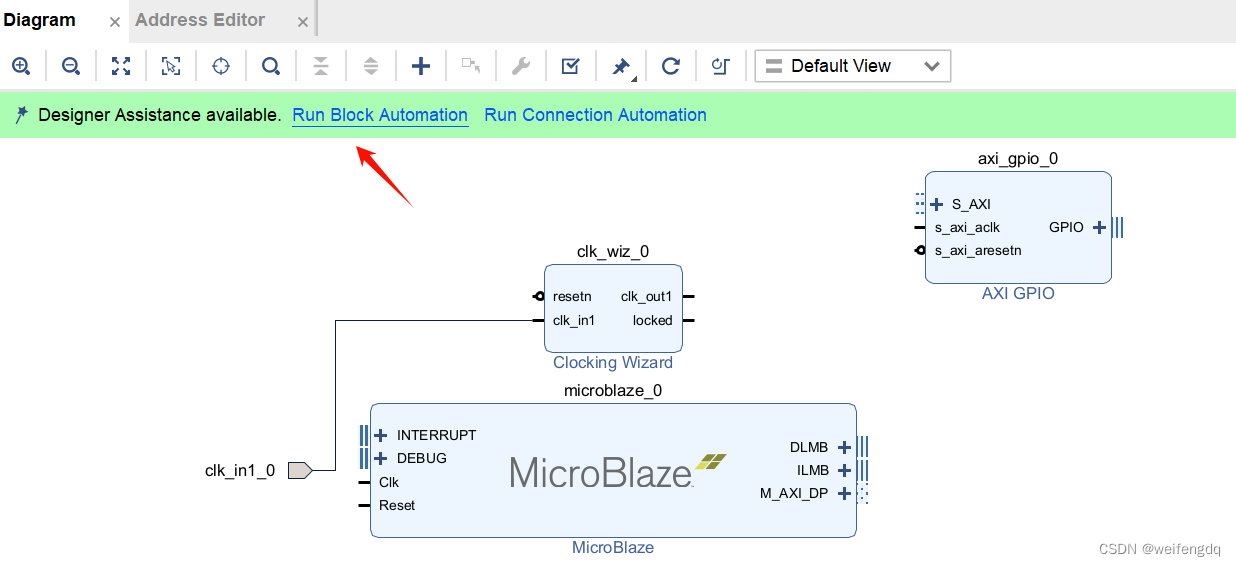

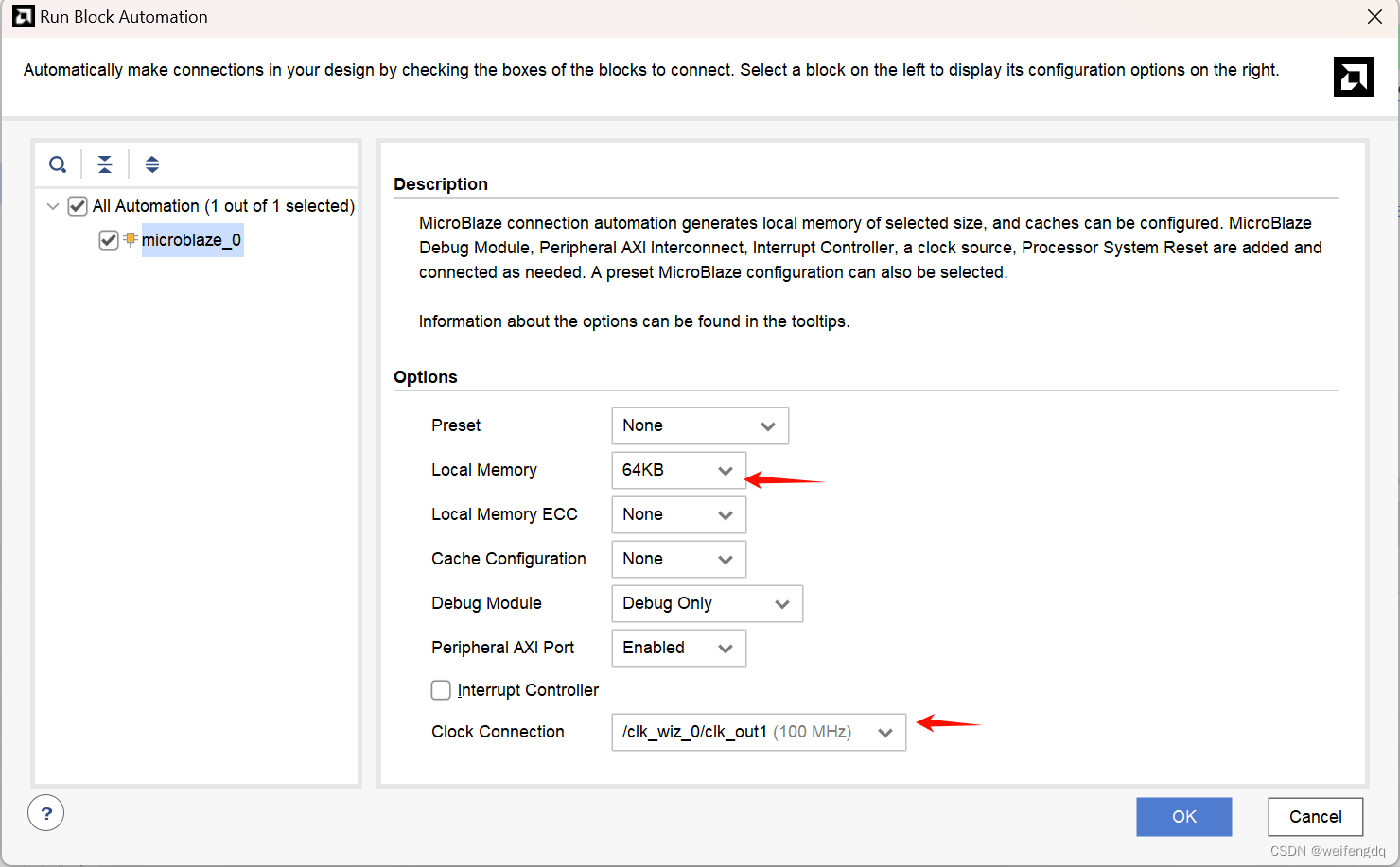

点 Run Block Automation

给64KB

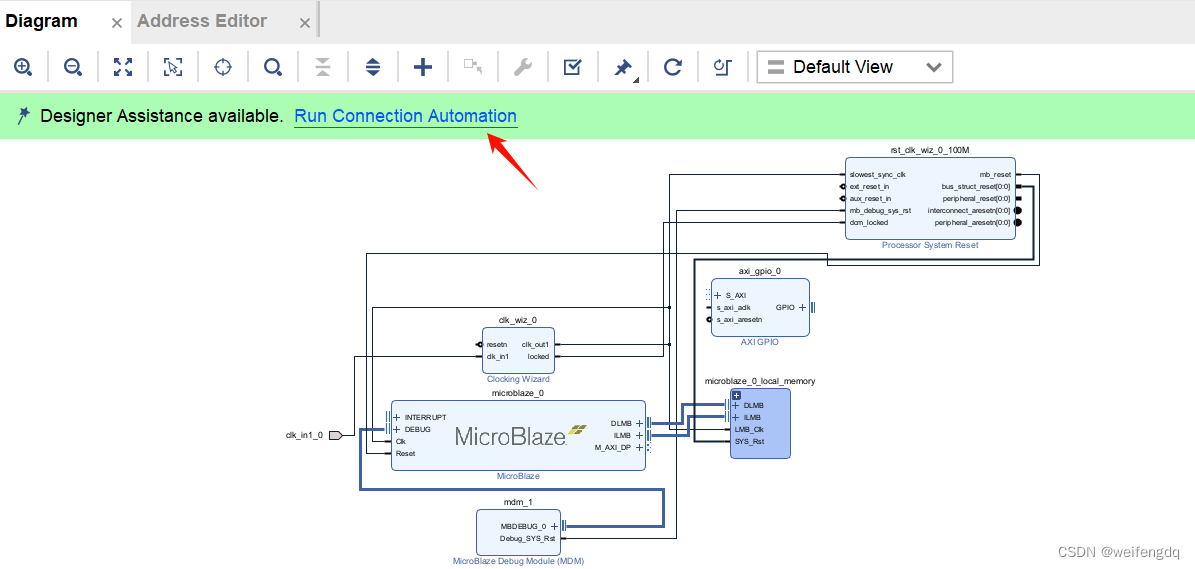

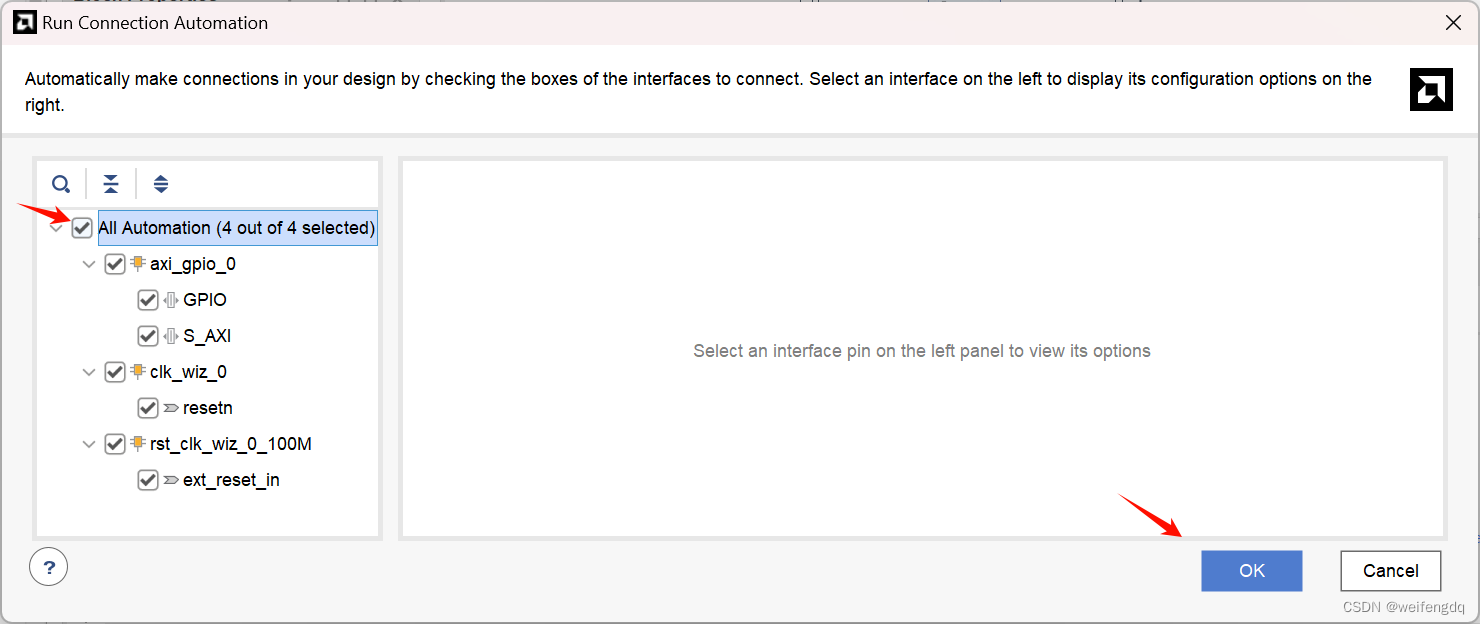

点 RunConnection Automation

全选

点 Regenerate Layout可以让排列规律一些

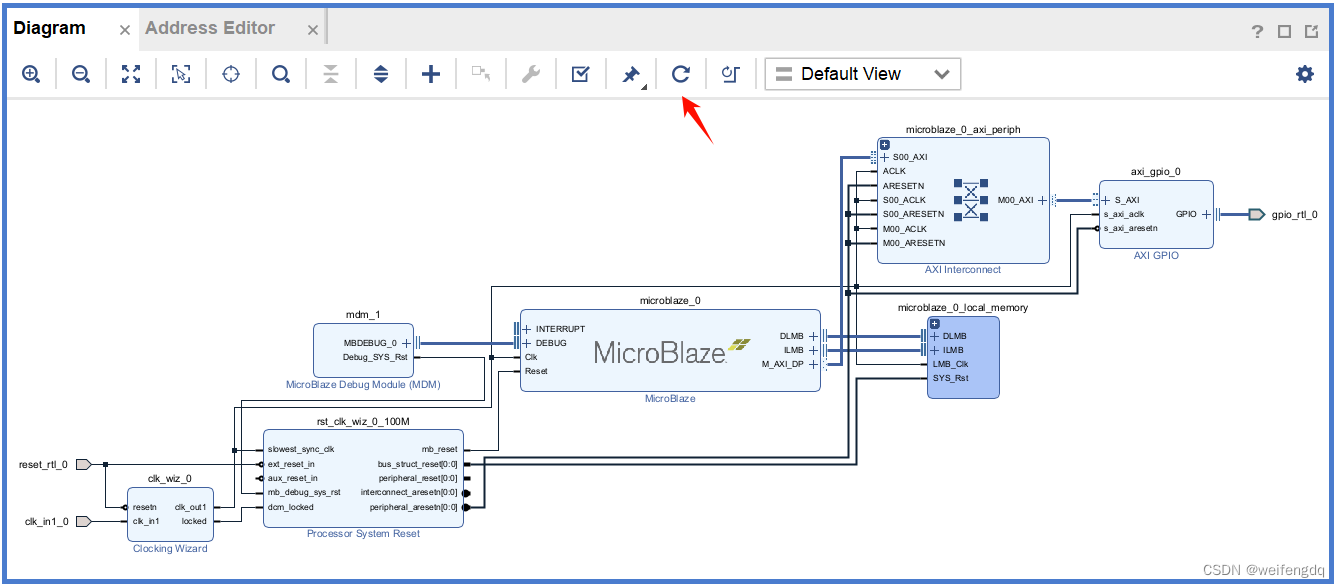

验证

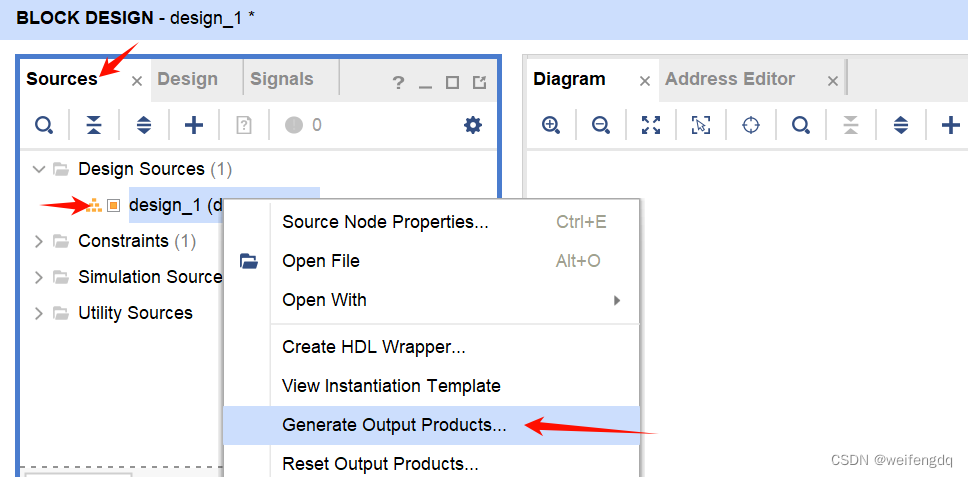

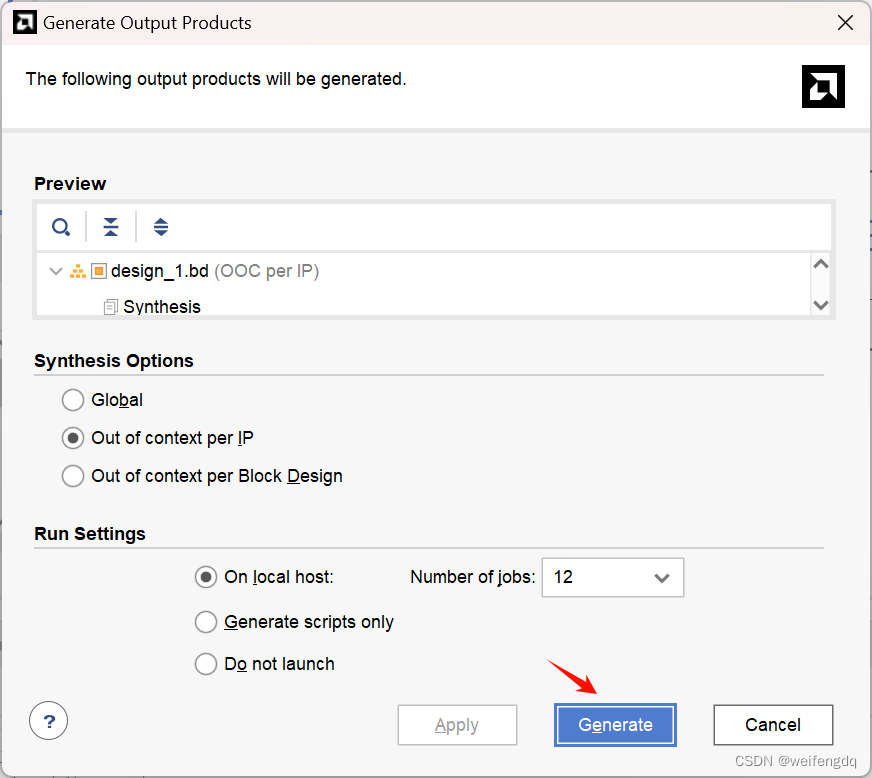

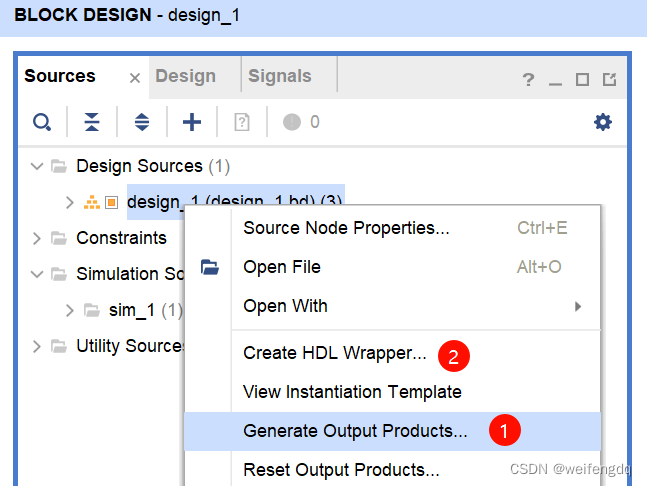

生成输出

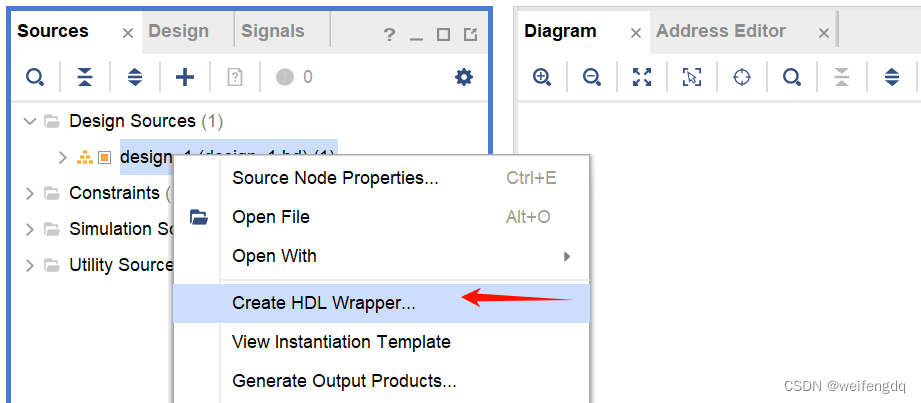

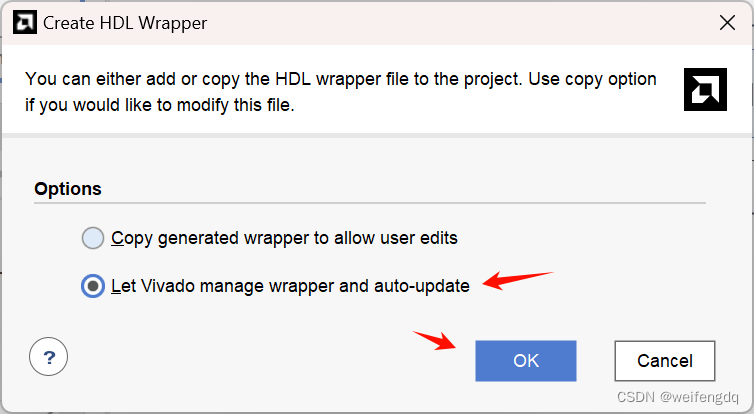

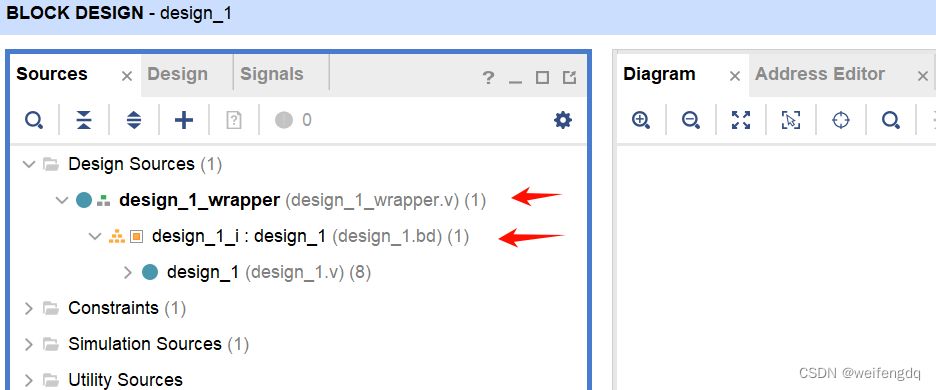

再包一层

变成这样了

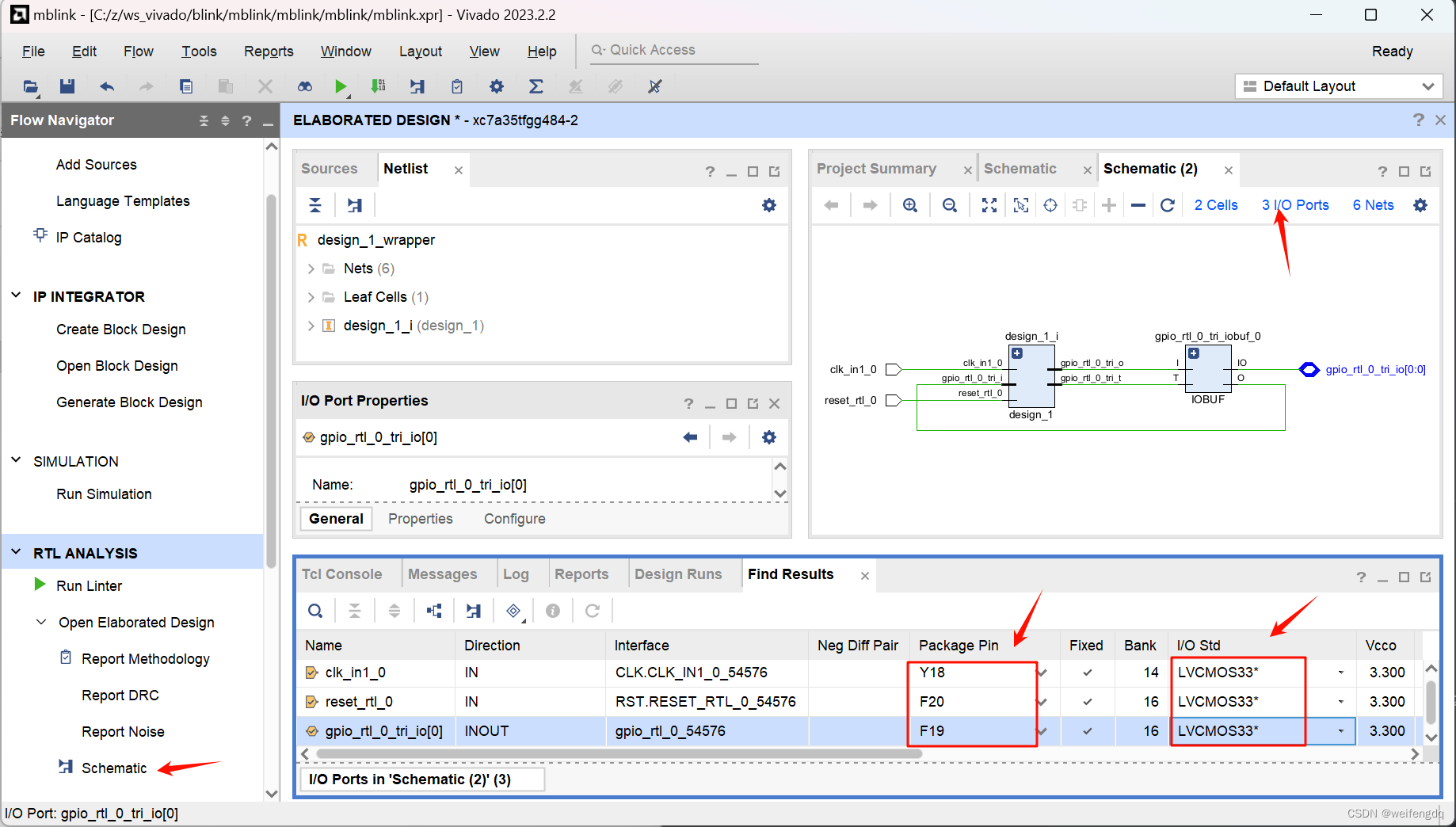

引脚分配好

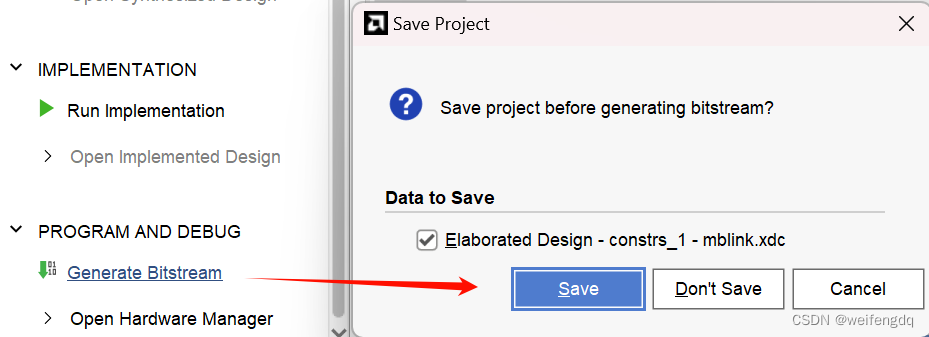

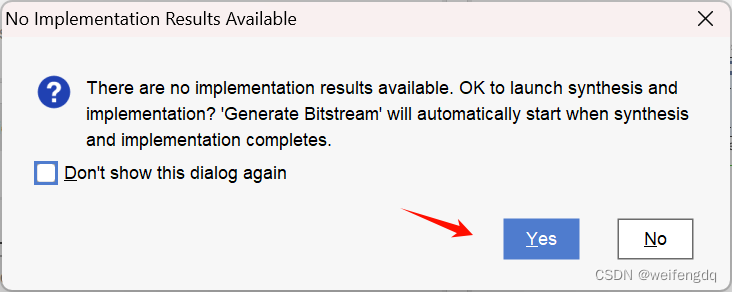

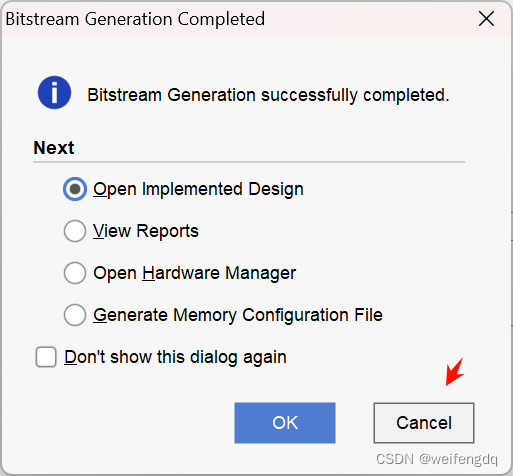

生成位流, 等待完成

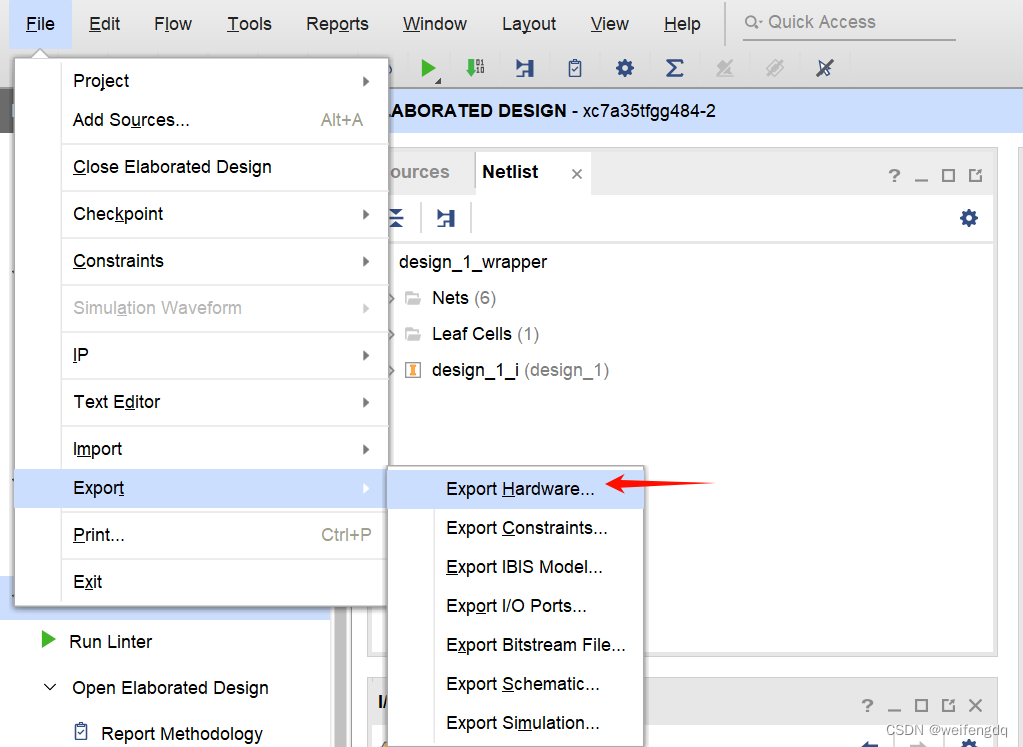

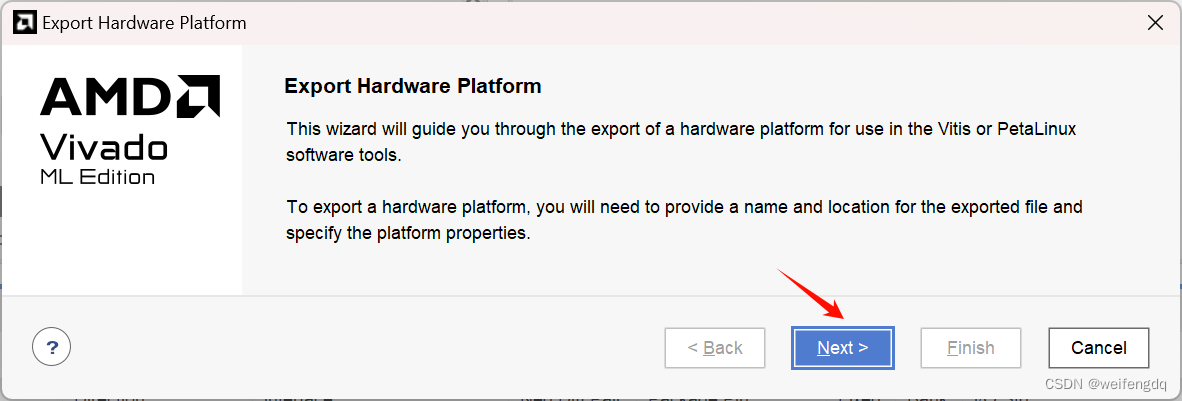

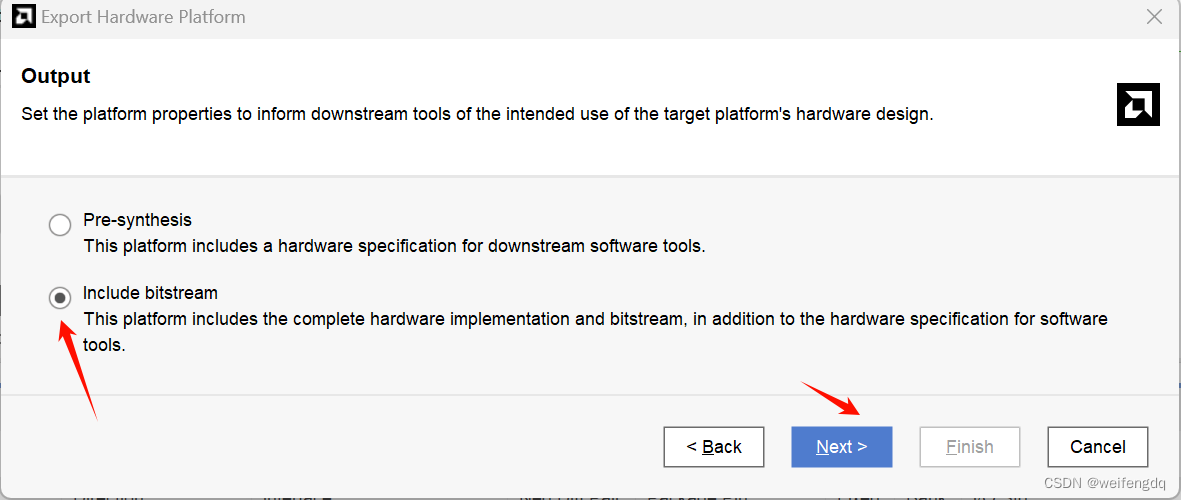

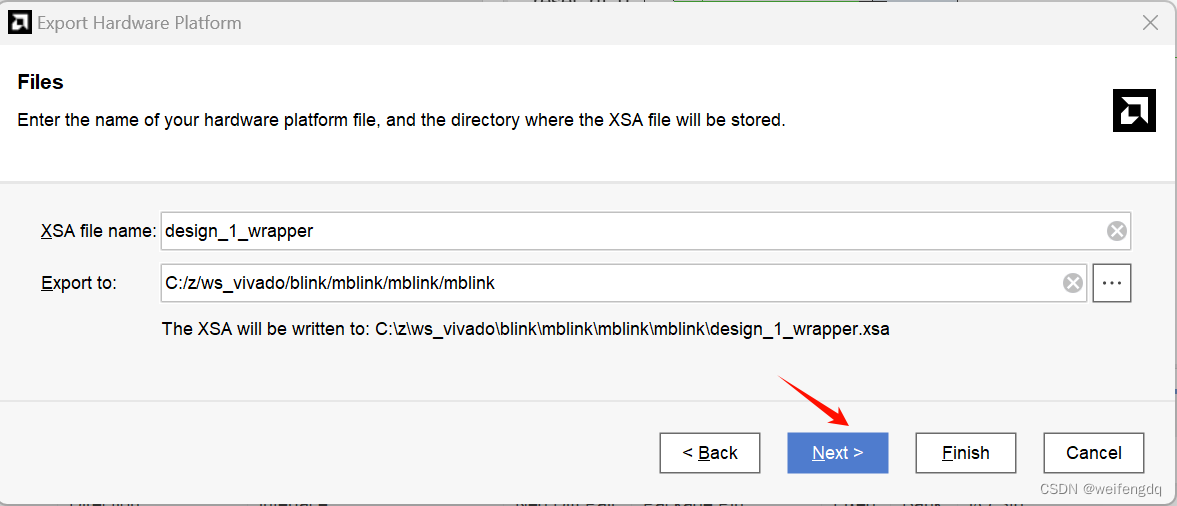

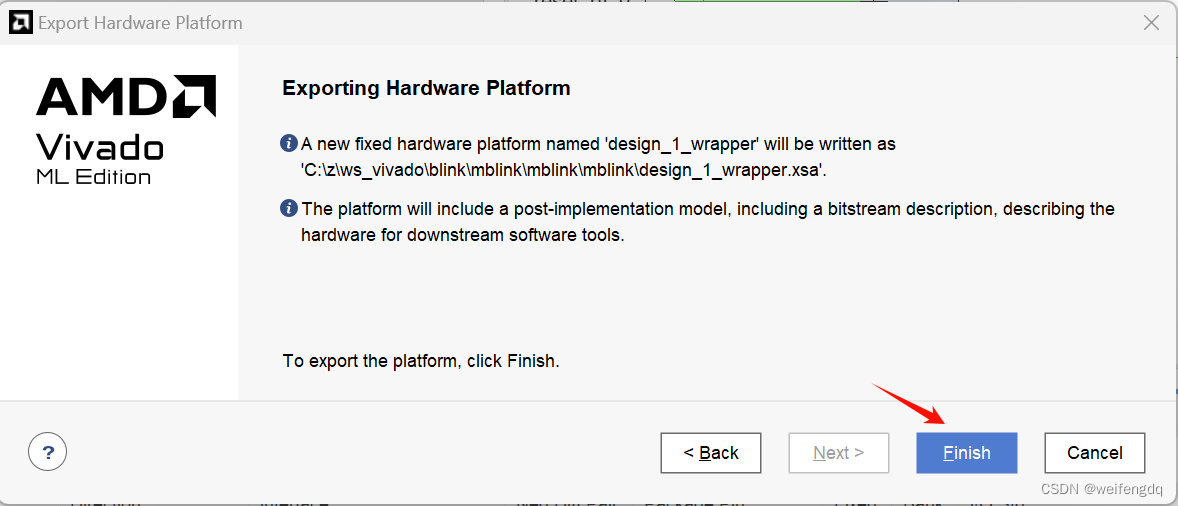

导出硬件 xsa 文件

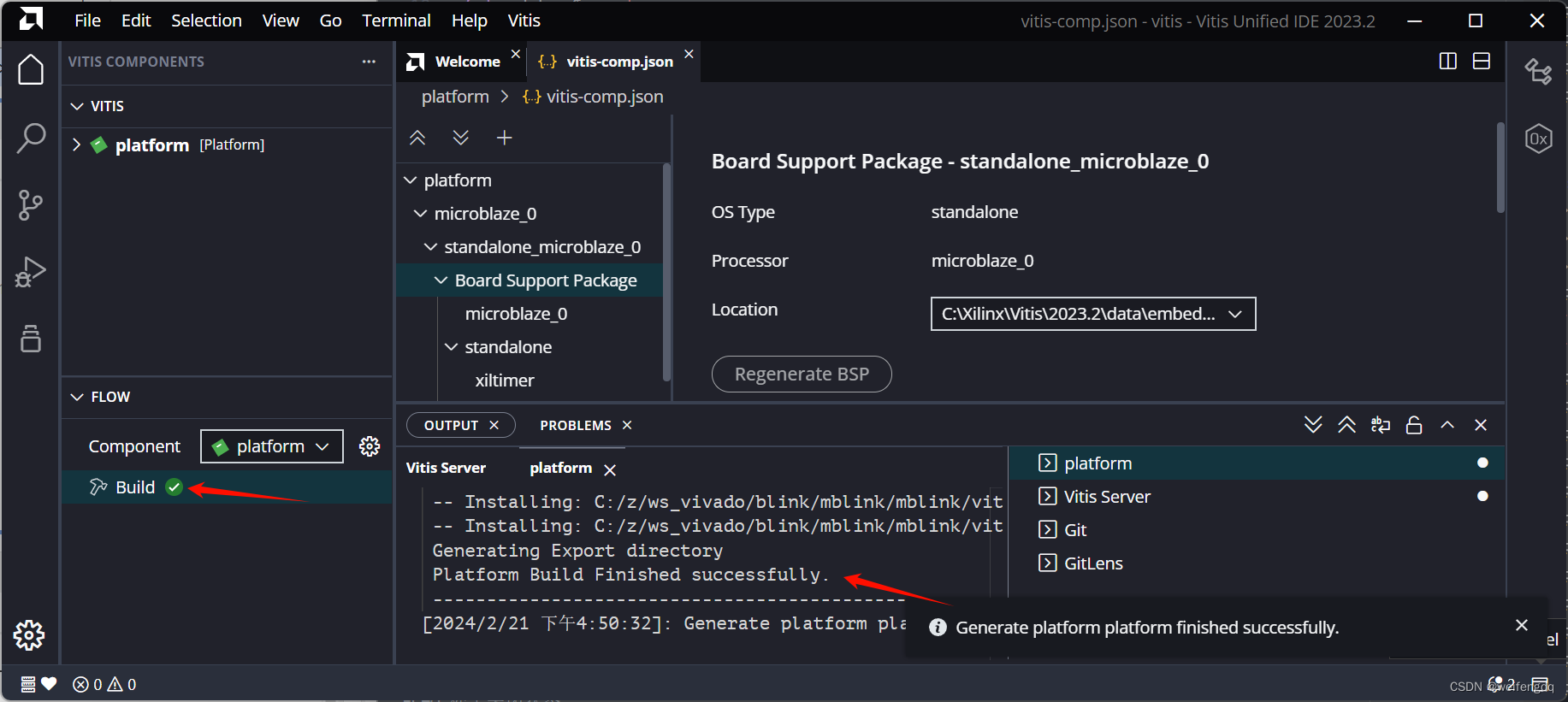

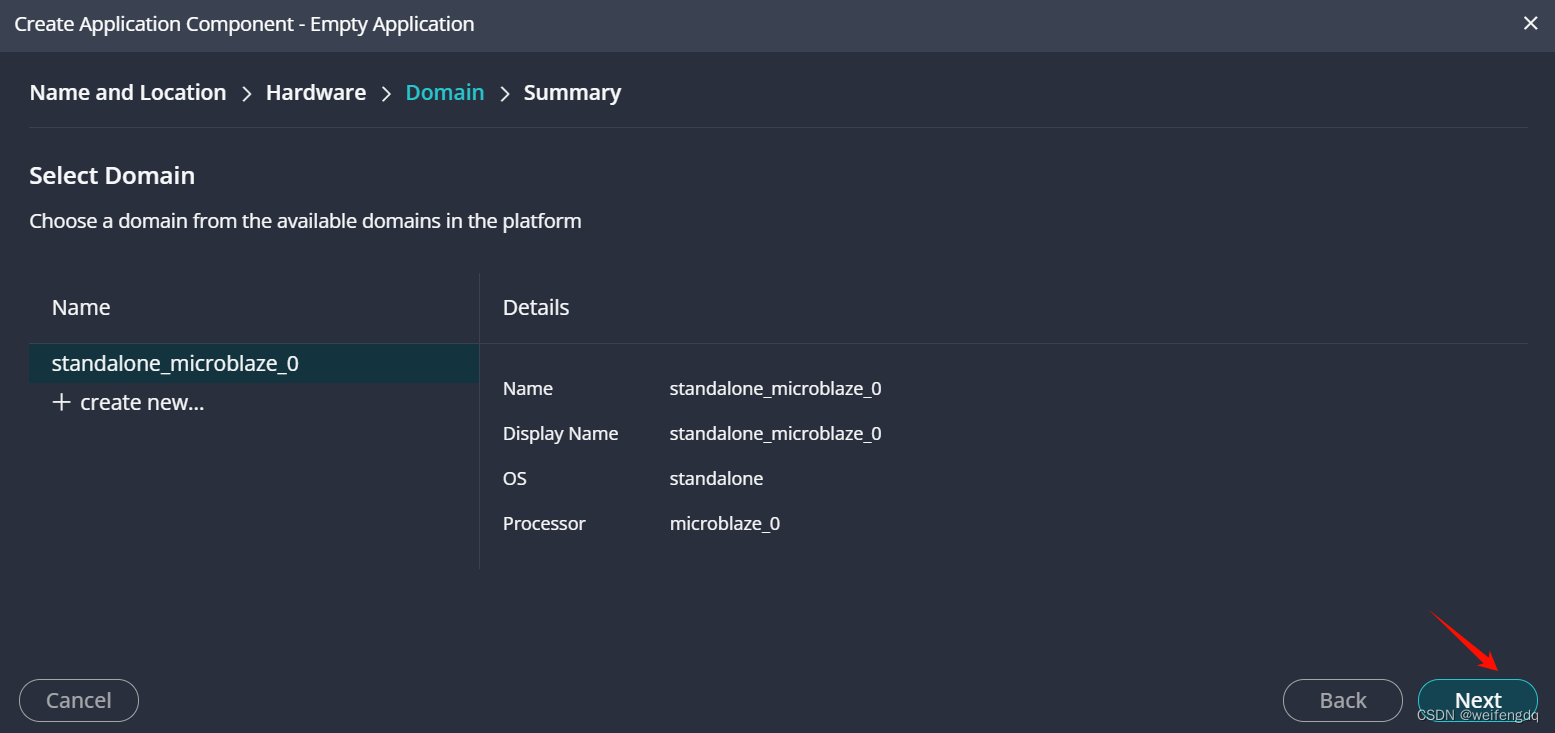

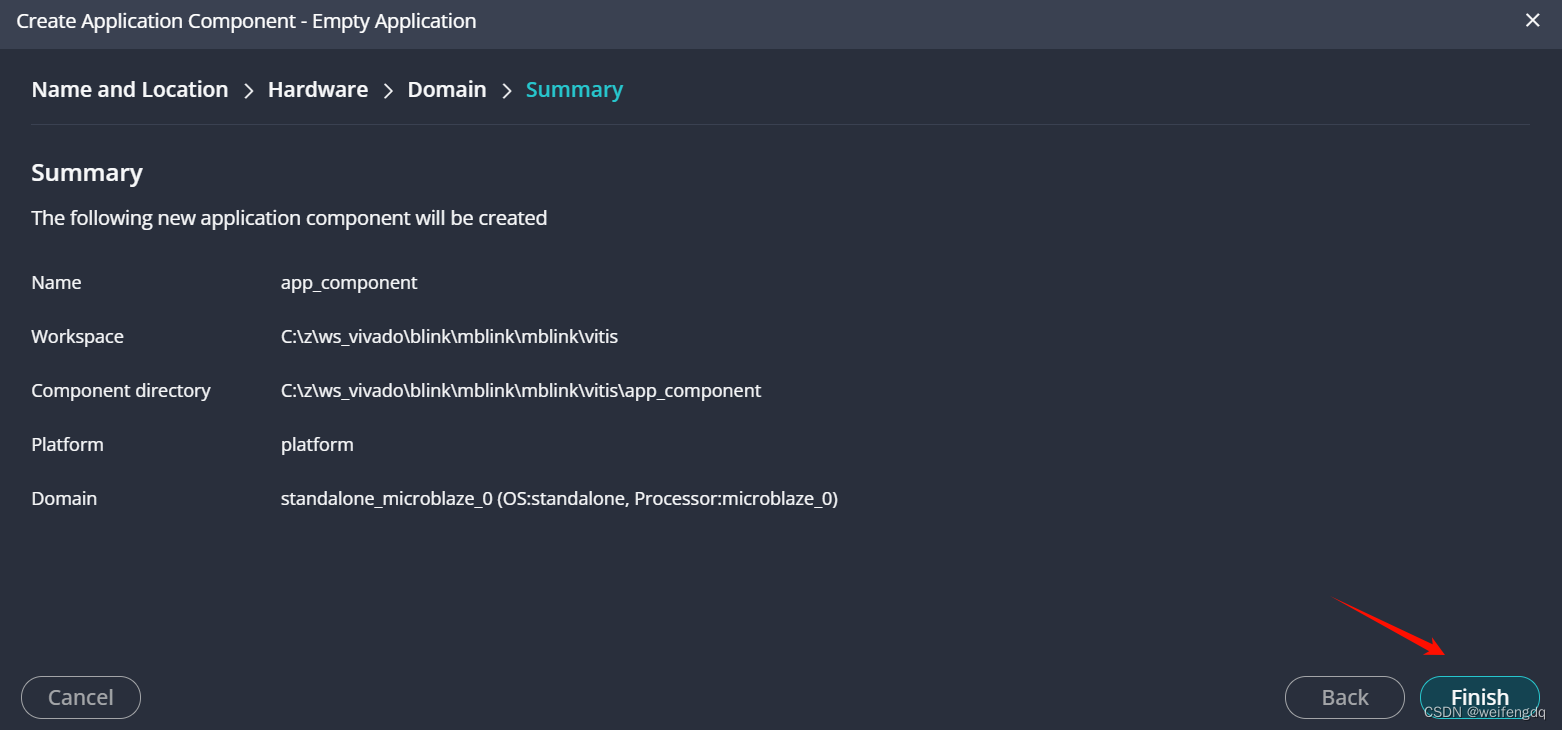

Vitis 2023.2 代码编写

新的Vitis和之前大不一样了:

- 界面变了, 从eclipse风格变成了VSCode风格, 操作不大一样

- SDK也变了,

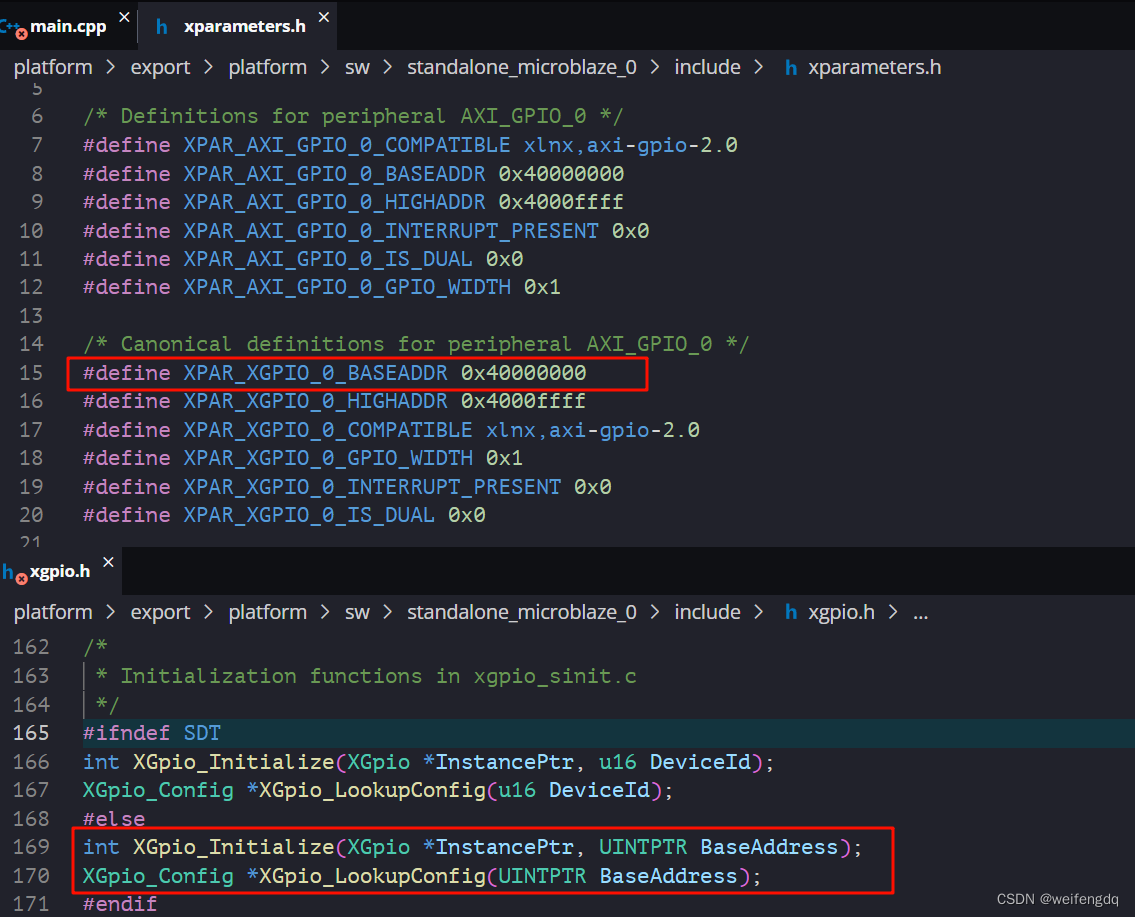

xparameters.h中 DEVICE_ID 现在成了 BASEADDR, 默认宏定义了 SDT, 如

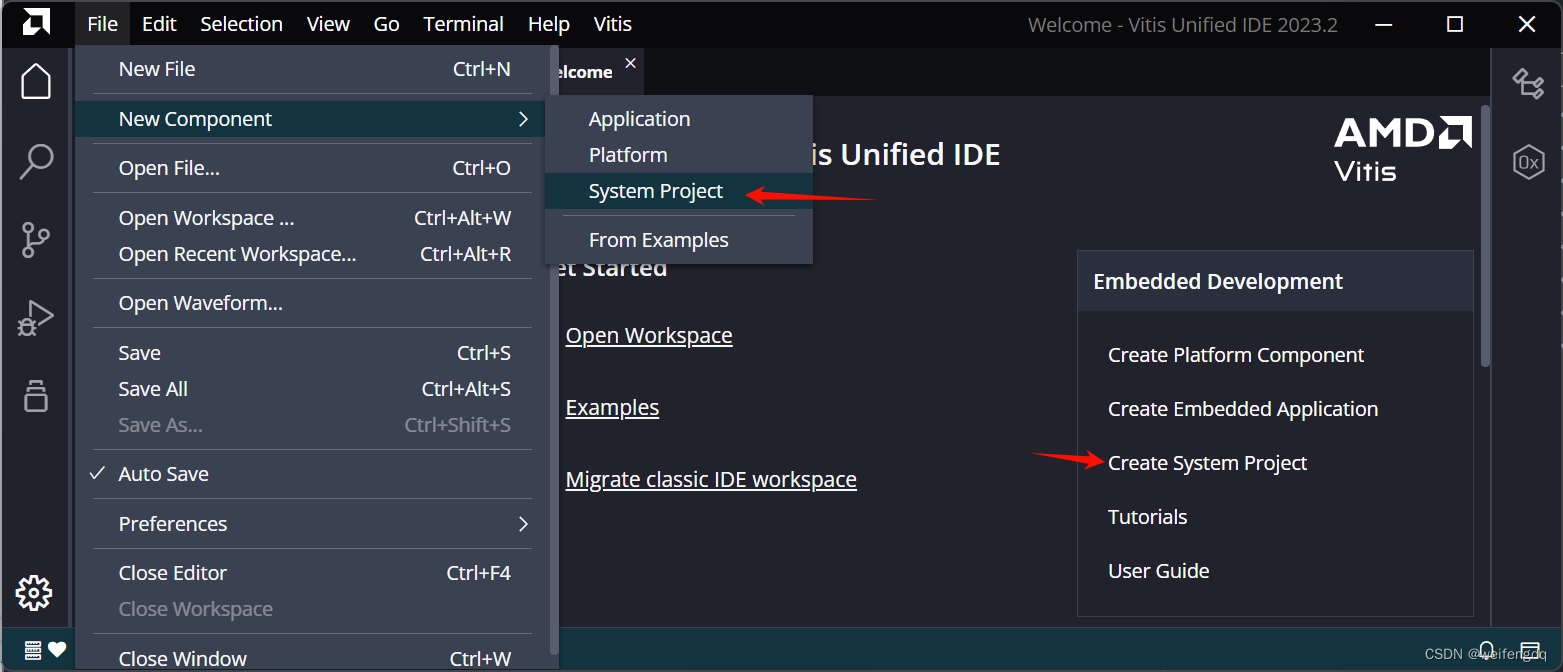

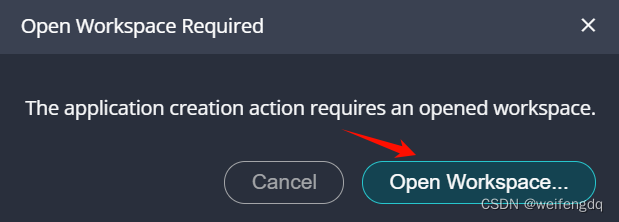

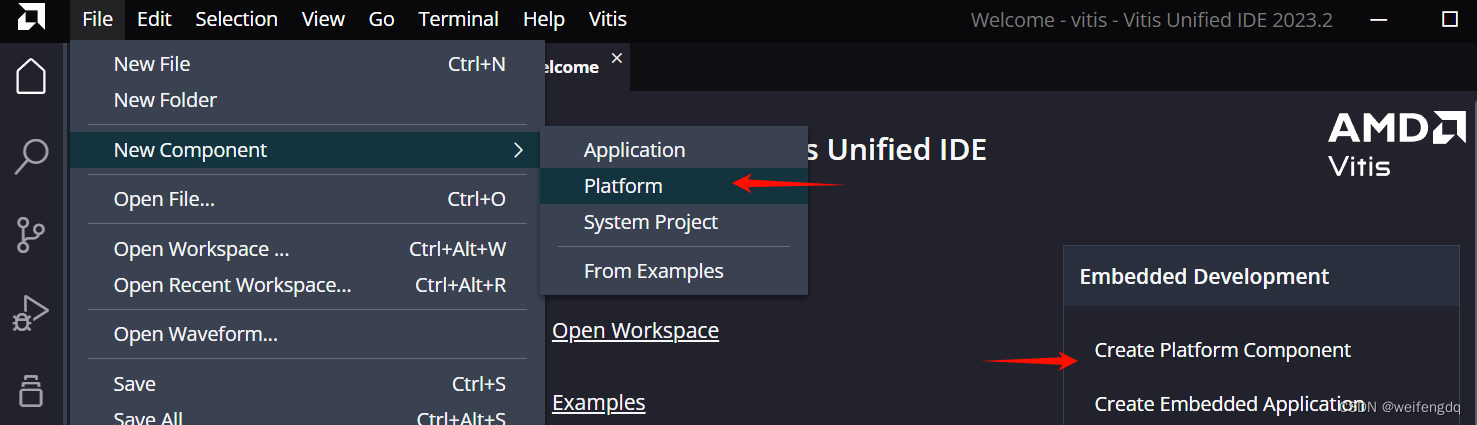

虽然可以通过 Tools -> Launch Vitis IDE 打开 Vitis 2023.2, 但这样会让Vivado变得不可用了. 所以还是直接找到Vitis 2023.2应用打开

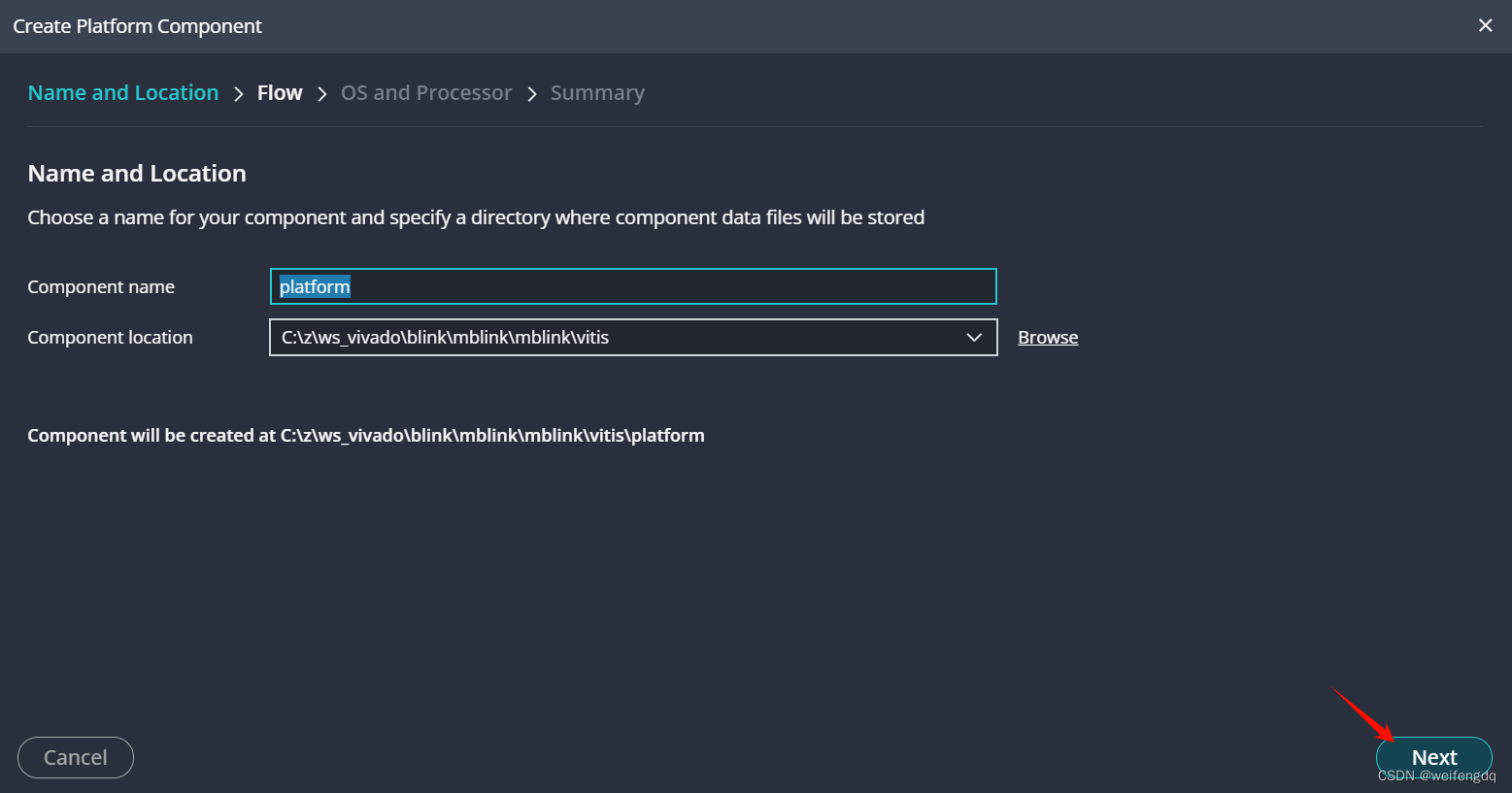

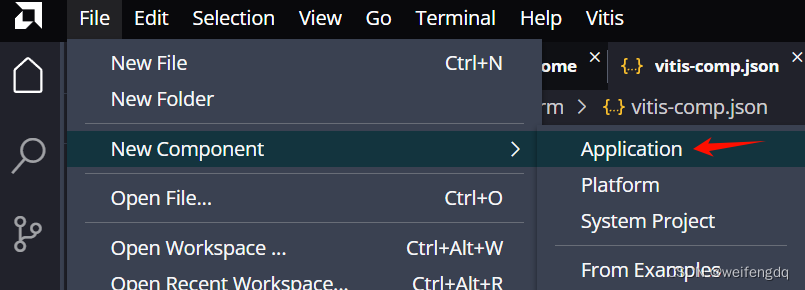

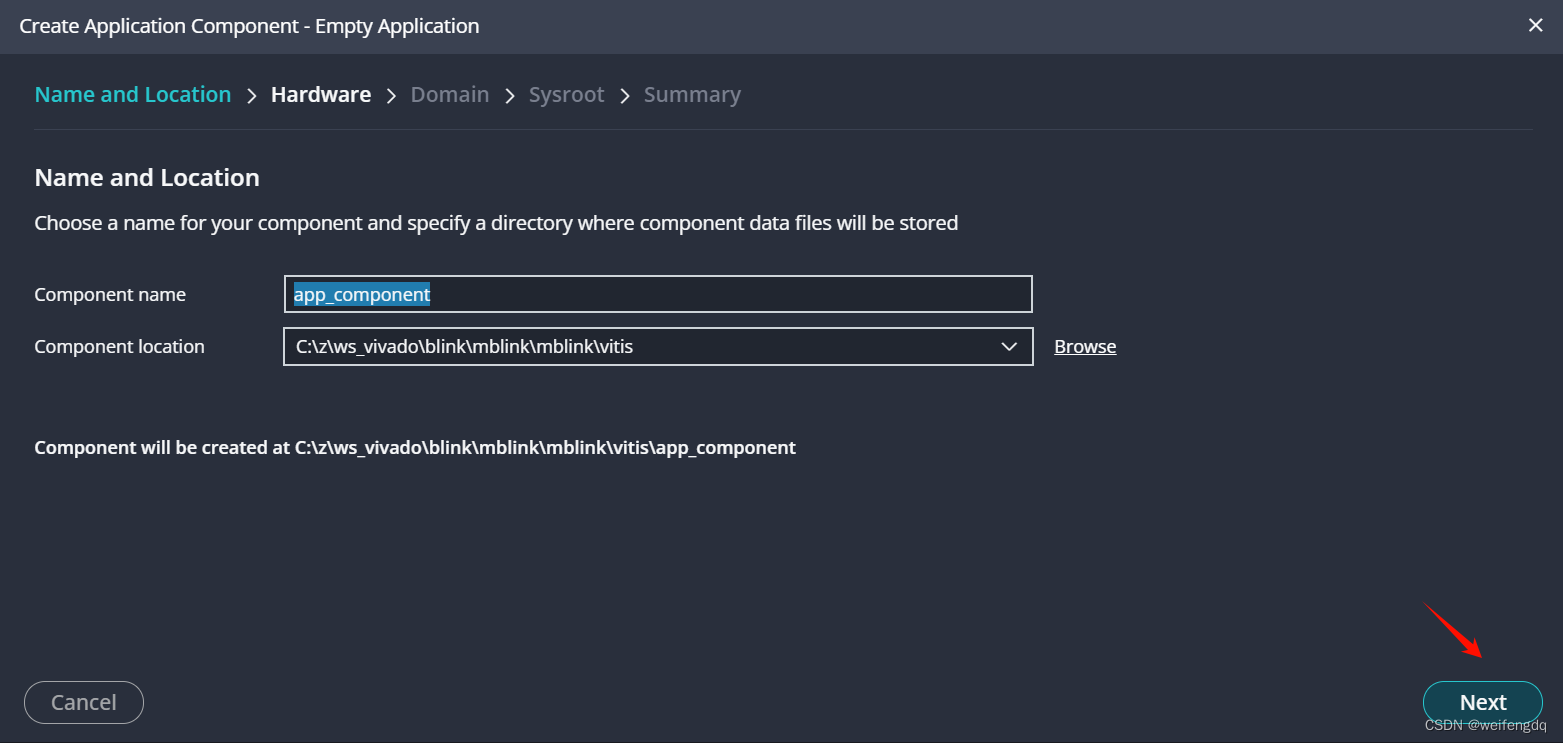

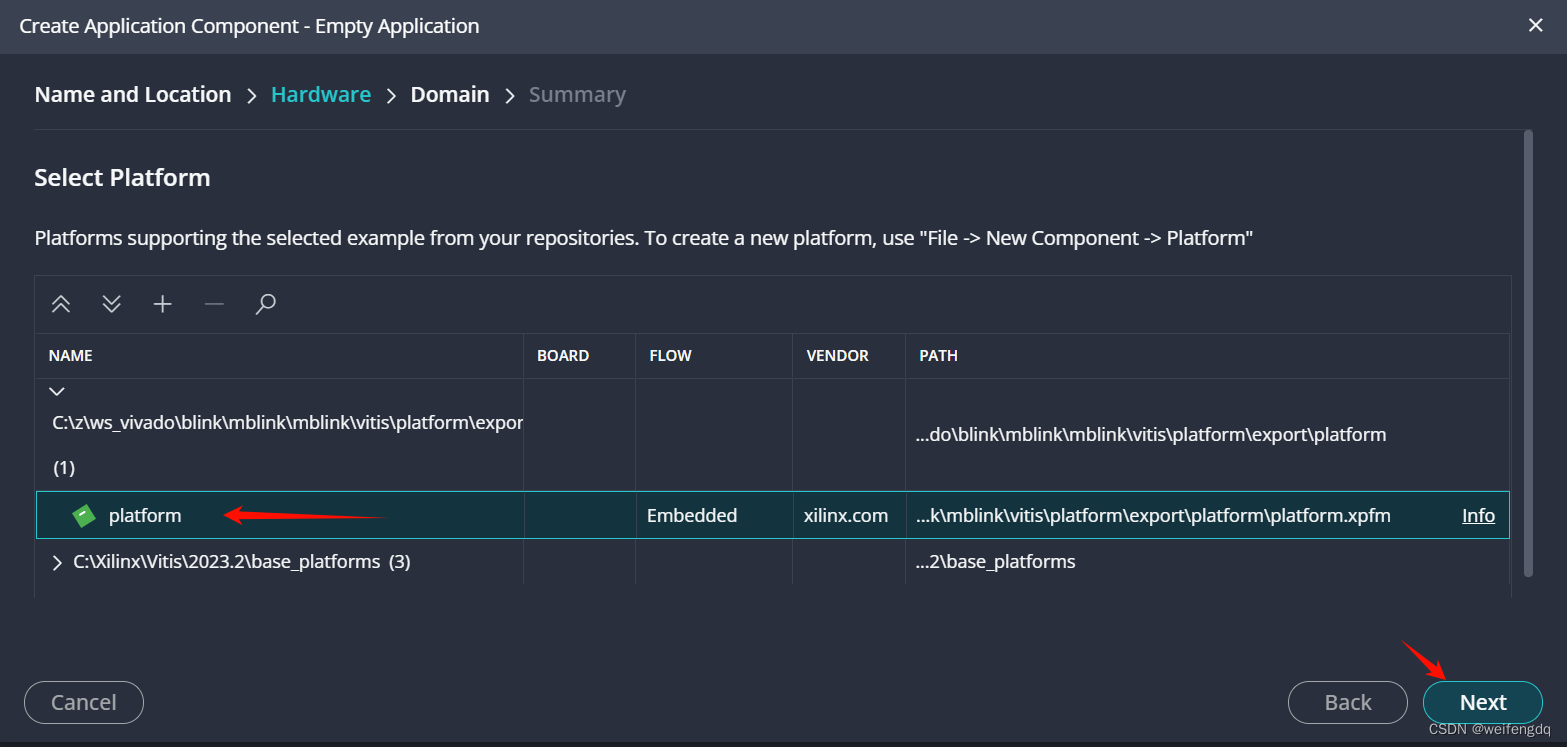

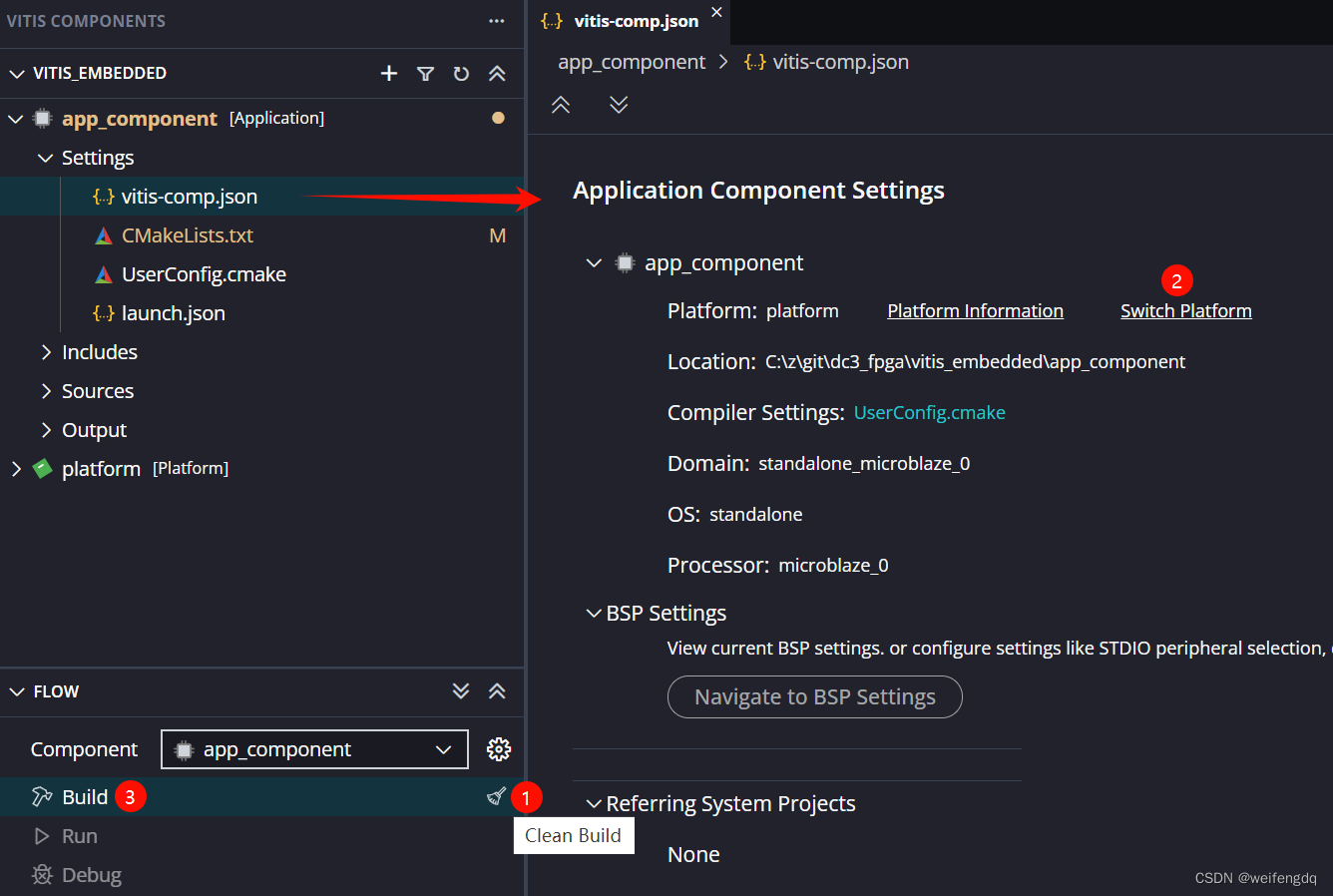

打开后是VSCode风格的界面, 接下来 选工程文件夹, XSA建Platform, Platform建App 三步走:

-

找个文件夹当Vitis工程文件夹, 直接点Open Workspace, 或者之前的

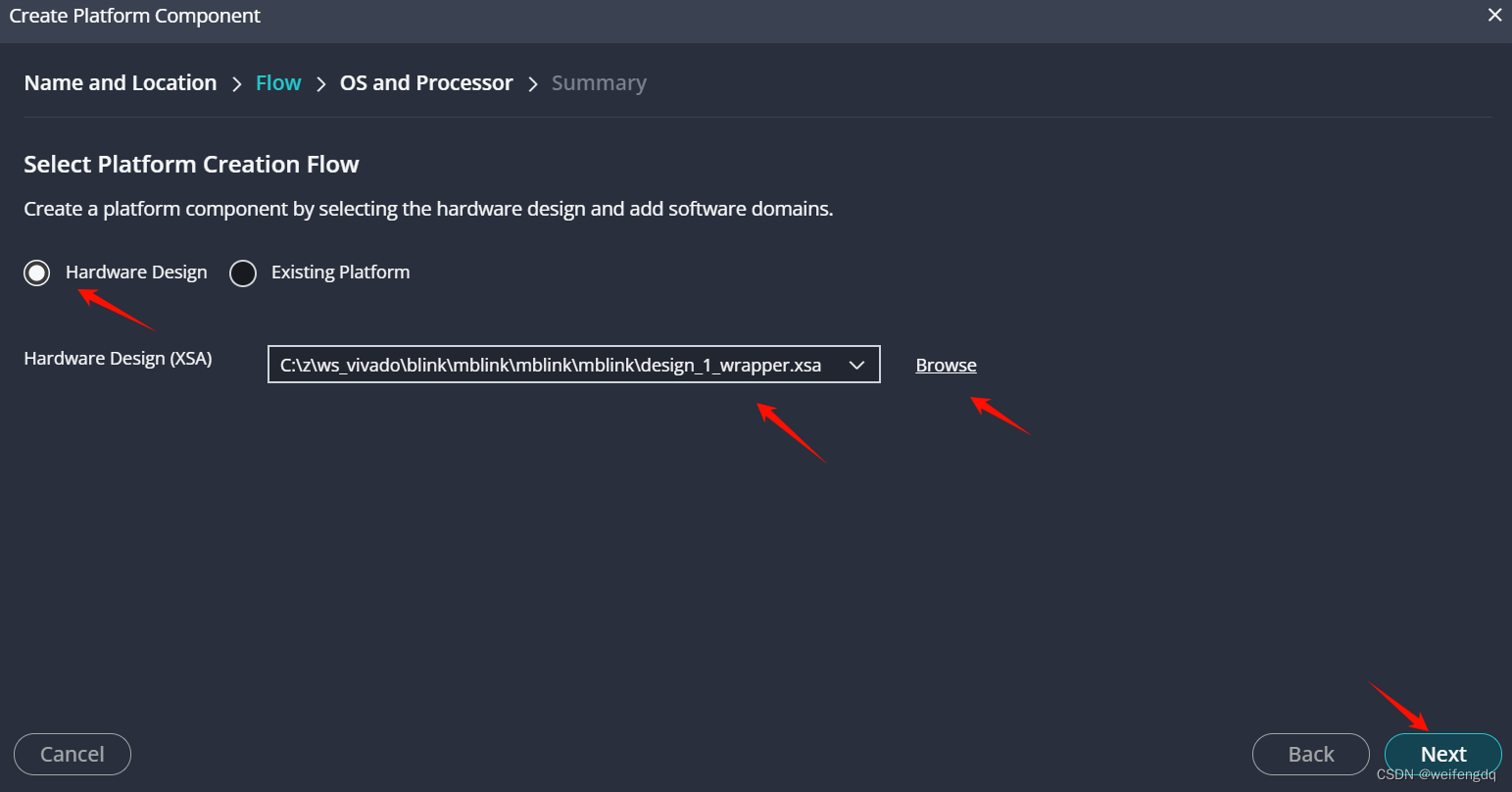

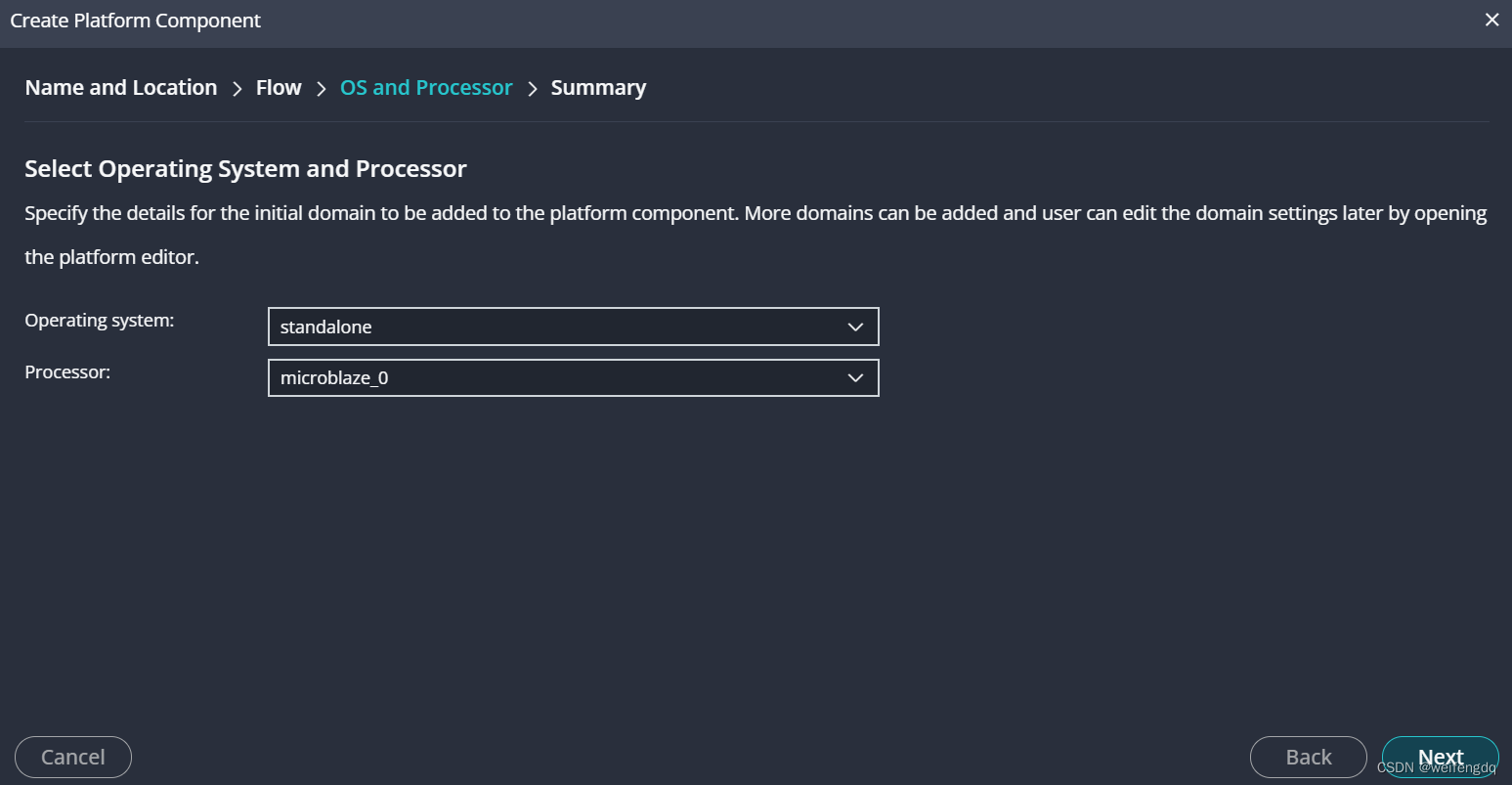

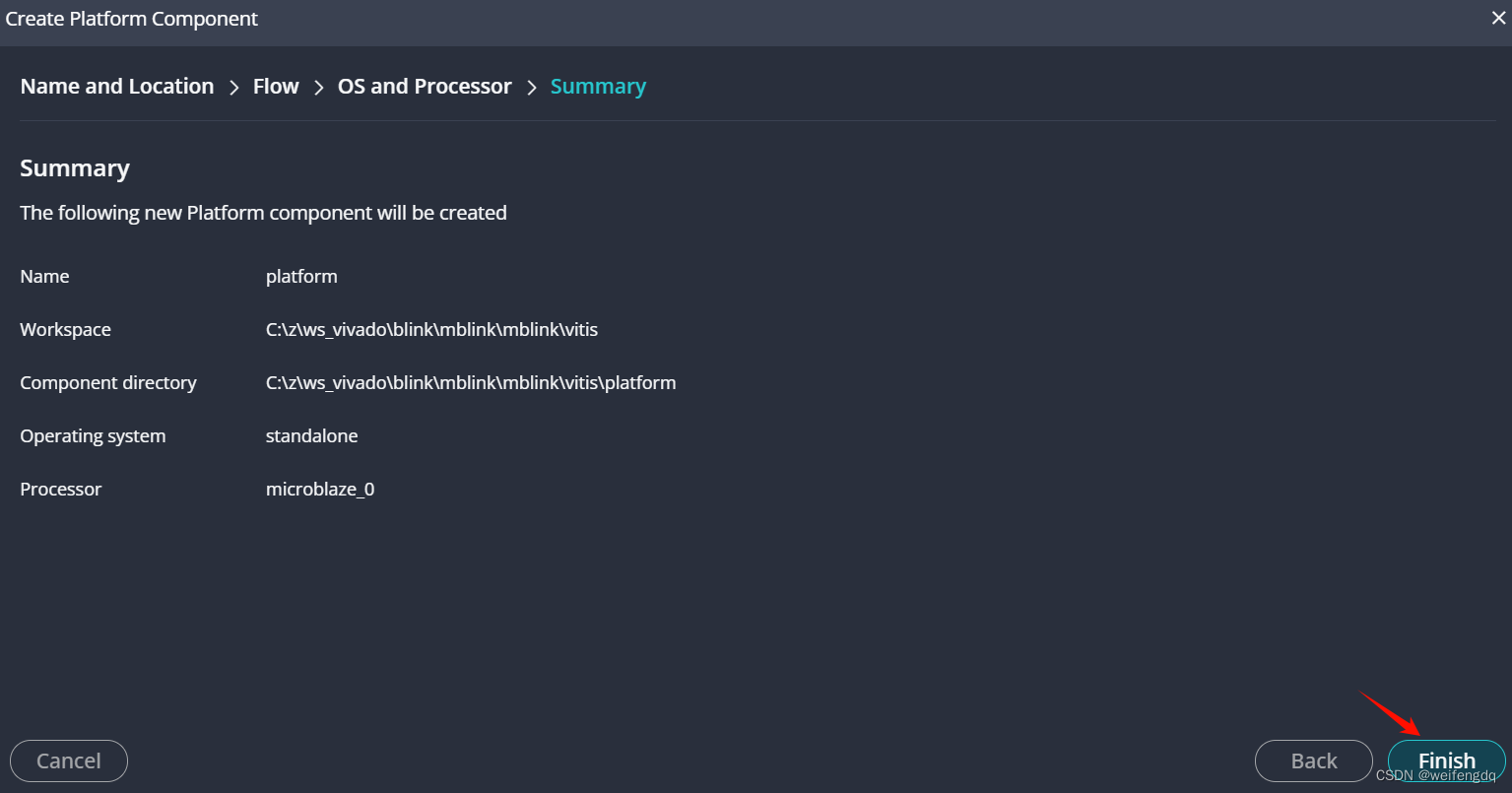

-

使用上面导出的xsa文件创建Platform Component, 然后编译一把, 生成BSP库

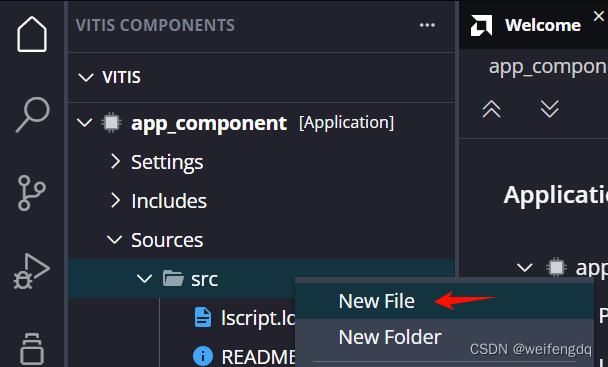

- 创建app, 使用上面的platform, 点灯

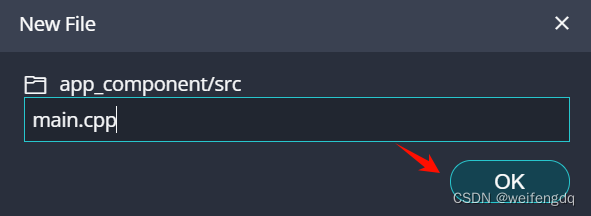

app_component - Sources - src 右键新建main.cpp文件

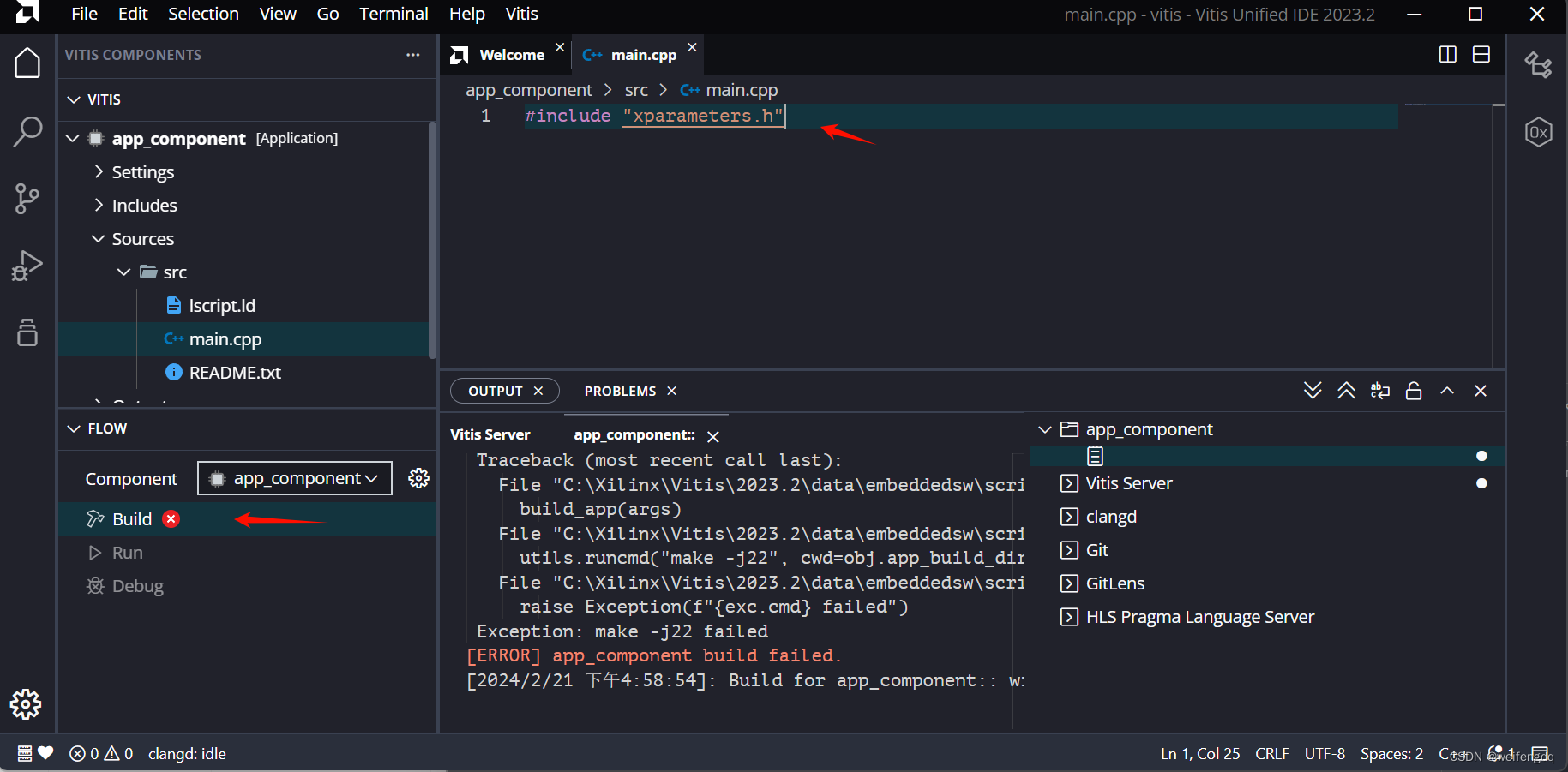

建完后写代码发现没有提示, 写出的头文件含波浪号, 对不对先Build一把

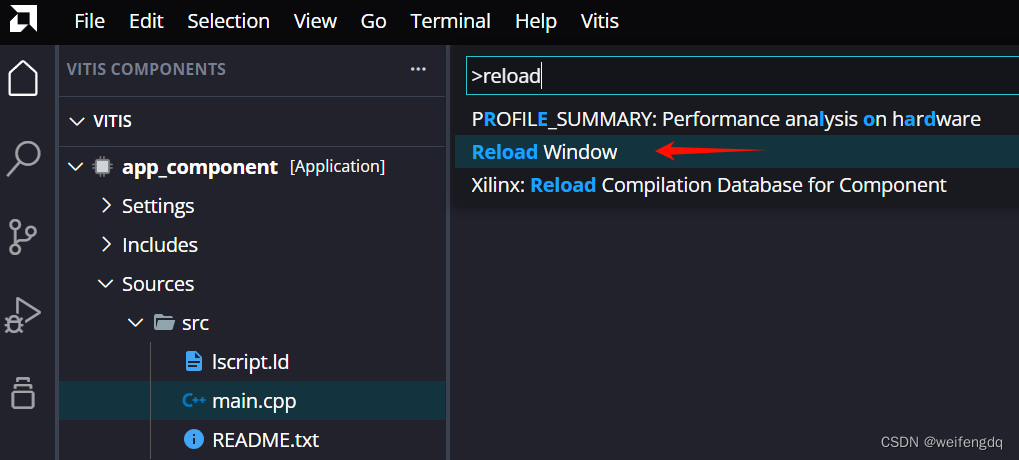

有时候新环境遇事不决 Ctrl+Shift+P, 然后Reload就对了

格式化代码和VSCode也一样, Alt+Shift+F

新的SDK里面找不到 DEVICE_ID 了, 统统换成了 BASEADDR

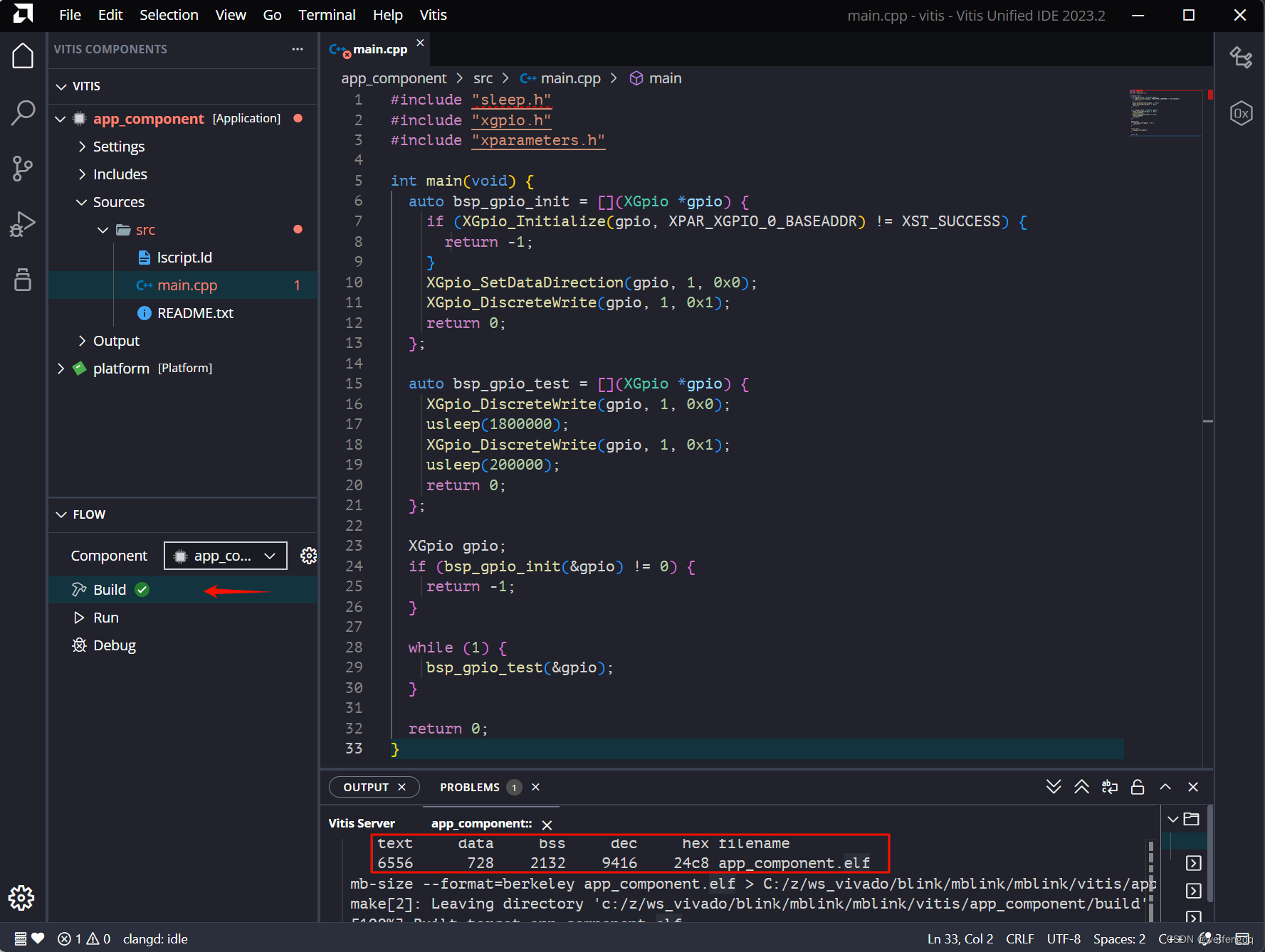

代码

- 支持常见的Cpp11/14操作如lambda, auto等

- 初始设置输出, 关闭LED

#include "sleep.h"

#include "xgpio.h"

#include "xparameters.h"int main(void) {auto bsp_gpio_init = [](XGpio *gpio) {if (XGpio_Initialize(gpio, XPAR_XGPIO_0_BASEADDR) != XST_SUCCESS) {return -1;}XGpio_SetDataDirection(gpio, 1, 0x0);XGpio_DiscreteWrite(gpio, 1, 0x1);return 0;};auto bsp_gpio_test = [](XGpio *gpio) {XGpio_DiscreteWrite(gpio, 1, 0x0);usleep(1800000);XGpio_DiscreteWrite(gpio, 1, 0x1);usleep(200000);return 0;};XGpio gpio;if (bsp_gpio_init(&gpio) != 0) {return -1;}while (1) {bsp_gpio_test(&gpio);}return 0;

}

编译

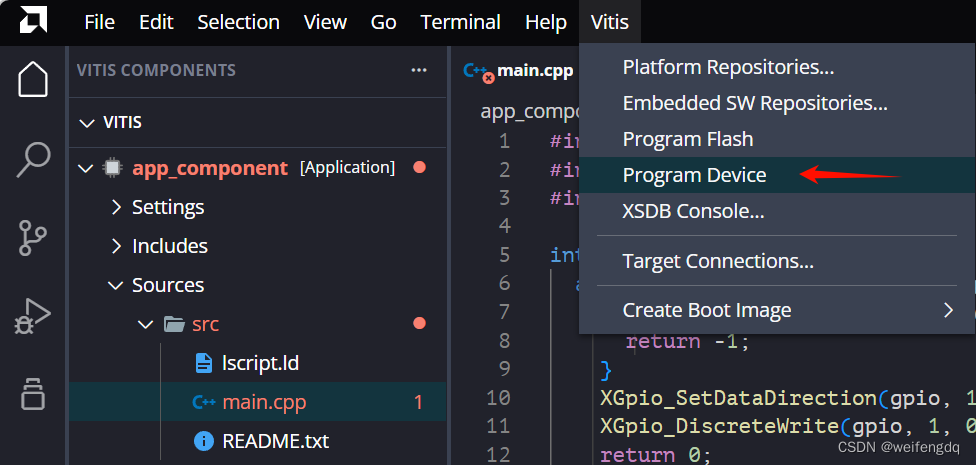

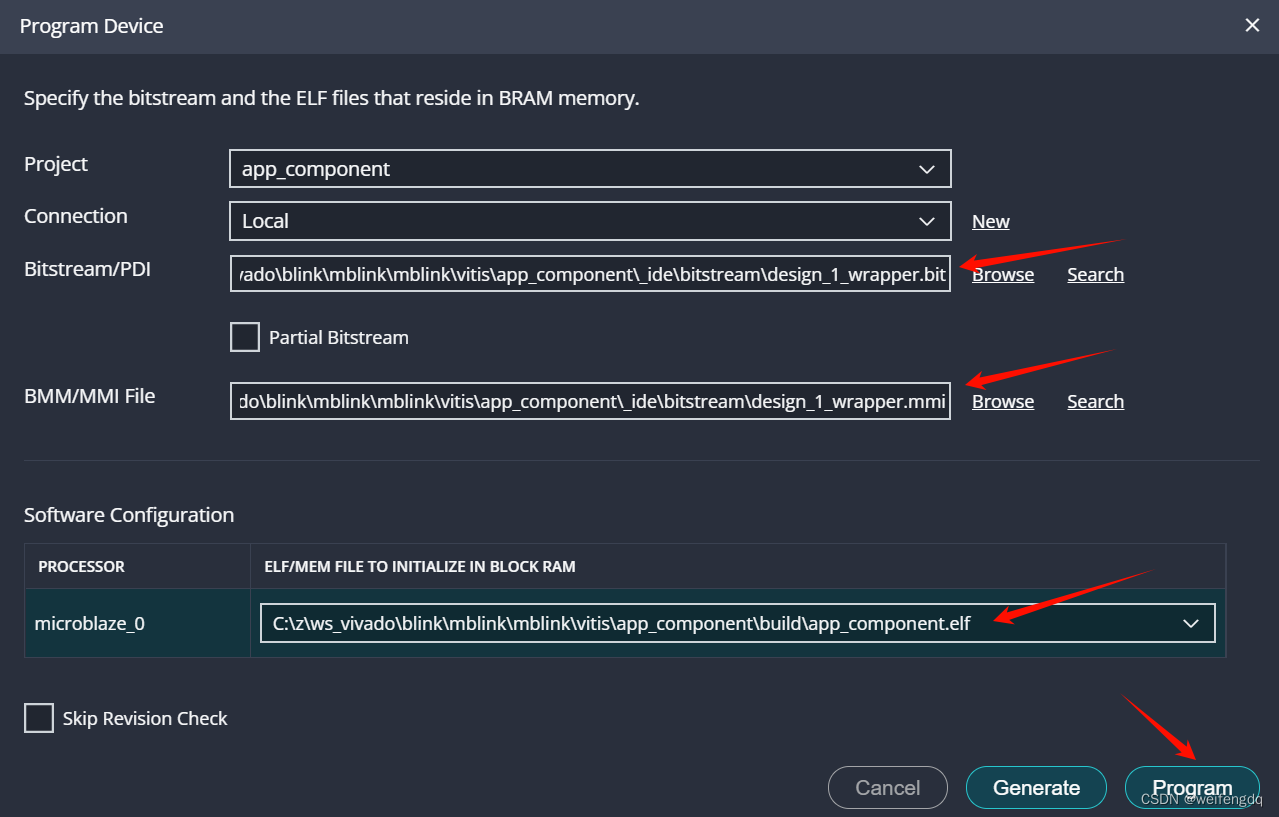

下载, 可以直接点Flow中的Run运行或者Debug调试(下次重开记得侧边栏Debug先Stop方块图标), 相当友好, 也可以按下图, 可以先点 Generate 再点 Program

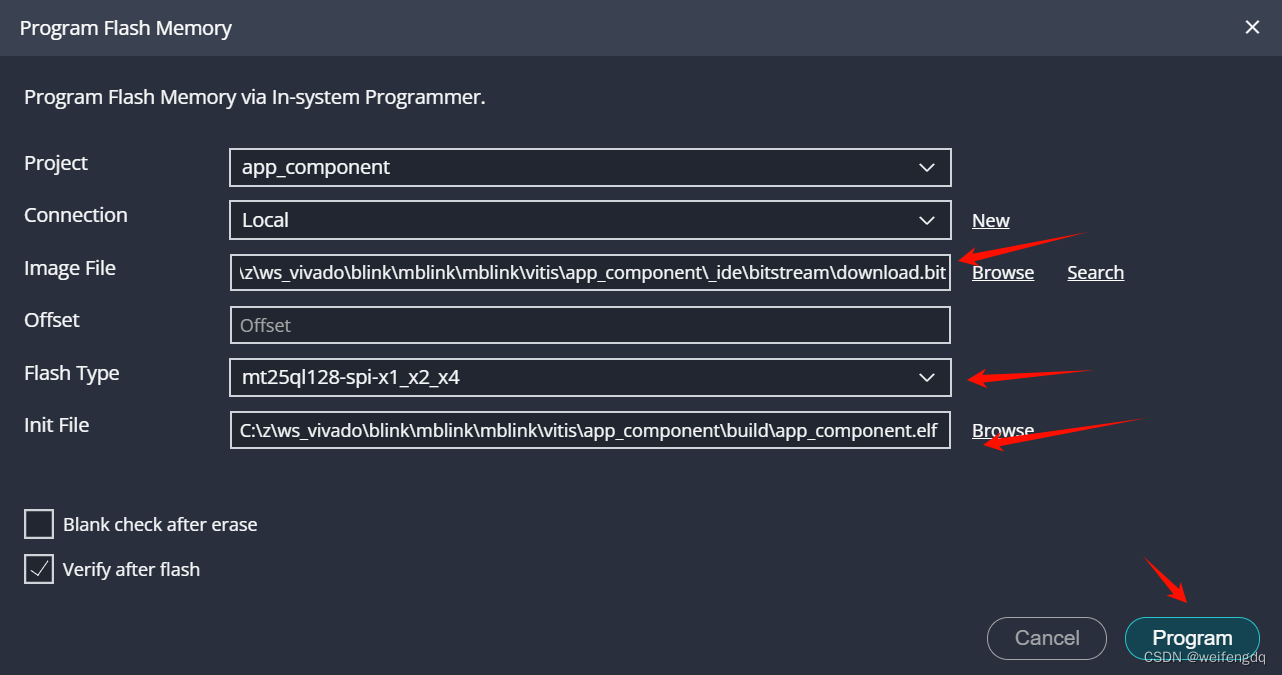

固化, 如果只是Vivado Verilog开发全部工程, 自然是在Vivado中固化, 如果是Vivado IP连连, 主要在Vitis开发, 那是要在Vitis固化

重新上电, 会发现启动比较慢(近10s), 是因为 Vivado 的XDC约束文件里忘记加SPI的配置了

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

需要:

- Vivado重新生成 Bitstream

- 替换

工程.runs\impl_1\design_1_wrapper.bit到 vitis 的vitis\app_component\_ide\bitstream\design_1_wrapper.bit - Vitis -> Program Device -> Generate按钮生成download.bit文件

- Vitis -> Program Flash 重新固化

重新上电, 发现启动速度正常了

注意:

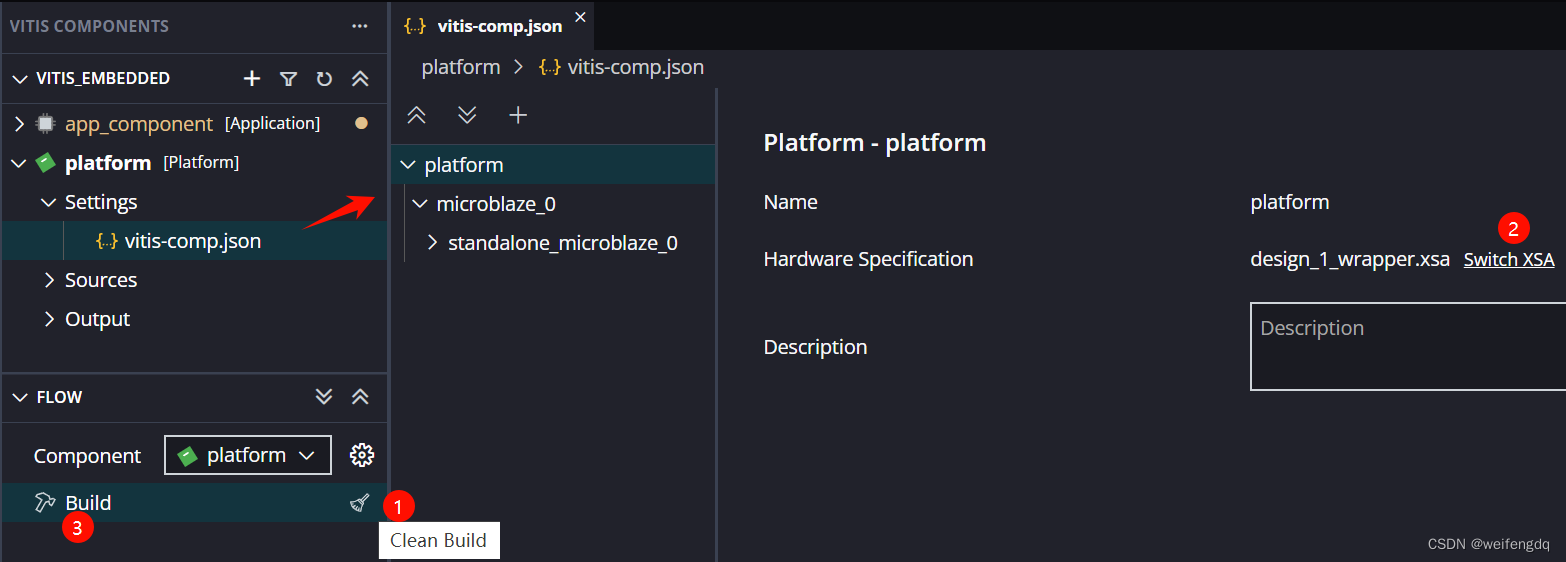

- 如果Vivado添加了新的IP, 如增加了Uart等, 那BSP肯定要跟着变的, 需要重新导出XSA文件, 在Vitis中删掉Platform重新从XSA建Platform并编译(或者如下图 1Clean, 2Switch XSA, 3Build), 然后APP工程需要先清理(或者直接删除Output所有文件)再编译, 必要时重载窗口. vivado工程的bit文件和mmi文件也要拷贝到

<vitits embedded prj>\_ide\bitstream目录下 - 文件爆炸式增长, 工程的Git管理还需要实际测试一下

Vitis HLS 自定义IP Blink

HLS: High-Level Synthesis, 高层次综合是一种将算法级或行为级描述转化为硬件描述语言(如Verilog或VHDL)

的过程,这种语言可以用于FPGA或ASIC的设计。这使得设计人员可以在更高的抽象级别上进行设计,从而提高设计效率并减少错误。一些有用的链接:

- 官网 Vitis HLS (xilinx.com), Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。

- 用户指南: Vitis 高层次综合用户指南 (UG1399)

- Vitis HLS 简介示例 (https://github.com/Xilinx/Vitis-HLS-Introductory-Examples)

- Vitis 加速示例仓库 (https://github.com/Xilinx/Vitis_Accel_Examples)

- Vitis 应用加速开发流程教程 (https://github.com/Xilinx/Vitis-Tutorials)

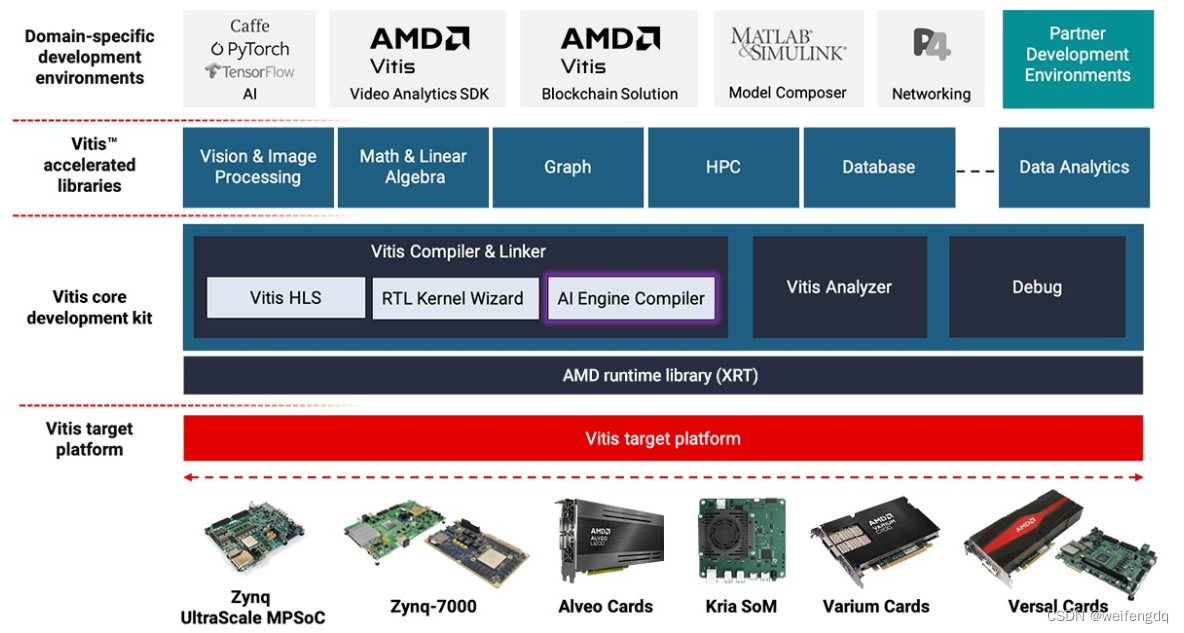

官方文档2023版其实已经把所有软件开发大一统到了 Vitis Unified IDE(Vitis 统一软件平台), 即便打开Vitis HLS, 也会提示最好迁移到 Vitis Unified IDE

官方的界面

不知是哪里出了问题(网络问题?), Vitis Unified IDE 里面没有找到上图中红色箭头的 HLS Component, 只有上图中绿色箭头的Embedded Development能用. 这里用老的 Vitis HLS 也问题不大.

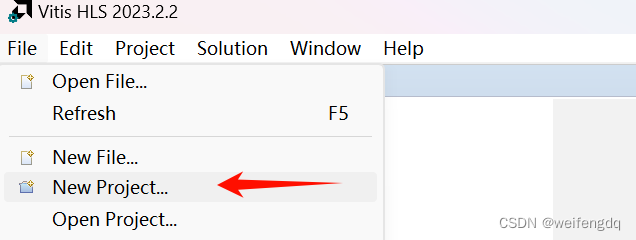

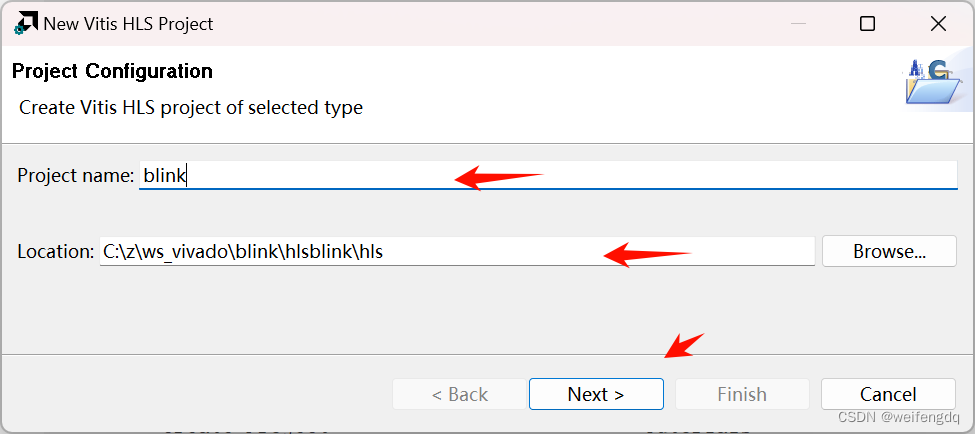

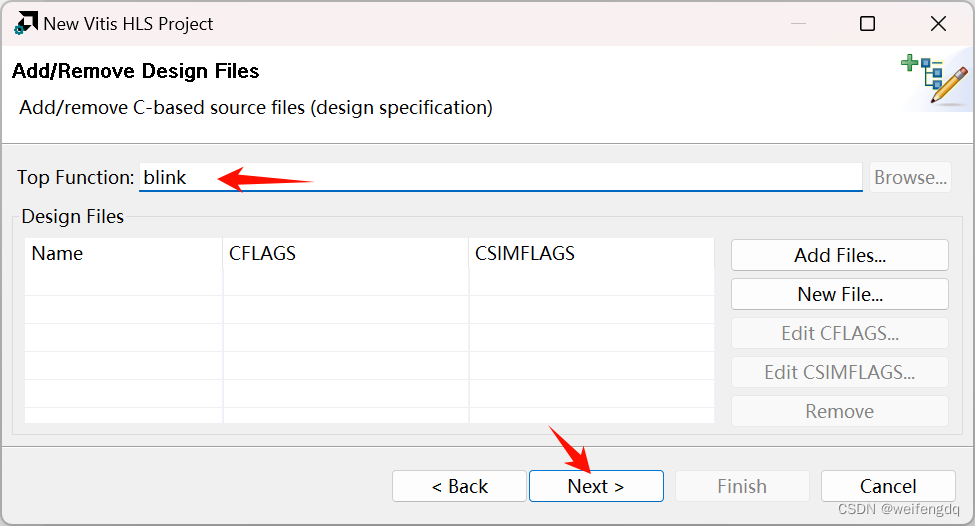

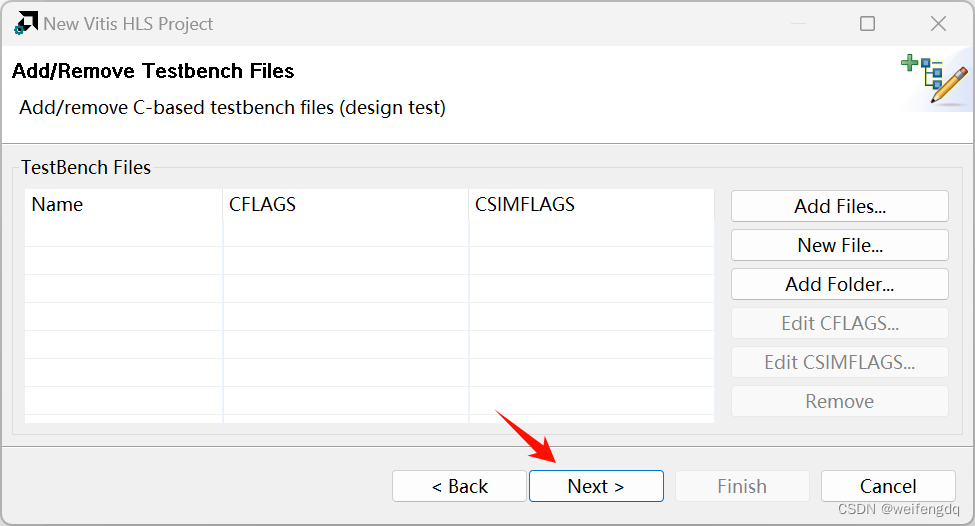

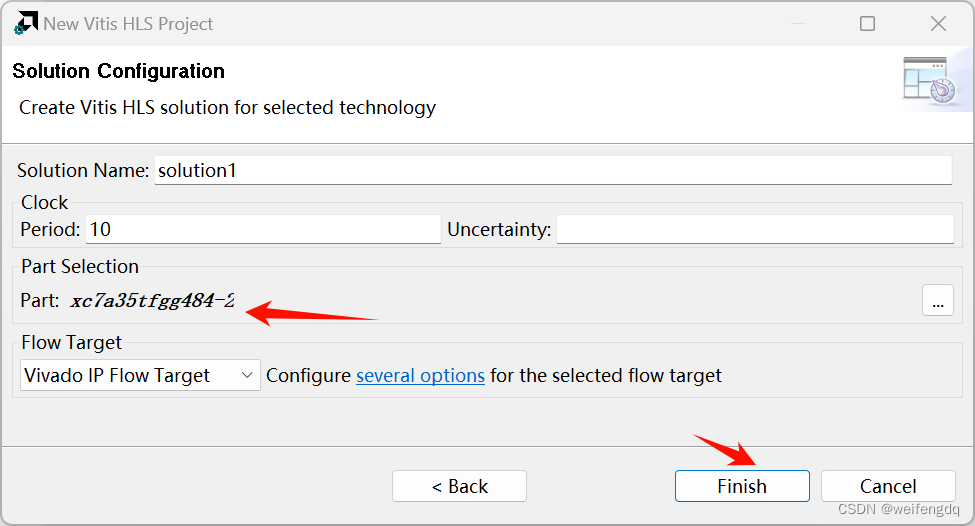

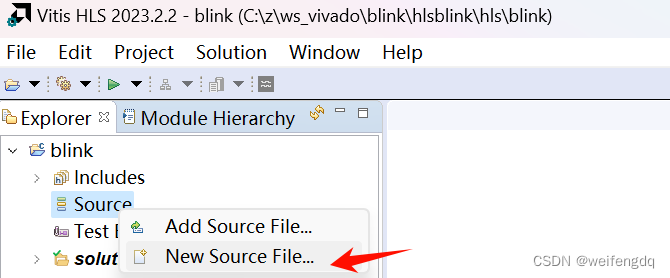

Vitis HLS 2023.2 GUI操作

打开 Vitis HLS 2023.2

代码(这里按100MHz写)

#include "ap_int.h"void blink(ap_uint<1> &led) {

#pragma HLS INTERFACE mode=ap_ctrl_none port=returnstatic ap_uint<32> counter = 0;if (counter < 180000000) {led = 0;} else if (counter < 200000000) {led = 1;} else {counter = 0;}counter++;

}

如果非写成class也可以

#include "ap_int.h"class Blinker {

public:Blinker() : counter(0) {}void blink(ap_uint<1> &led) {counter++;if (counter < 180000000) {led = 0; // LED on} else if (counter < 200000000) {led = 1; // LED off} else {counter = 0;}}private: ap_uint<32> counter;

};void blink(ap_uint<1> &led) {

#pragma HLS INTERFACE mode = ap_ctrl_none port = returnstatic Blinker blinker;blinker.blink(led);

}

说明:

- 要有一个函数名对应上上面图中的 Top Function, 这里是blink

#pragma HLS INTERFACE mode = ap_ctrl_none port = return是去掉状态控制(不然会多start等控制引脚), 可以在图形界面 Directive 插入这种指令, 这里直接填进去了- 如果写 led=!led, 会出现输入输出都有led引脚的情况, 不建议这么写

- 可以在测试文件中写main函数测试, 这里略

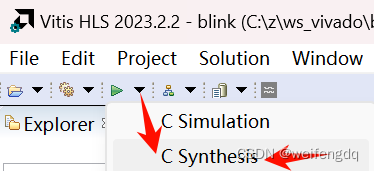

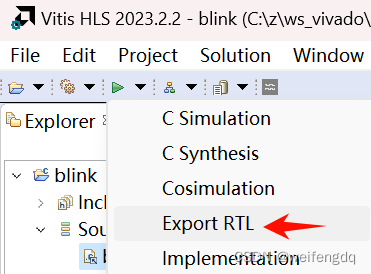

综合, 之后可以导出RTL

这样就有了一个Blink的IP, 可以用于Vivado工程

Vivado 使用自定义IP

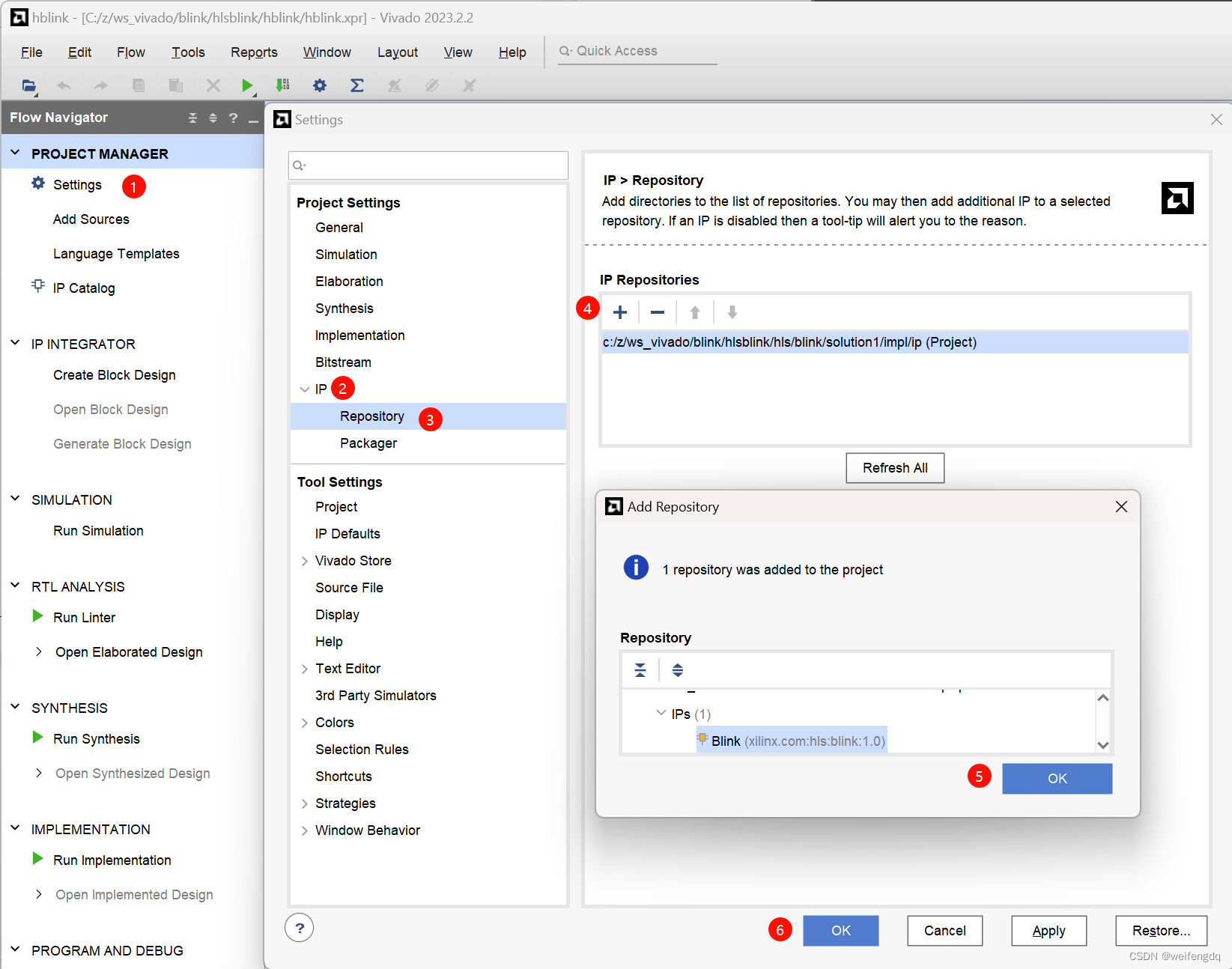

上面生成的Blink的IP, 可以用于Vivado工程(如果更新了hls代码, 需要重新综合导出, 并在下图中Refresh All, Block界面中重新导入IP, 或者点击界面提示的 Refresh IP Catalogs)

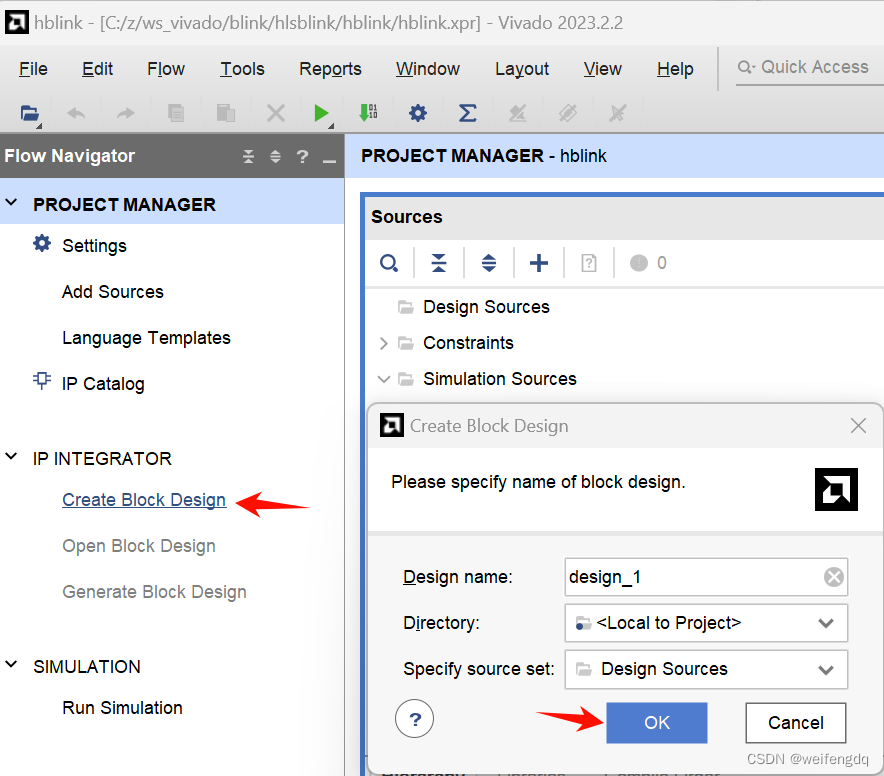

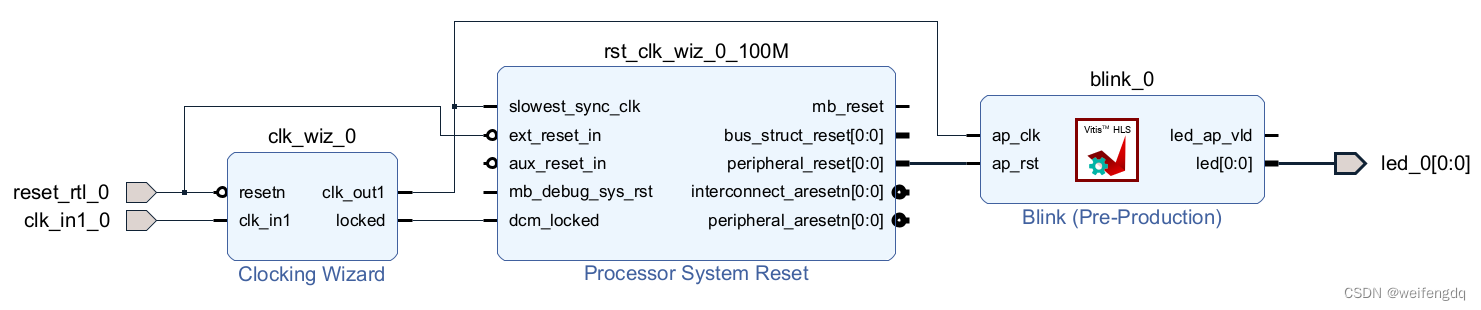

依然是Create Block Design

加入 Clocking Wizard(设置50M, 单端, 输出100M, 低电平复位) 和 Blink IP:

- 这里的 ap_vld 引脚用于有效指示, 指示数据何时可用于读取或写入, 这里不管它. 参考 pragma HLS interface • Vitis High-Level Synthesis User Guide (UG1399)

输出, 创建wrapper

分配clk rst led引脚, 生成位流文件, 测试即可.

本小节同样实现了点灯功能, Vitis HLS使用Cpp开发Blink IP, 然后Vivado中连连看完成实际效果.

HLS自定义IP含AXI接口连接MicroBlaze

如果想让Vitis HLS 像AXI GPIO IP那样和MicroBlaze等软核连起来, 刚好HLS有 m_axi, s_axilite 等, 可以使用 hls 实现类似 AXI GPIO 的效果

Tcl脚本创建HLS工程 综合导出RTL 版本控制

上小节是用GUI创建的工程, 本节用Tcl脚本创建工程

run_hls.tcl

- 创建proj_mhls工程, 会在当前目录生成同名文件夹以及hls.app

- 顶层函数blink

- 设置器件型号 xc7a35tfgg484-2

- IP接到MicroBlaze, 这里设为和MicroBlaze一样的100MHz

- c综合, 导出RTL后退出vitis_hls命令行

open_project -reset proj_mhls

add_files blink.cpp

# add_files -tb blink_test.cpp

set_top blink

open_solution -reset solution1

set_part {xc7a35tfgg484-2}

create_clock -period "100MHz"

# csim_design

csynth_design

# cosim_design -rtl verilog

export_design -evaluate verilog

exit

blink.cpp

- 顶层函数blink, 会在platform中输出xblink.h文件, 地址定义在xparameters.h

- in端口可以通过 XBlink_Set_in_r 函数赋值 0 或 1

- 返回值 0 可以通过 XBlink_Get_return 函数获取

int blink(bool *in, bool *out) {

#pragma HLS INTERFACE s_axilite port = in

#pragma HLS INTERFACE s_axilite port = return*out = *in;return 0;

}

运行脚本自动创建工程, 综合, 导出RTL, 无需打开GUI

vitis_hls -f .\run_hls.tcl

目录结构是这个样子, 传git时可以忽略log和proj_*

├── blink.cpp

├── proj_mhls

│ ├── hls.app

│ └── solution1

├── run_hls.tcl

└── vitis_hls.log

如果想打开Vitis HLS 的 GUI

vitis_hls -p .\proj_mhls\hls.app

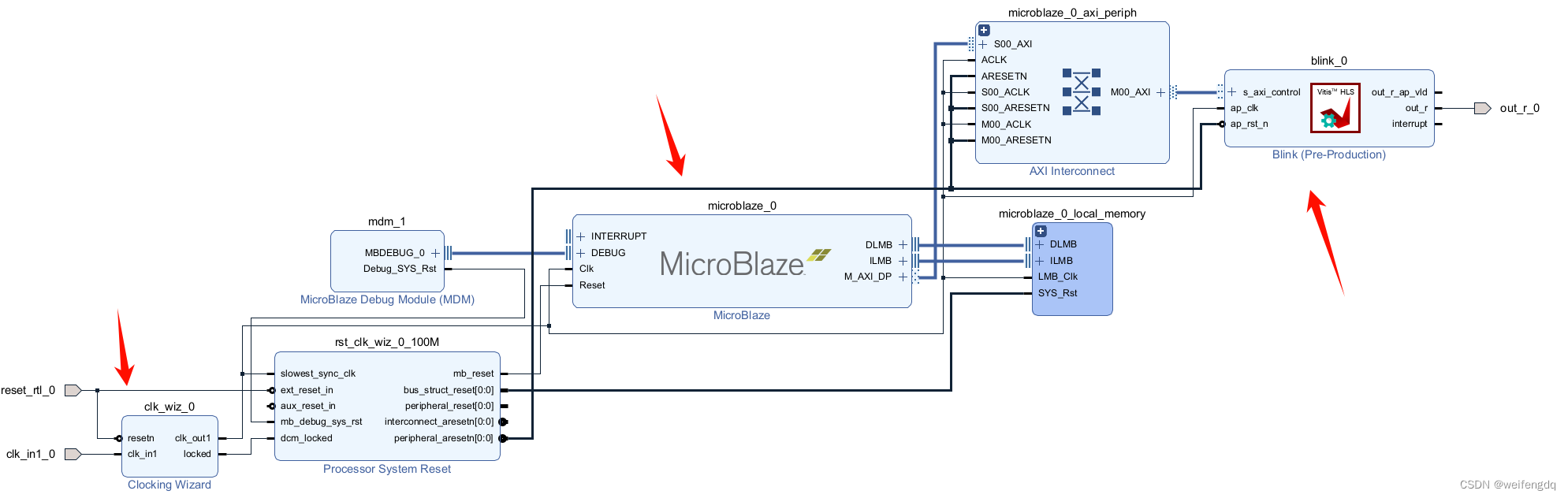

Vivado 连接自定义IP和MicroBlaze

创建工程部分略, IP部分截图

依然是 Generate Output Products -> Creat HDL Wrapper, 添加约束, 生成位流, 导出硬件得到XSA文件.

接着 Tools -> Launch Vitis IDE

Vitis 2023.2 代码编写

三步走:

- Open Workspace 找个文件夹当工程文件夹

- 根据XSA创建platform Component

- 根据platform创建App

main.cpp

- 通过地址查配置, 配置初始化, IP初始化

- 先关闭LED, 开始IP的运行

- 循环中Blink

#include "sleep.h"

#include "xblink.h"

#include "xparameters.h"int main(void) {XBlink_Config *cfg = XBlink_LookupConfig(XPAR_XBLINK_0_BASEADDR);XBlink xb;XBlink_CfgInitialize(&xb, cfg);XBlink_Initialize(&xb, XPAR_XBLINK_0_BASEADDR);XBlink_Set_in_r(&xb, 1);XBlink_Start(&xb);// XBlink_Get_return(&xb);while (1) {XBlink_Set_in_r(&xb, 0);usleep(1800000);XBlink_Set_in_r(&xb, 1);usleep(200000);}return 0;

}

编译运行, 效果是一样的

![[CISCN2019 华北赛区 Day2 Web1]Hack World 1 题目分析与详解](http://pic.xiahunao.cn/[CISCN2019 华北赛区 Day2 Web1]Hack World 1 题目分析与详解)

)

)