文章目录

- 一、模型的处理

- 二、TDR仿真

- 2.1 修改求解模式

- 2.2增加求解设置

- 三、查看仿真结果

- 3.1 查看TDR结果

- 3.2 查看S参数结果

- 四、结果分析

- 4.1上升时间tr对仿真的影响

- 附:工程链接

在上一讲中,主要是通过观察S参数确定via的优化是否达到目标。但S参数只能看到一个整体的结果,并不知道via真实的阻抗是多少?想要单独确定via的阻抗,最好还是通过TDR的仿真。

一、模型的处理

在上一讲中,已经比较详细的阐述了via的建模过程。 HFSS实战(二)——过孔via建模及参数优化

在这一节中,我们主要对模型进行进一步的处理。

TDR对仿真分辨率是有要求的,不同上升时间的step信号,能识别的最小尺寸是不同的。

举个例子:

15ps的上升时间:

15 ∗ 1 0 − 12 ∗ 3 ∗ 1 0 8 ∗ 1 0 3 3.3 = 2.48 m m ≈ 100 m i l \frac{15*10^{-12}*3*10^{8}*10^{3}}{\sqrt[]{3.3}}=2.48mm≈100mil 3.315∗10−12∗3∗108∗103=2.48mm≈100mil

而过孔的尺寸比 100 m i l 100mil 100mil要小很多。

有两种办法可以解决这个问题:

1、利用wave port的De-embeding功能(因为我设置wave端口后仿真一直报错,没有解决。如果有人设置成功了,请告诉我一声,十分感谢~)

工程连接如下:waveport_via_sim

waveport的特点如下:

- 不需要增大模型的尺寸就可以拉升或缩短传输线

- de-embed设置为正数,意味端口内移,传输线缩短

- de-embed设置为负数,意味端口外移,传输线拉长

2、使用lump port + 传输线尺寸拉长,处理后的模型如下,拉长后,尺寸变大,求解速度变慢,不是很推荐这种。

二、TDR仿真

将其导出为HFSS模型后打开工程。导出过程参见:HFSS实战(二)——过孔via建模及参数优化

2.1 修改求解模式

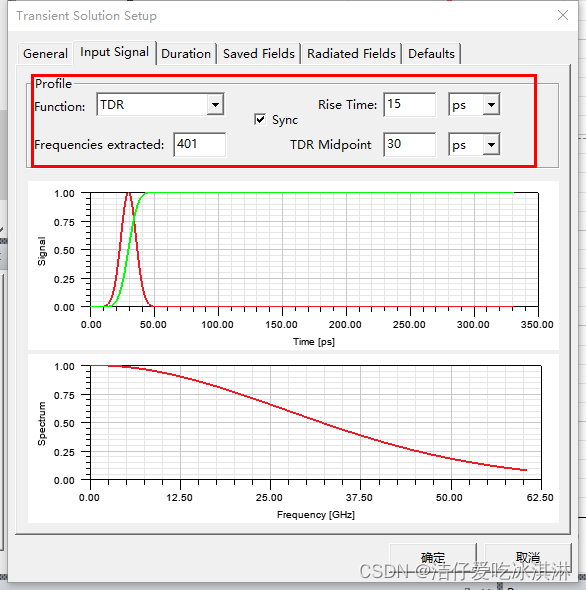

2.2增加求解设置

点击Analysis→Add Solution Setup

设置完成点击→确定

点击Setup1→右键→Analyze

三、查看仿真结果

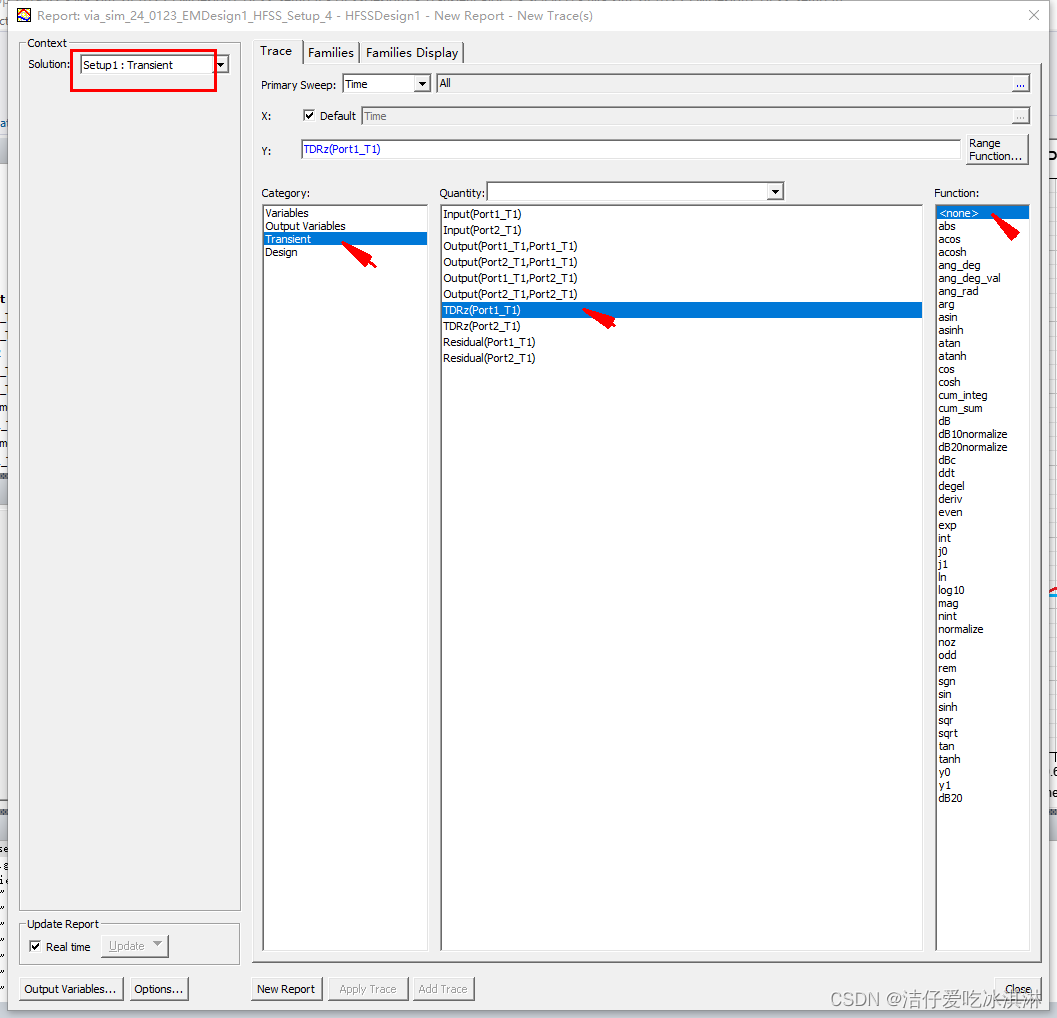

3.1 查看TDR结果

3.2 查看S参数结果

四、结果分析

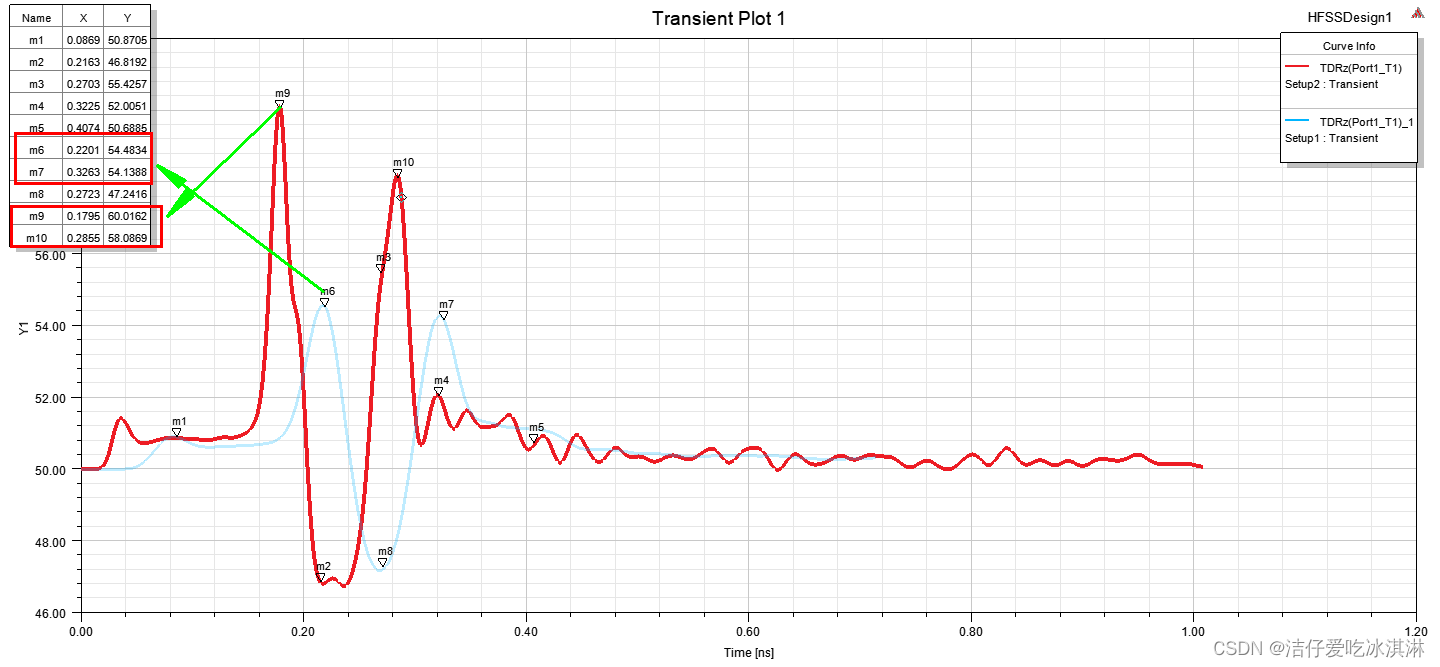

过孔处的阻抗上升至54 Ω Ω Ω,基本还算满足要求。

4.1上升时间tr对仿真的影响

新建setup,将RiseTime=15ps,再次执行仿真

可以看出原本是54Ω的过孔变成了60欧姆。什么原因呢?

我猜可能是残桩的影响,下一节我们继续!

附:工程链接

过孔仿真HFSS工程链接

C#的预处理器指令和条件编译符号)

![P9389 [THUPC 2023 决赛] 烂柯杯 题解](http://pic.xiahunao.cn/P9389 [THUPC 2023 决赛] 烂柯杯 题解)

赋值运算符)

命名空间)