使用源文件

概述

源文件包括从AMD IP添加的设计源、知识产权(IP)源目录、RTL设计源、从系统添加的数字信号处理(DSP)源生成器工具和IP子系统,也称为块设计,由IP集成商创建AMD Vivado的功能™ 设计套件。源文件还包括模拟源文件和约束文件,用于指定设计的时间要求和物理约束定义设计所使用的AMD设备资源。在项目模式下工作时,可以创建并使用Vivado IDE或使用Tcl命令或脚本以及Vivado IDE添加源文件自动管理项目中的源文件。您可以创建和管理源当前项目的本地文件、从库远程引用的文件或单独的文件目录您可以在中的任何位置将Verilog、VHDL和SystemVerilog源文件添加到项目中设计流程。

注意:有关使用AMD Zynq时源文件管理的信息™ 7000台设备,AMDZynq™ UltraScale+™ MPSoC设备和MicroBlaze™ 处理器,请参阅MicroBlaze嵌入式处理器《设计用户指南》(UG1579)。在非项目模式下工作时,可以使用Tcl命令或脚本,但必须手动管理源文件。本章的大部分内容涵盖在项目模式下创建和管理源。在非项目模式下使用源涵盖在非项目模式下创建和管理源。有关项目和的更多信息非项目设计流程模式,请参阅Vivado design Suite用户指南中的此链接:设计流程概述(UG892)。将源文件添加到Vivado Design Suite时,无论是在项目模式下还是在非项目模式下,该工具都会保留文件的相对路径和绝对路径。当打开设计时,默认情况下Vivado design Suite首先应用相对路径来定位文件和目录,如果找不到文件,则应用绝对路径。此功能受控制通过PATH_MODE属性,该属性默认为RelativeFirst。您可以更改此行为为特定的设计源设置PATH_MODE属性。请参阅有关详细信息,请参阅Vivado Design Suite属性参考指南(UG912)中的PATH_MODE属性信息注意:有关与添加源相关联的Tcl命令的信息,请参阅Tcl命令添加设计源、约束文件和仿真源。

创建和添加设计源

在AMD Vivado™ IDE,您可以创建和管理设计源文件,包括HDL或网表文件。在AMD Vivado中打开一个项目™ IDE中,“源”窗口显示设计源、约束和模拟源是文件或文件集的集合,构成当前项目。

“源”窗口提供了查看与关联的源文件的不同方式项目,包括以下视图:

•层次结构:显示设计模块和实例的层次结构以及源包含它们的文件。Vivado IDE自动检测设计层次结构的顶部,尽管您可以根据需要手动更改它。

•IP源:显示IP核心定义的所有文件,这是从Vivado IP积分器,或从System Generator添加的DSP模块。

•库:显示按不同库排序的设计源。

•编译顺序:按从前到后的顺序显示源文件,以及显示了约束的处理顺序。“编译顺序”视图可以显示用于合成、实现或模拟的处理顺序。

提示:有关“源”窗口中使用的图标的信息,请参阅Vivado Design Suite用户指南:使用Vivado IDE(UG893)。创建新的源文件

1.若要创建新的设计源以添加到项目中,请选择“文件” → 添加源。

注意:也可以从“源”窗口的右键单击菜单中选择“添加源”,或者在流导航器中单击“添加源”。

2.在“添加源”向导中,选择“添加”或“创建设计源”,然后单击“下一步”。

3.在“添加或创建设计源”页面中,从子菜单中选择“创建文件”选项以创建新的源文件。

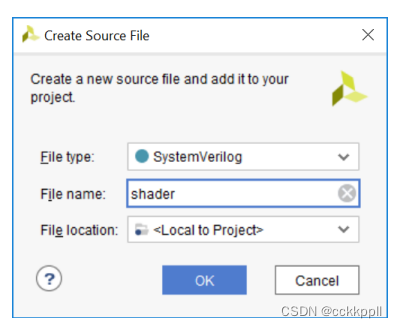

4.在“创建源文件”对话框中,设置以下选项,然后单击“确定”:

•文件类型:指定以下文件格式之一:Verilog文件(扩展名.v)、Verilog头文件(.vh扩展名)、SystemVerilog文件(.sv扩展名)和VHDL文件(.VHDL或.vhd扩展名)或内存文件(.mem)。

•文件名:指定新的HDL源文件的名称。

•文件位置:指定创建文件的位置。文件的占位符将添加到“源”窗口中显示的源列表中。这个

只有在“添加源”向导中单击“完成”,才会创建文件。

提示:您可以多次单击“创建文件”来定义要添加到项目中的几个新模块。

5.在“添加或创建设计源”页面中,为源文件指定适当的库。

默认情况下,所有HDL源都会添加到xil_defaultlib库中。在图书馆列,可以引用现有库名称,也可以手动键入新库名称根据需要指定其他用户VHDL库。

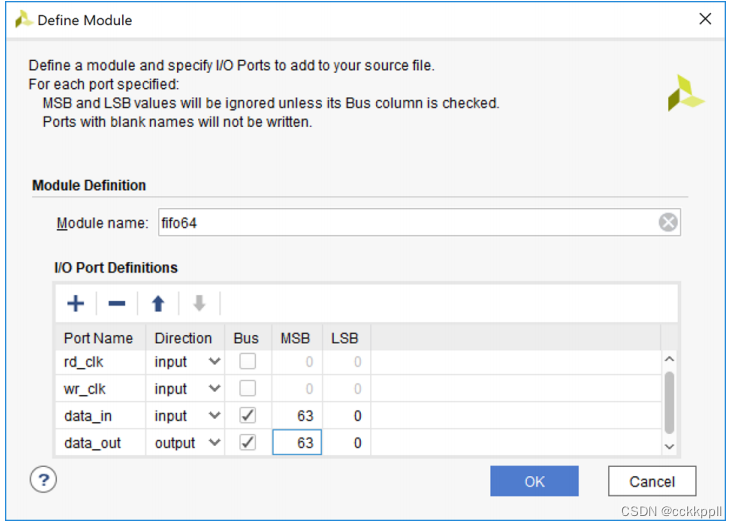

6.单击“完成”创建新的源文件,并将它们添加到项目中。创建新的源文件后,Vivado IDE将打开“定义模块”对话框以提供帮助您可以定义模块或实体声明的端口。在定义模块对话框中,您可以定义Verilog的模块或实体,Verilog使用以下选项的Header、SystemVerilog或VHDL代码:

•新建源文件:如果您创建了多个文件,则会显示此字段,允许您选择要定义的模块的名称。

•实体名称/模块名称:指定VHDL代码中实体结构的名称或者Verilog或SystemVerilog代码中的模块名称。

注意:名称默认为文件名,但可以更改。

•体系结构名称:指定VHDL源文件的体系结构。默认情况下,名称是行为。

注意:在定义Verilog或SystemVerilog模块时,此选项不会出现。

•I/O端口定义:定义要添加到模块定义中的端口:

•端口名称:定义要显示在RTL代码中的端口名称。

•方向:指定端口是输入、输出还是双向端口。

•总线:指定端口是否为总线端口。使用定义总线宽度MSB和LSB选项。

•MSB:定义最高有效位(MSB)的编号。这与LSB相结合字段,以确定所定义的总线的宽度。

•LSB:定义最低有效位(LSB)的数量。

注意:如果端口不是总线端口,则忽略MSB和LSB。“源”窗口列出了新定义的模块。在中编辑新的源文件Vivado IDE文本编辑器,双击文件或从右键菜单中选择“打开文件”。请参阅《Vivado Design Suite用户指南:使用Vivado IDE(UG893)》中的使用文本编辑器以获取有关编辑文件的信息。

添加设计源

1.选择文件 → 添加源。

注意:或者,也可以单击“流导航器”中的“添加源”,或者从右键单击“源”窗口中的菜单。

2.在“添加源”向导中,选择“添加”或“创建设计源”,然后单击“下一步”。

3.在“添加或创建设计源”页面中,设置以下选项,然后单击“完成”。

•添加文件:打开文件浏览器,以便选择要添加到项目中的文件。您可以添加RTL项目的以下文件类型:HDL、EDIF、NGC、BMM、ELF、DCP和其他文件类型。

注意:在“添加源文件”对话框中,每个文件或目录都由一个图标表示作为文件或文件夹。红色小方块表示它是只读的。

•添加目录:打开目录浏览器,从所选目录添加源文件目录。指定目录中具有有效源文件扩展名的文件将添加到项目。

•创建文件:打开“创建源文件”对话框,您可以在其中创建新的VHDL,Verilog、Verilog头或SystemVerilog文件。

•库:通过选择从当前定义的库名称中选择库,或通过键入指定新的库名称库文本字段。

注意:此选项仅适用于VHDL文件。默认情况下,HDL源被添加到xil_defaultlib库。您可以根据需要创建或引用其他用户VHDL库。对于Verilog和SystemVerilog文件,将库设置为xil_defaultlib。

•删除:从要添加的文件列表中删除选定的源文件。

•上移/下移:按列表顺序上移/下移文件或目录。的顺序在下游过程中,文件会影响详细说明和编译的顺序例如合成和模拟。请参见指定顶部模块和重新排序源文件夹。

•扫描并将RTL Include文件添加到项目中:扫描添加的RTL文件并添加任何被引用的Verilog’将文件包含到本地项目目录结构中。

•将源复制到项目中:将文件复制到本地项目目录中,而不是引用原始文件。

注意:如果使用“添加目录”添加源文件的目录,则目录结构为在将文件本地复制到项目中时进行维护。有关详细信息,请参见使用远程源或将源复制到项目中。

•从子目录添加源:从目录的子目录中添加源文件使用“添加目录”选项指定。

)

-投票帖子管理实现)

)