@TOC 鉴频鉴相器中为了保证鉴相范围,主要有两种PFD可以在理想情况下实现

1.电路结构

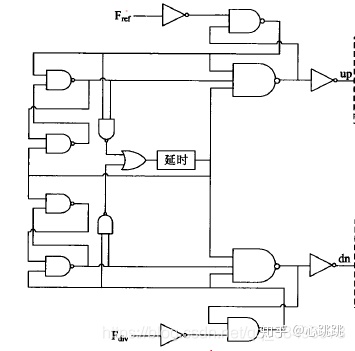

1.1传统型电路结构

参考文献:宽带CMOS分数频率合成器的研究与实现——黄福青 东南大学博士论文

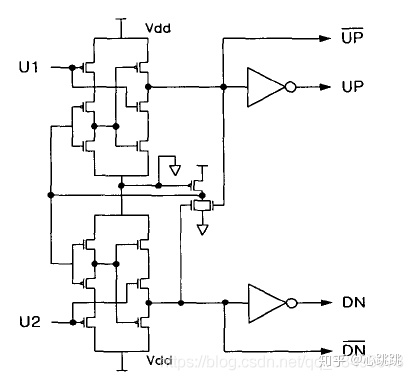

1.2 触发器型电路结构

参考文献:A High Speed and Low Power Phase-Frequency Detector and Charge - pump

此电路在仿真对比的时候,没有采用图中为伪nor结构,采用静态CMOS逻辑的或非门,并且加入了delaybuffer,来消除死区。

2.电路仿真

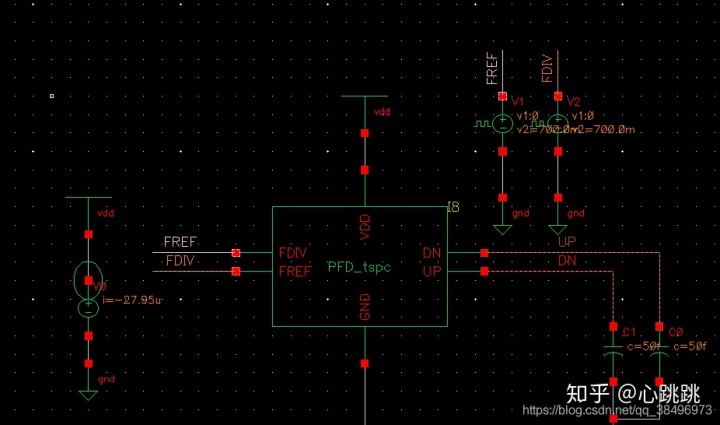

2.1仿真电路模型

两种PFD采用相同的测试电路,电源电压0.7V。输出负载50fF。

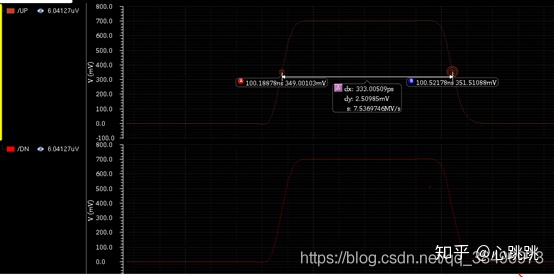

2.2 死区时间:

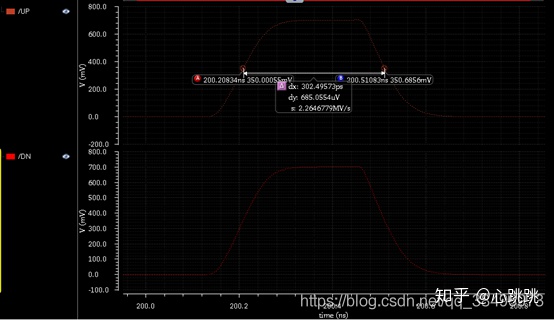

输入同频同相时钟信号30MHz,脉冲的上升沿50%到下降沿50%为脉冲宽度。

传统型经过加入delay后UP和DN 脉宽约为333ps,即为复位延迟时间。

触发器型经过加入delay buffer后复位延迟为300ps

两者的复位延迟时间比较意义不大,都可以通过调节delay buffer延时获得。 ## 2.3鉴相范围:: 两个电路理论上均可以实现

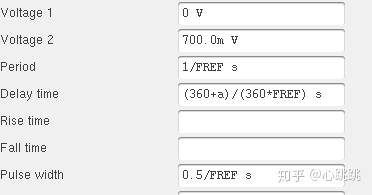

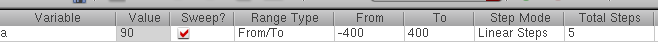

传统型仿真结果:

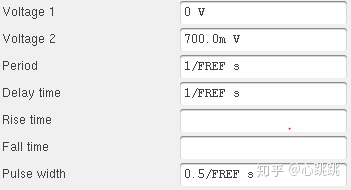

边沿触发器型仿真结果

两者的鉴相范围大约都是 -1.94pi到1.94pi。

2.4功耗仿真

由于两种电路均是动态功耗,与时钟频率有关,以200M为例,FDIV落后FREF信号90度。仿真时间500n

传统型平均电流41.39uA 触发器型平均电流20uA

触发器型在相同时钟频率情况下功耗有很大优势。

2.5 最高工作频率

最高工作频率没有仿真,仿真到2G,但是不清楚如何算是UP和DN信号输出正常。有待请教。

3.问题

触发器型的PFD的输出信号UP和DN,脉冲的上升下降沿较长,粗略观测 传统型输出脉冲边沿约为100ps左右, 触发器型的脉冲边沿在200ps左右。 感觉触发器型的PFD输出信号边沿可以进一步优化,我没有详细研究如何优化,欢迎讨论。

,切片,扩展,删除,追加,统计,长度,获取下标等...)