上一章中提到了普通RS锁存器的两大缺点:

1. S端口和R端口不能同时有效,但实际应用中不能保证这种情况不出现,此时可能会出错;

2. 在计算机中,有许多内存单元协同组成一个寄存器,存储同一个数据。但每一位数据可能是先后到来的(比如加法器,计算出最高一位会花费比低位更多的时间),如果内存单元被写入的时间无法统一,就会造成混乱。RS锁存器并没有提供控制写入的端口——只要输入变化,状态就会改变。

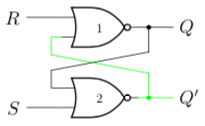

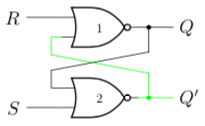

本章中将要探讨如何改进这两点,并设计出更加适合存储数据的存储电路。基础电路仍然是RS锁存器:

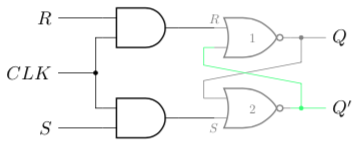

一、门控RS锁存器

我们从问题二开始解决。为此我们只需增加一个写控制端口。当该端口为高电平时,

控制端口,我们将其命名为

门控RS锁存器的功能和普通RS锁存器一样,也有一样的状态转换图和特性方程:

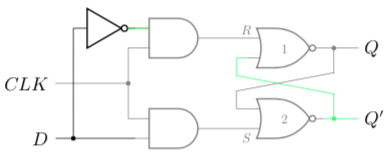

二、D锁存器

接下来,我们解决第一个问题:摆脱RS锁存器的

为此,我们做出的牺牲是放弃了

因此我们发现,当

D锁存器在

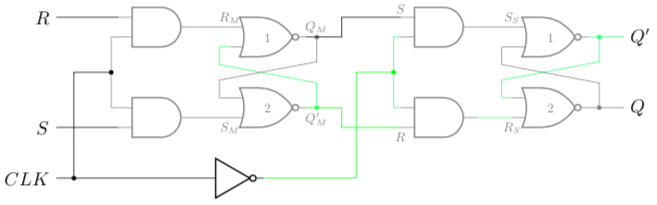

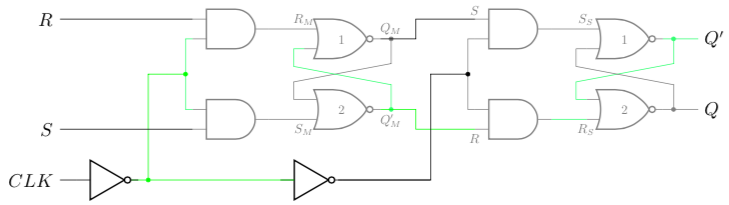

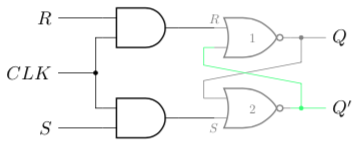

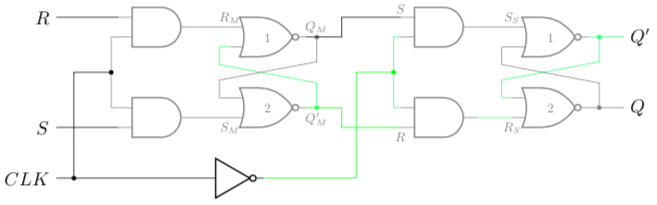

三、RS触发器

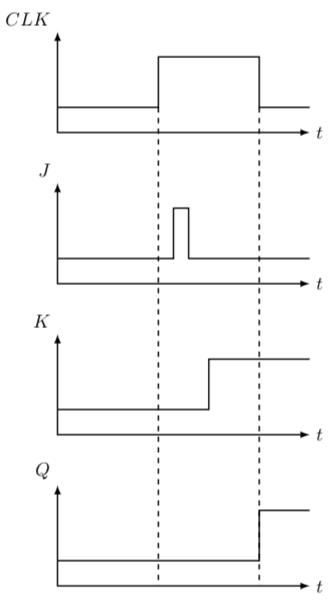

一个只在某个时刻发生状态更新的锁存器就叫做触发器。我们考虑如何实现在某个时刻的更新。如果有两个RS锁存器,可以将它们串联,并给一个相反的

第一个锁存器叫主锁存器,第二个叫从锁存器。从锁存器接收主锁存器的状态作为输入。在时钟信号低→高→低的一个周期中,它的功能发生了这样的变化:

时,主锁存器处于保持状态,不接受输入;从锁存器可以工作,但主锁存器状态不改变,所以它也不会发生改变。此时整个触发器就处于保持状态。主锁存器状态为1,则从锁存器S=1, R=0,状态也为1,反之则状态为0,所以整个触发器的状态和主锁存器状态一致。

时,主锁存器接受输入,能改变状态,但此时从锁存器不再工作,因此该状态改变暂时无法反映到触发器的输出上,触发器仍然处于保持状态;

又变回0,此时从锁存器重新开始工作,把主锁存器的最后一个状态接收,然后改变触发器输出。

一个信号要想通过整个触发器从输入走到输出,要先在时钟为高时进入主锁存器,然后在变成低电平时从主锁存器进入从锁存器,因此,只有在

要做出上升沿更新,也就是

要注意的是,触发器仅仅改变了锁存器更新的机制,并没有改变它的逻辑功能——比如,对于RS触发器,它的特性方程和RS锁存器一致:

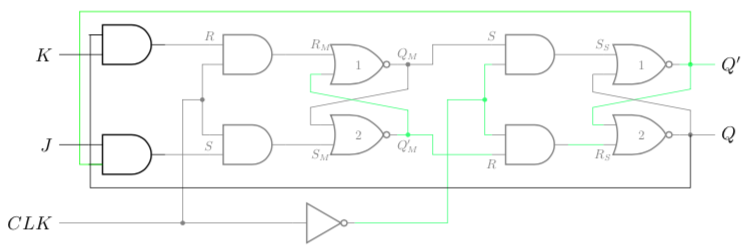

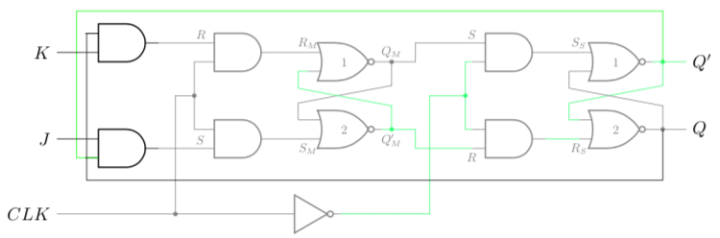

四、JK触发器

对于RS触发器,我们也要继续解决这个约束条件的问题。当然,我们仍可以像D锁存器那样,把

但还有第二种方案,就是利用

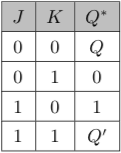

仍然用代入的方法得出它的特性方程:

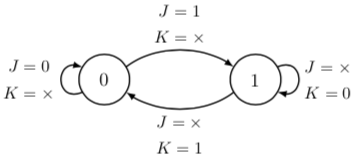

但是,这个特性方程不像D锁存器一般直观,所以在画状态转换图时,我们可以分别代入各种输入并列出特性表:

从此表来看,J和K的四种取值对应四种功能——其中保持(

JK触发器相比于RS触发器,还有一个性质,就是它会自己把自己锁死。对于RS锁存器,我们可以放心地在

理论上,在高电平期间的

这是因为,由于

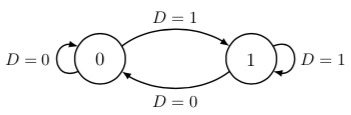

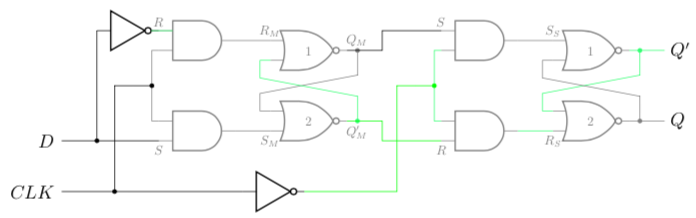

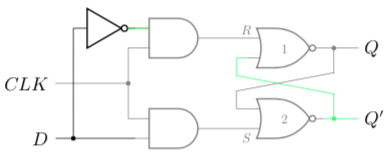

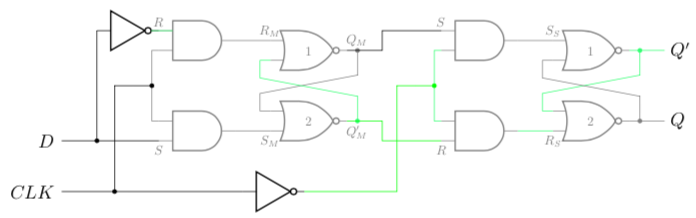

五、D触发器

仍然令

它的逻辑功能仍然是:

相比JK触发器,由于它不使用自身状态作约束,所以不会产生一次翻转的问题。和RS触发器一样,它只关心下降沿瞬间主锁存器的状态。

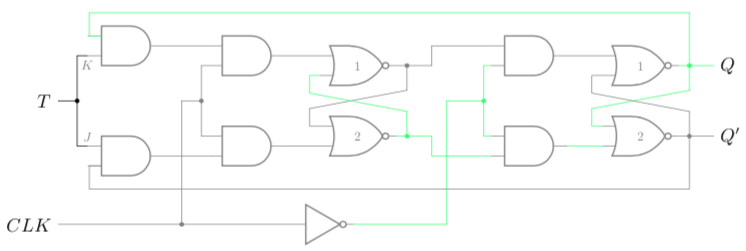

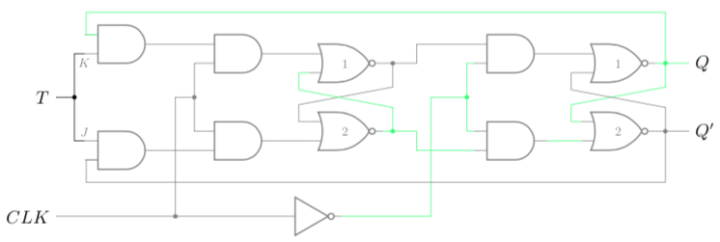

六、T触发器

T触发器是一类偏功能性的触发器——它没有做出任何显著的改进,而只是提供了一种特殊的逻辑功能。我们将同一个输入赋给JK触发器的

那么,它的特性方程为:

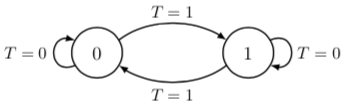

同样画出它的真值表和转换图:

由此发现,它只有“保持”和“翻转”的功能,也就是JK触发器中

总结:本文中,我们的锁存器经历了如下的迭代:

我们改进了上一章所提及的两个问题,并最终得到了两套解决方案:JK触发器和D触发器。这两个触发器,一个更全面,一个更简单,两个都是在时序电路设计中最常用的触发器。