物理单元( physical cell)指没有逻辑功能但是具有物理实现功能的标准单元, 用于抑制芯片生产过程中的各类物理效应, 保证芯片生产后能够正常工作 。硬核位置确 定后,需要插入物理单元消除影响芯片工作的物 效应,所有插入的物理单元都需要将物理状态设置为锁定 ,防止 EDA工具在后续优化中改动单元物理位置 。常见物理单元有tap cell,dcap cell,boundary cell,filler cell,tie cell,antenna cell。

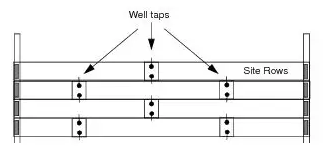

Tap cell

tap cell用于消除芯片的闩锁效应,通过固定间距对衬底施加偏置电压减小衬底的寄生电阻,使三极管压无法达到导通要求从而切断闩锁效应的正反馈环路 ,消除闩锁效应。

tap cell一般交错摆放,类似棋盘分布。在 7nm工艺下,tap cell的最大 有效 间隔为 100μm。如图所示 ,芯片内部 每间隔 100μm需要插入一列 tap cell,如果 tap cell的插入位置已被硬核占据或者水平方向存在硬核阻断了阱的连续性 ,需要在硬核周围 50μm的范围内插 入 tap cell消除闩锁效应的影响。

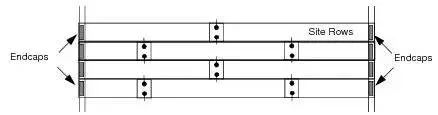

Boundary cell

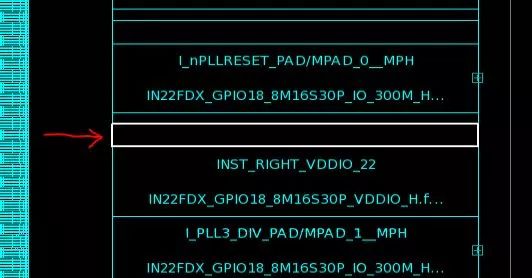

boundary cell,也称作Endcap cell,用来保证芯片边界标准单元的物理环境保持 一致,确保标准单元不会出现在 阱的边缘。在芯片的边界、硬核周围都需要插入 boundary cell 。

Boundary cell一方面可以保持阱和注入层的连续性,同时也可以在刻蚀和离子注入的时候对row边缘的std cell起到一定的保护作用。

Filler cell

Filler cell用于填充芯片内部的空白部分。物理版图没有标准单元的区域需要插入 Filler cell,filler cell用于连接芯片内部的扩散层和电源线,使 阱保持连续,满足DRC的检查要求。同时也可以对周围的std cell有一定的保护作用。

在集成电路制造过程中,无论是注入还是刻蚀,贴近空旷的区域的一边都倾向于受到更多的刻蚀或者注入,这样无疑会增大cell的variation,进而对时序的准确性产生负面影响。

除普通的standard cell filler,还有IO filler。

IO filler,也叫作pad filler,通常是用来填充I/O 单元与I/O单元之间的空隙。为了更好的完成power ring,也就是ESD之间的电源连接。

Decap cell

Decap cell,中文名去耦单元,这是一种特殊的Filler cell。当电路中大量单元同时翻转时会导致冲放电瞬间电流增大,使得电路动态供电电压下降或地线电压升高,引起动态电压降,俗称IR-drop。

为了避免IR-drop对电路性能的影响,通常在电源和地线之间放置由MOS管构成的电容,这种电容被称为去耦电容或者去耦单元,它的作用是在瞬态电流增大,电压下降时向电路补充电流以保持电源和地线之间的电压稳定,防止电源线的电压降和地线电压的升高。在电源电压正常的时候,Decap可以充电来存储能量,当电源电压较低的时候就可以放电来起到一定的缓冲作用。

在布局规划阶段,所有逻辑功能相关的标准单元位置尚未确定,插入填充会影响 EDA工具的布局和优化效果,通常在线完成后统一插入填充单元。

Tie cell

Tie cell,又称为钳位单元。常见的有tie high,tie low两种,分别提供电源地电位。

主要起到ESD保护的功能。通常在placement之后,route之前添加。

Antenna cell

天线效应是集成电路制造过程中经常发生的现象,原因在于连接在栅极的金属会不断收集电荷,在某个临界节点将会放电到栅极引起晶体管损坏。

解决的办法之一就是插入antenna cell来增大栅极的面积,也就是提高承受放电电流的能力。在后端设计中,通常在绕线阶段让工具在发现有antenna violation的时候自动插入antenna cell。

Spare Cell

spare cell就是备用的cell。 简单来说,就是每块地方洒一些类似DFF,NAND,AND,XOR,INV等的备用cell, 为以后做function eco和metal eco用。

数字后端——ECO_沧海一升的博客-CSDN博客对ECO(engineering change order)进行简单介绍https://blog.csdn.net/qq_21842097/article/details/121717450 但是插入spare cell也有一些负面影响,主要原因在于它们会占用std cell的放置区域,可能会引起整体的优化结果质量下降。

MIMCAP

最后介绍一下MIMCAP,其中MIM指的是Metal-Insulator-Metal,这是一种特殊类型的用来提供电容的cell,区别于DECAP的主要特点是电容量较大,大小也比一般的std cell要大很多,而且使用的金属层一般比较高,可以重叠放在绝大部分类型的cell上而不产生DRC。

通常在小尺寸的工艺上,mimcap layout的下极板需要先先到top metal,然后再连下去。因为电容在工作过程中,上下极之间存在一定压差,由于MIM之间的介质较薄,容易发生类似天线效应的情况,即把介质层击穿,因此才采用将下极板连接重新接回TOP METAL,以避免类似天线效应的发生。