随着集成电路制造工艺技术的迅速发展,集成电路集成度迅速攀升,制造流程及工艺步骤日趋复杂,工艺尺寸也在不断缩小。集成电路可制造性设计(Design For Manufacturability,DFM) 以直接提升集成电路芯片的良品率及降低芯片的生产成本为主要目的,越来越引起业界的关注。

随着集成电路工艺尺寸的进步,DFM 对芯片良率的影响日益凸显,随着工艺尺寸的演进,到了超深亚微米90nm 及以下,工艺和设计因素对芯片良品率的影响急剧增加。因此在超深亚微米考虑可制造性是十分有必要。

一、深亚微米时代的可制造性设计问题

在传统的数字后端设计中,版图的物理设计一般通过了DRC、LVS 的物理验证,即可保证芯片质量及良品率。然而随着工艺尺寸进入深亚微米,一些制造技术如光刻胶曝光、显影、刻蚀和化学机械抛光都会对金属互连结构造成不利影响,并随着布局的局部特征而变化,这将使得传统的数字后端设计方法面临严峻的挑战。

可制造性设计是为了提升芯片生产良率的而定制的设计规则。它将设计与生产之间的联系变得更加紧密。换句话说,完整的可制造性设计方案能够让IC 设计者更早的使用可制造性设计流程与规范,来提升芯片的设计、生产效率。因此,从版图设计者的角度来说,需要有一套适应深亚微米的可制造性设计流程来指导版图的设计与验证工作。在过去的芯片设计中,IC 设计者可以直接将满足物理验证的电路设计交给代工厂,进行生产制造。但是在进入先进制程(180nm

以下)工艺后便遇到了困难,主要体现在以下几个方面。

1、CMOS闩锁效应

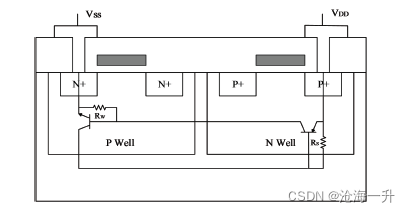

MOSFET 为四端器件,包括源(S)、栅(G)、漏(D)、衬底(Sub),在现代CMOS 双阱工艺中,P 阱连接VSS,N 阱连接VDD,这种双阱CMOS 结构将产生寄生双极晶体管:P 阱存在NPN 晶体管,N 阱存在PNP 晶体管,构成SCR(Silicon Controlled Rectifier)寄生结构。

当P 管源极输入一个正向触发信号,在电源VDD 和地线VSS 之间由于寄生的PNP 和NPN 双极性晶体管。当无外界干扰未引起触发时,两个晶体管均处于截止状态,集电极电流增益非常小,因此闩锁效应不会产生。但当其中一个晶体管的集电极电流由于受外部干扰而突然增加到一定值时,会反馈至另一个晶体管,从而使两个晶体管因触发而导通(通常情况下是PNP 比较容易触发起来),VDD 至VSS 之间形成低抗通路。之后就算外界干扰消失,由于两三极管之间形成正反馈,还是会有电源VDD和地VSS 之间的漏电(锁定状态),闩锁效应由此而产生。随着集成电路制造工艺的发展, 晶体管的集成度越来越高,产生闩锁效应的可能性会越来越大。

2、金属互连问题

随着集成电路制造工艺的不断复杂化,互连金属层的不断增加,以及工艺节点的不断降低,互连制造问题已成为制约纳米CMOS 工艺芯片生产制造成品率(Yield)的最大因素。一方面,工艺节点降低带来的工艺偏差,会产生越来越多的刻蚀错位,大大增加通孔失效的概率。另一方面,版图的密度效应问题会使金属在化学机械抛光过程中出现版图表面的高低起伏。倘若金属互连的通孔在制造过程出现这种现象,就很有可能造成层间金属互连失效,特别是进入深亚微

米时代后,铜互连技术的大量应用使互连线通孔失效的现象发生的越来越频繁。

3、天线效应

在芯片生产过程中,暴露的金属线或多晶硅(polysilicon)等导体,就像是一根根天线,会收集电荷导致电位升高。天线越长,收集的电荷也就越多,电压就越高。若这片导体碰巧只接了MOS 栅,那么高电压就可能把薄栅氧化层击穿,使电路失效,这种现象就是“天线效应(PAE)”。

随着半导体制造工艺的不断进步,等离子体Plasma 干法刻蚀技术因其各向异性、高的选择比等优点被广泛用来刻蚀金属与半导体材料。该方法通过使用放电产生的等离子体与刻蚀材料接触发生化学反应实现刻蚀过程。干法刻蚀方法的缺点是增加了半导体内部游离的等离子体电荷数目,这无疑会增加天线效应发生的概率。

4、随机颗粒缺陷

半导体制造工艺过程中许多工艺节点都会引入沾污而产生随机颗粒缺陷(Random Particle Defects)。如果在一条或两条较窄的互连线之间存在着随机颗粒缺陷,则可能造成互连线短路或断路,如图:

传统上,芯片制造厂商通过制定最小线宽、最小间距等设计规则避免随机性误差对良品率的影响。版图设计者只要遵守最小设计规则就可以减少由颗粒引起的电路短路或者开路现象。但随着集成电路进入超深亚微米时代,电路的特征尺寸在不断减小,而引起随机性误差的颗粒几何尺寸并没有随之变小,颗粒尺寸逐渐可以与特征尺寸相比拟,使得纳米级电路的成品率对随机误差更加敏感。

随机颗粒缺陷的位置可以通过关键区域(Critical Area)来进行描述,其良率Y可以由泊松等式来描述。

CA 表示关键区域面积,DD 表示工艺固有缺陷密度。

所谓关键区域,是指如果随机缺陷的中心落在这个范围内,就会发生电路故障(产量损失)的区域。

对于一个确定的版图来说,随机颗粒缺陷尺寸越大,则关键区域面积越大,芯片良率损失也会越大。通常关键区域CA 面积由版图设计者决定,工艺固有缺陷密度由代工厂决定。

5、版图图形密度

在深亚微米制造工艺中,化学机械抛光(CMP)技术被广泛应用于版图表面的平坦化,该技术通过抛光头与基片之间的化学反应与机械运动来实现基片表面的平坦化,但最终获得的图形表面平整度往往会受到版图图形密度影响。

CMP 是利用抛光液中化学添加剂的化学作用,首先与晶片表面材料进行化学反应,形成易去除的薄膜反应层,再通过抛光垫于晶片之间的研磨料的摩擦作用,去除前期形成的薄膜反应层,最后,通过抛光液的携带作用,将抛光去除的材料带离晶片表面,露出新生表面,进一步再反应再去除,重复进行以去除表面的粗糙部位,达到平坦化目的。

所谓版图图形密度,是指在化学机械抛光过程中,版图中图形小间距、高密度区域的抛光速度比大图形间距、小密度的区域快。由于小而孤立、凸出的图形在平坦化过程中要承受较

大压力,所以抛光速度较快;低处图形承受的压力相对较小,所以抛光速度较慢。

由于图形密度的差异,最终会造成版图图形的凹陷和侵蚀,如上图所示。如果在通孔平坦化时出现这种现象,将很可能出现金属互连线断路的现象。

二、可制造性设计流程

加入可制造性设计的后端实现流程如下图:

整个流程其实是针对CMOS 深亚微米出现的闩锁效应,天线效应效应、金属互连问题、版图随机缺陷及版图图形密度等可制造性问题,提了解决方案,并加入到传统流程中。

提及的物理实现单元可见数字后端——物理单元介绍

1、Tap 单元插入(Tap Cell Insertion)

在CMOS 工艺中通过插入Tap 单元来解决并预防闩锁效应,Tap 单元版图如图(a)所示。作为一类特殊的物理单元,阱连接单元(Well-Tap-Cell)是近年来在130nm 及以下更先进的物理设计中新增加的,它不存在任何逻辑功能与时序约束,主要用来限制电源(地)与衬底之间的电阻,减小闩锁效应发生的几率:通过Tap 单元将N well 连接至VDD,P 衬底连接至VSS,以电阻并连的方式降低N 阱寄生电阻RS、P 阱寄生电阻RW,从而降低寄生三极管的电流放大倍数,从而有效提高寄生SCR 网络抗闩锁的能力,如图(b)所示。

2、天线二极管插入(Antenna Cell Insertion)

在实践中,消除天线效应方法一般有三种,包括跳线法,添加天线二极管,插入缓冲器三种。

跳线法可以分为向上跳线法与向下跳线法两种,即通过不同金属间向上或向下的跳线来断开存在天线效应的金属层,经通孔连接到其他金属层,然后再重新连接到当前层。跳线法虽然操作简单,但会引入额外的通孔与金属线,进而加剧线间串扰,产生额外的设计规则问题,因此在使用时要严格控制通孔数量与金属布线层。

所谓添加天线二极管,是指在存在天线效应的金属层上插入天线二极管单元,通过二极管的反向漏电流来释放电荷,实现天线效应的消除,如下图:

插入缓冲器,是通过在金属导体长线上插入多级缓冲器的方法来消除天线效应。

3、叠层通孔最小区域填充(Double Via Insertion)

金属互连问题最有效的解决方法是叠层通孔最小区域填充,即在通孔旁路通过并连冗余通孔的方式来减小通孔失效的概率,如图所示。

这种方法不仅解决了通孔空洞(Voids in Vias)、金属互连失效等问题,保证了金属线之间的连通性,另外,因为通孔的电阻要大于金属线,所以增加并连的通孔数目后还可以减小通孔电阻,减小线上延时,进而改善电路关键路径的时序及功耗损失。因此在设计布线之后进行叠层通孔最小区域填充是非常必要的。

4、互连线全局扩展与加宽(Wire Spreading and Widing)

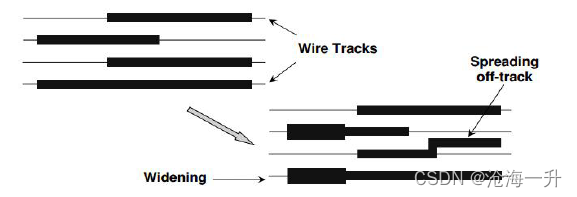

在芯片制造过程中,灰尘、微粒沾污都会引入随机颗粒缺陷,增大版图关键区域的面积,造成互连线短路或断路的现象发生。(1)通过扩展互连线间距(Wire Spreading)的方法可以减小随机缺陷对金属线的影响,进而来降低版图热点分布的个数,减小关键区域面积。互连线间距一般会被扩大1/2 pitch 的距离,以降低关键区域发生短路的可能性。(2)减小断路关键区域出现断路的概率可以通过增大金属线宽度(Widen),从而使金属线能够承受随机缺陷带来的影响,如图所示。

在版图关键区域分析阶段,若线扩展与加宽操作未能使版图热点分布与数量有所减小,则需要重新进行布线,并将绕线模式设置为Density-Driven,这样可以实现更均匀的走线分配与更小的走线间距。

5、Filler 单元的插入(Filler Cell Insertion)

即在版图中密度低的区域插入一些填充单元(包括标准单元填充物与金属填充物)来使版图密度保持均匀,使在化学机械抛光过程获得较好的平坦效果。为避免图形平坦过程中出现侵蚀、凹陷现象,需要保持芯片整体密度的均匀性、一致性。任何影响导线横截面的工艺都必须小心控制:第一点:宽金属的侵蚀会减少其电流承载能力,使金属线IR-Drop 更加严重,所以控制这一点对电源网络分布至关重要。第二点:金属线的侵蚀会使信号线的电阻变大,进而增加信号线上的延时。通常的做法是在版图布线完成后在标准单元间隙插入填充单元(Filler Cell),填充单元是在标准单元库中定义的与电路逻辑无关的填充物。

)

- 前端开发需要了解的工具集合:webpack, eslint, prettier, ...)