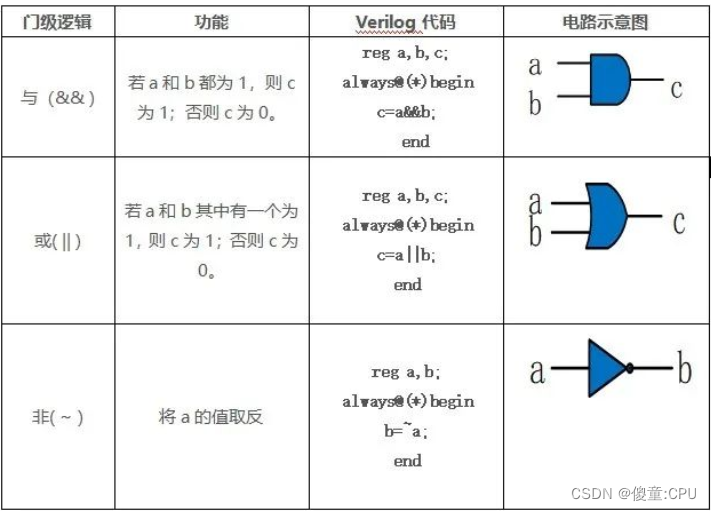

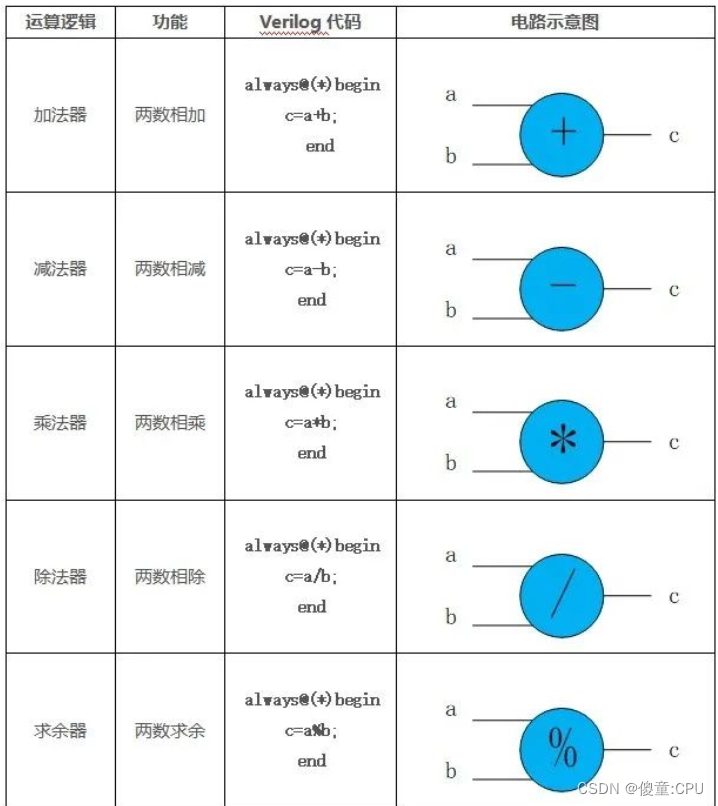

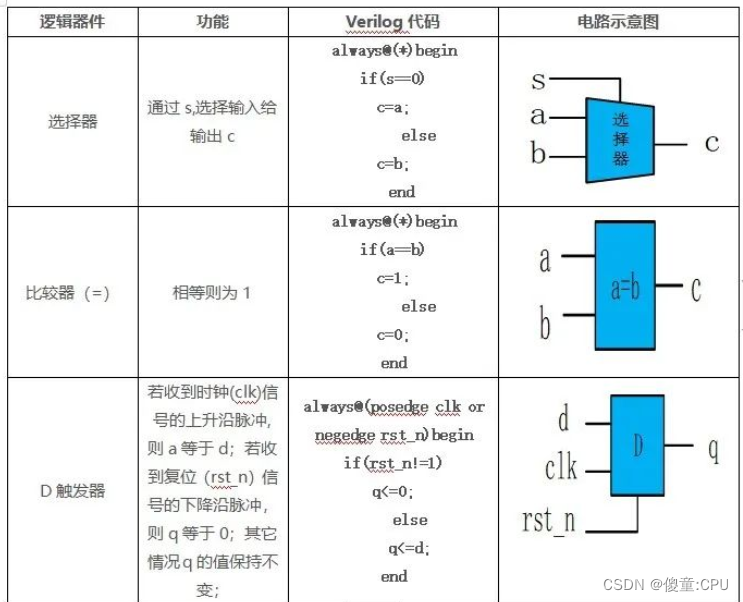

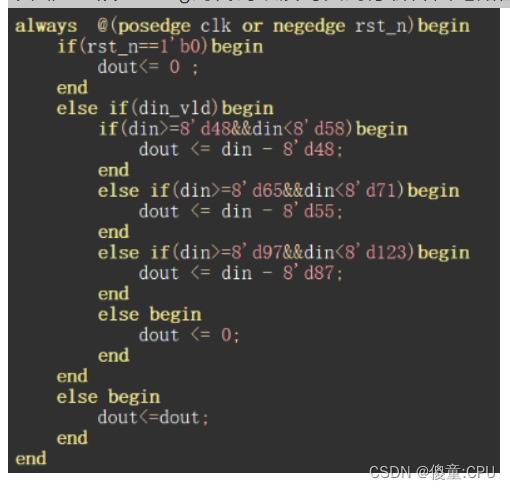

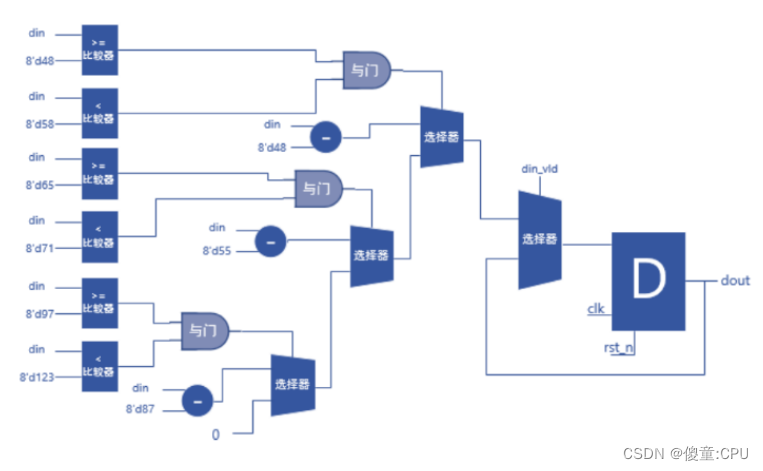

根据verilog代码画电路图

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.mzph.cn/news/242722.shtml

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈email:809451989@qq.com,一经查实,立即删除!相关文章

VS2015编译boost 1.62.0

参考链接: http://blog.chinaunix.net/uid-22301538-id-3158997.html

D:\boost_1_62_0>bjam –toolsetmsvc-14.0 –prefixD:/boost_1_62_0/output –without-python –build-typecomplete linkshared threadingmulti install

复数矩阵分解的拆解思路(矩阵求逆/特征值分解)

作者:桂。 时间:2017-10-26 07:11:02 链接:http://www.cnblogs.com/xingshansi/p/7735016.html 前言 主要记录特征值分解的硬件实现思路。 一、实数矩阵转化 在FPGA运算中,对实数运算通常优于对复数运算。假设C为复数矩阵&#…

贷款机构如何审核个人征信?

贷款是要查看征信的, 但是大家知道贷款机构是如何审查借款人的征信吗?下面我们一起来看下。1看征信报告打印时间一般贷款机构要求提供的是最新的征信报告,当然每个机构要的具体期限不一样,有的要求是最近一个月的,有的…

VS2015 + CUDA 8.0 配置GTX1070的OpenCL 开发环境

一、查看计算机对OpenCL异构计算的支持情况

使用 GPU Caps Viewer 查看计算机对OpenCL的支持情况,目前最新的版本是 gpu-caps-viewer-1-32-0, 下载地址:http://www.geeks3d.com/20161107/gpu-caps-viewer-1-32-0-released/ 从上面两个图可以…

空间谱专题16:间距选取分析

作者:桂。 时间:2017-11-01 23:26:30 链接:http://www.cnblogs.com/xingshansi/p/7769153.html 前言 本文主要分析布阵间距选取依据,个人观点,仅供参考。 一、问题描述 对于空间谱测向(以MUSIC算法为例&a…

征信逾期了,5年后能自动消除吗?

最近有一个朋友去申请贷款,然后被拒了,理由是属于征信黑名单。这个朋友很纳闷,自己最近几年从来没有贷过款,信用卡每个月都是正常在还,没有出现逾期过,为何说征信是黑名单呢?后来一问才知道&…

什么样的人去贷款最受银行欢迎?

去贷款,大家是不是都想着所有的流程都能一次性顺利通过,而且拿到的贷款额度高,利息低?这是理想的一种状态,但是贷款不是你自己说了算的,而是贷款公司说了算,所以做一个让贷款公司喜欢的人将能更…

网贷申请技巧,提高90%通过率

目前网贷很流行,深受大家欢迎,而且网贷简单方便,所以是解决短期缺钱一个很好的渠道。但是网贷也不是那么好撸的,想要提高网贷的通率,你得学会一些技巧。一、申请贷款准备1、联系客服不要盲目的去申请贷款,因…

格雷码与二进制的转换

格雷码与二进制的转换

格雷码转二进制码的基本思路:

格雷码转二进制是从左边第二位起,将每位与左边一位二进制码的值异或,作为该位二进制码后的值(最左边一位依然不变)。

以其中一个为例:格雷码111-&g…

度量、符号、转换关系

作者:桂。 时间:2017-11-19 10:13:49 链接:http://www.cnblogs.com/xingshansi/p/7859240.html Power Ratio:能量比,如果幅度,需要平方转化。s.t. y 10log10(x) 参考:《Electronic Warfare and Radar Sy…

Intel CPU集成显卡被UEFI BIOS禁用想开启的设置

台式机处理器为i7-6700k, 带有HD Graphics 5300, 想用来做OpenCL开发,然后下载了intel_sdk_for_opencl_setup_6.3.0.1904.exe, 做了demo,发现识别不到OpenCL Platform, 在设备管理器中一看,发现集成显卡不见…

使用SystemVerilog门模型描述的组合逻辑

使用SystemVerilog门模型描述的组合逻辑

模块和文件

组合逻辑是无状态的,换言之,输人的变化立即反映在输出的改变上。 SystemVerilog的基本构造单元是模块(module)。

module And2 (input wire x,y,output wire z);assign z = x & y;endmodule模块描述从关键字module开…

去银行贷款,有中介和没中介的巨大差别

说到贷款中介,很多朋友可能第一想法是没必要,自己去贷款,贷款机构审核的是自己,能不能贷款完全取决于个人条件,所以没必要找中介,更不需要额外多支付中介费。如果这些话是那些优质的客户说出来,…

组合逻辑块的测试平台

组合逻辑块的测试平台

测试平台是不需要综合的,因此SystemVerilog的所有语法都可以用来编写测试平台。测试平台的模块不需要声明输入和输出,测试平台包括了被测试对象、产生测试激励的信号源及观察或记录被测对象输出的机制。 测试平台通常实现两大功能:1)产生被测模块所需…

)