概述

verilog c代码

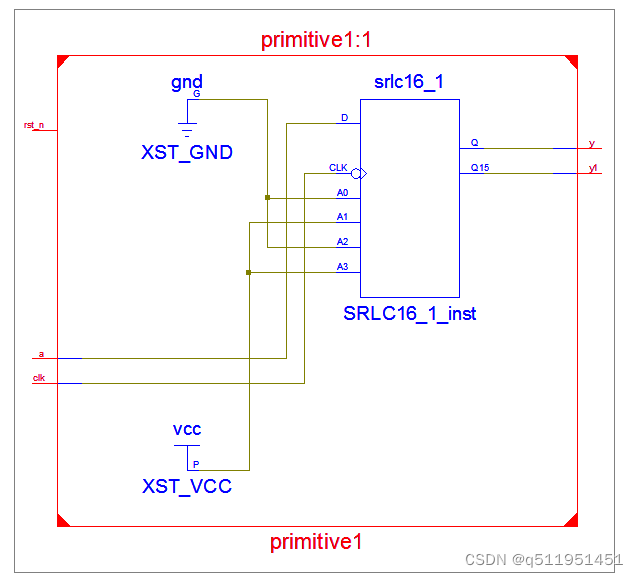

module primitive1(input clk , // system clock 50Mhz on boardinput rst_n, // system rst, low active input a , output y1, // output signaloutput y // output signal);SRLC16_1 #(.INIT(16'h0000) // Initial Value of Shift Register

) SRLC16_1_inst (.Q(y), // SRL data output.Q15(y1), // Carry output (connect to next SRL).A0(0), // Select[0] input.A1(1), // Select[1] input.A2(0), // Select[2] input.A3(1), // Select[3] input.CLK(clk), // Clock input.D(a) // SRL data input

);endmodule

原语代码

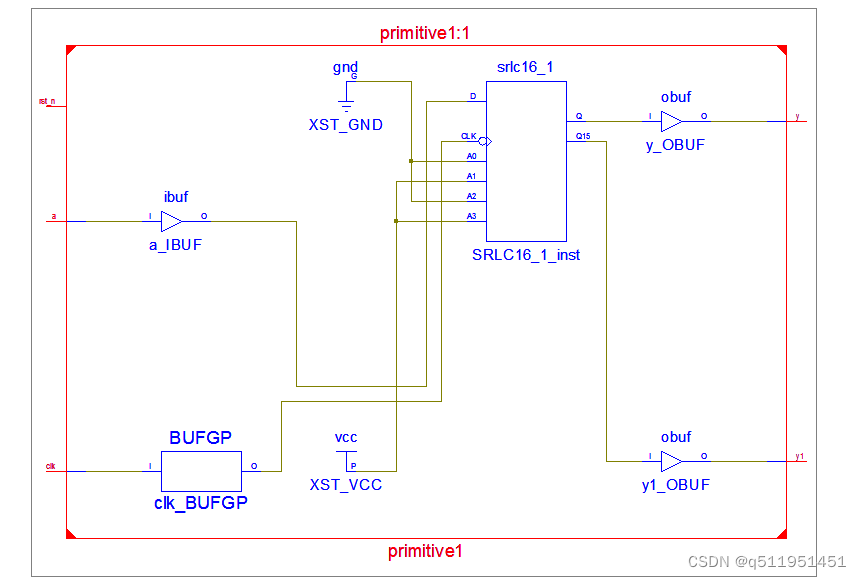

module primitive1 (clk, rst_n, a, y, y1

);input clk;input rst_n;input a;output y;output y1;wire N0;wire N1;wire a_IBUF_3;wire clk_BUFGP_5;wire y1_OBUF_8;wire y_OBUF_9;GND XST_GND (.G(N0));VCC XST_VCC (.P(N1));SRLC16_1 #(.INIT ( 16'h0000 ))SRLC16_1_inst (.A0(N0),.A1(N1),.A2(N0),.A3(N1),.CLK(clk_BUFGP_5),.D(a_IBUF_3),.Q(y_OBUF_9),.Q15(y1_OBUF_8));IBUF a_IBUF (.I(a),.O(a_IBUF_3));OBUF y_OBUF (.I(y_OBUF_9),.O(y));OBUF y1_OBUF (.I(y1_OBUF_8),.O(y1));BUFGP clk_BUFGP (.I(clk),.O(clk_BUFGP_5));

endmoduleRTL结构图

技术原理图

)

)

)

)

)

】)

详解)