芯片行业是个高风险、高投入的行业,做一款芯片仅仅是开模的费用就是百万起。

从设计到制造都是环环相扣的,设计过程中的BUG或者错误能够达到上千个。

所以验证是保证芯片功能正确性和完整性最重要的一环。(文末有学习视频哦~)

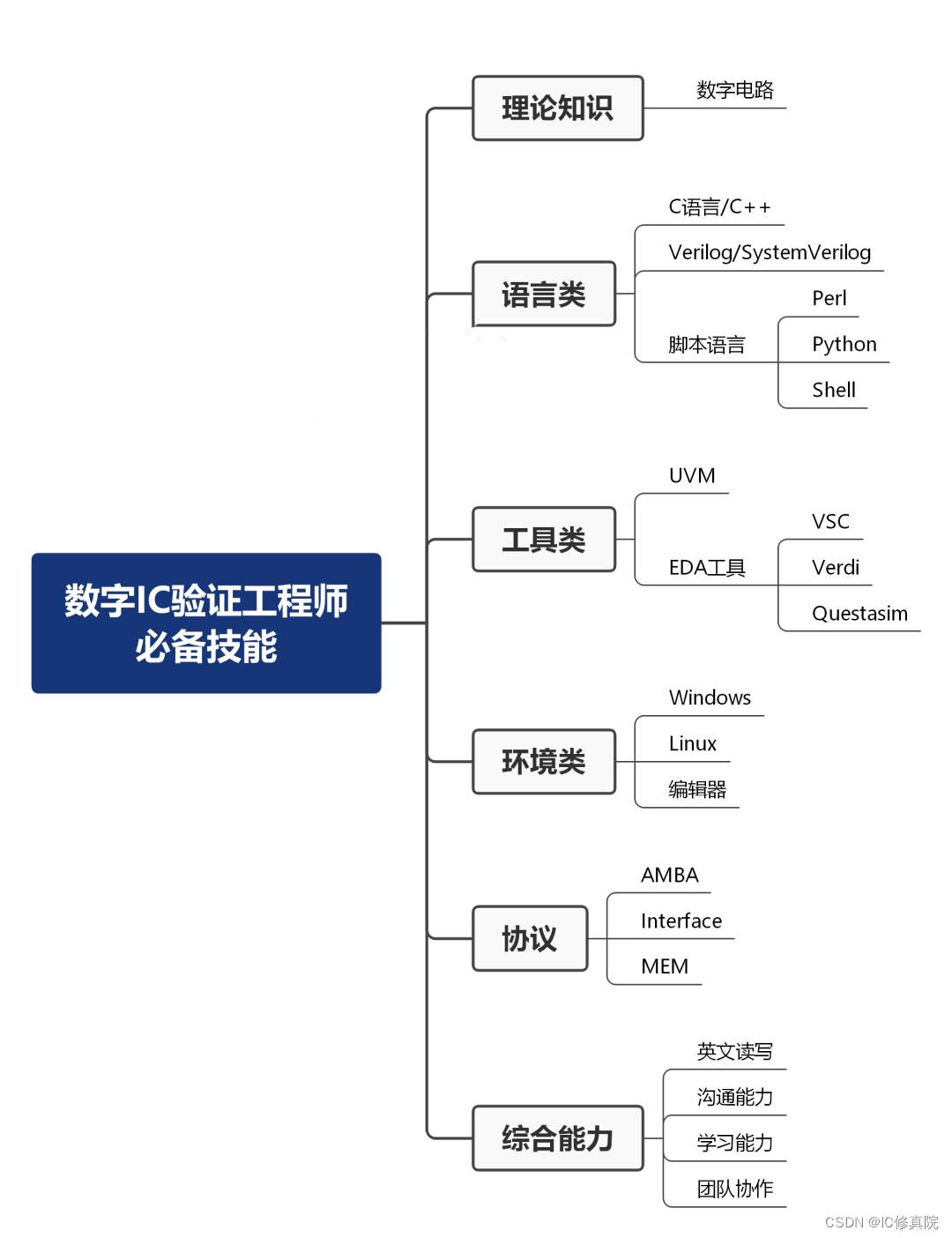

验证工程师的必备技能?

这里罗列的是数字IC验证工程师需要具备的技能,是要用所有“资源”点满的。

理论知识

说起理论知识,数电知识是做数字芯片的基石,也是很多同学入行学习的第一本书,一定是需要先掌握的。可以理解为自带的被动技能。

语言类

先来看Q技能,语言。验证工程师们需要使用各种验证语言去搭建验证环境。常用的验证语言有C、C++和StemVerilog。

验证岗位对Verilog语言的要求是能够看懂、能够理解的程度,并不需要像设计岗位那样精通。

System Verilog就属于验证工程师的核心技能了,随着设计越来越复杂,为了更方便例化模块,所以SV语言也是越来越流行。

工具类

再来看W技能,验证工具。UVM是现在主流的验证方法学,同样属于验证工程师必备的核心技能。当验证环境和测试用例都搭建好后,就需要进行仿真和debug了。

EDA仿真工具,不同公司使用的工具软件不同,但大都是三巨头家的(Synopsys、Cadence、Mentor)。掌握并熟练使用这些EDA工具,能够很大程度上提升仿真和debug效率。

环境类

接下来是E技能,环境。EDA工具基本都提供的是Linux版本,芯片设计公司提供的开发环境也都是Linux。所以需要熟练掌握Linux环境下的常用命令和操作。处理文本需要使用到编辑器,比如VIM,所以对于编辑器同样要做到熟练使用。

协议类

除了验证的一些基本技术之外。IP中还会使用到很多协议,所以验证工程师还需要了解各种通用协议。如果说前面的技能都属于基础的话,协议就属于进阶类型的技能了,可以直接理解为大招。

学习书籍推荐

SV和UVM

SV和UVM就这两本书,想学习的话可以先找视频看一下,SV看第一遍看不懂没关系,再看看书就懂得差不多了,然后学习UVM,UVM是基于SV的验证方法学,把 UVM 的结构理清楚,这对于验证非常重要。

IC验证视频学习

SV随机化约束的种类和控制

SOC项目介绍和spec讲解

更多免费视频可点击下方链接领取哦,或者想要了解行情,薪资,岗位的同学也可以通过下方链接进行了解~

这里给大家放个入口:芯片设计入门了解/更多视频课资料领取

)

深度学习硬件)

)

:排序(2):计数排序)

——情况一)

)