TIMING-14 : 时钟树上的 LUT

在时钟树上发现 LUT <cell_name> 。不建议在时钟路径上包含 LUT 单元。

描述

时钟路径上的 LUT 可能导致偏差过大 , 因为时钟必须在穿过互连结构的常规布线资源上进行布线。除偏差过大外 , 这些路径更易于受到 PVT 变动的影响。强烈建议尽可能避免使用局部时钟。

解决方案

解决方案是更改设计 , 移除位于时钟树上的 LUT 。综合可能会在时钟门控和反相等许多情况下出现此状况。对于反相LUT1 单元 , 完成 opt_design 后可能会将 LUT 吸收到下游 slice 中。请调查此状况 , 确保完成 opt_design 后此情况仍有效。

示例

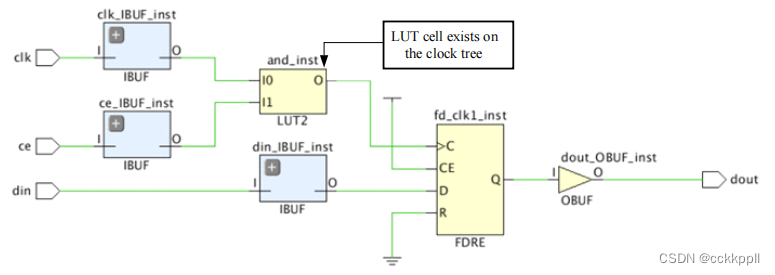

在下图中 , 使用 LUT 对含时钟使能信号的时钟进行门控。路径上的 LUT 可能导致偏差过大。

TIMING-15 : 时钟间路径上的严重保持时间违例

在 <cell_name> ( 由 <clock_name> 进行时钟设置 ) 与 <cell_name> ( 由 <clock_name> 进行时钟设置 ) 之间存在 <value ns 的严重的时钟间偏差 , 此偏差导致存在 <VALUE> ns 的严重保持时间违例。布线期间修复严重的保持时间违例可能会影响建立时间裕量, 导致时序收敛难度提升。

描述

DRC 警告报告称由于时钟间偏差导致严重的保持时间违例 , 可能导致实现期间难以达成时序收敛。建议对大于 1.0 ns的严重的时钟间偏差进行调查, 以确保约束或设计拓扑结构正确。

解决方案

调查时序路径上的时钟间严重偏差是否应定时 , 或者是否与未最优化的时序约束有关。如果由于未约束的 CDC 路径而导致发生严重偏差, 请添加必要的时序例外。如果由于与时钟树关联的逻辑而导致发生违例 , 请调查是否可通过改进路径的拓扑结构来更轻松地收敛时序。

TIMING-16 : 建立时间严重违例

在 <cell_name> ( 由 <clock_name> 进行时钟设置 ) 与 <cell_name> ( 由 <clock_name> 进行时钟设置 ) 之间存在 <value> ns 的建立时间严重违例。这些阶段结束时出现的建立时间严重违例可能难以在布局后实现流程期间进行修复, 原因可能是 XDC 约束或设计架构未最优化。

描述

此 DRC 警告用于报告在实现期间较难以达成时序收敛的建立时间违例。建议对大于 1.0 ns 的建立时间违例进行调查 ,以确保约束或设计拓扑结构正确。

解决方案

调查建立时间严重违例是否源于应定时的时序路径 , 或者违例是否与未最优化的时序约束有关。如果由于未约束的CDC 路径而导致发生建立违例 , 请添加必要的时序例外。如果由于存在大量组合逻辑而导致发生违例 , 请调查是否可通过改进路径的拓扑结构来更轻松地收敛时序。

TIMING-17 : 未设置时钟的时序单元

时序时钟无法到达时钟管脚 <pin_name> 。

描述

DRC 报告可列出不受时序时钟约束的时序单元 , 此类时序单元会影响针对报告的单元所生成的时序分析。强烈建议正确定义所有时钟以实现最大范围的时序路径覆盖, 并保证最高的准确性。否则可能因缺失时序分析而导致硬件故障。

解决方案

解决办法是在驱动未约束的时序单元的时钟树上创建缺失的基准时钟或生成时钟。

TIMING-18 : 输入或输出延迟缺失

在 <port_name> 上缺失与 <clock_name> 时钟相关的 <input/output> 延迟。

描述

IO 时序与包含外部器件的时序路径有关。输入和输出延迟可指定与设计接口处的时钟沿相关的端口路径延迟。强烈建议添加输入/ 输出延迟约束 , 以确保 FPGA 接口可满足外部器件的时序要求。

解决方案

添加对应于必需的开发板应用的必需输入和输出延迟约束。

)

)

)

![2024 年 20 款最佳免费视频转换器软件 [安全快速有效]](http://pic.xiahunao.cn/2024 年 20 款最佳免费视频转换器软件 [安全快速有效])

)