引言

在之前的文章中,我们介绍了索尼、安森美以及三星等Sensor厂家在车载领域中的技术论文,分析了各个厂家不同的技术路线、Sensor架构以及差异点。今天,笔者借豪威科技在移动端200Mega Pixels产品的技术论文,讲解消费级CIS传感器的基本架构、工艺以及与车载应用不同之处。

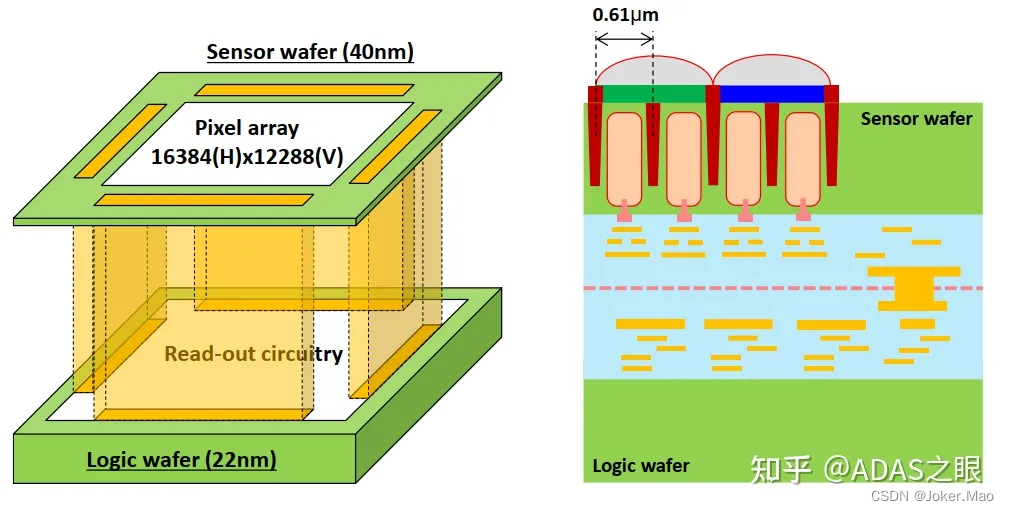

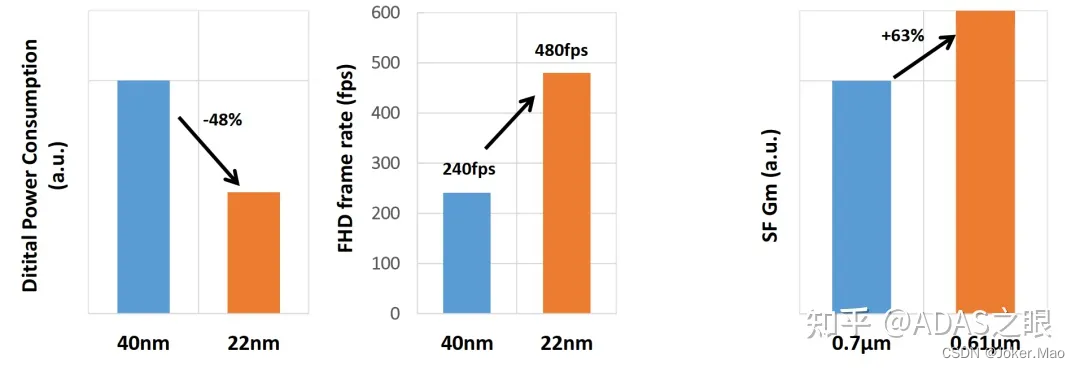

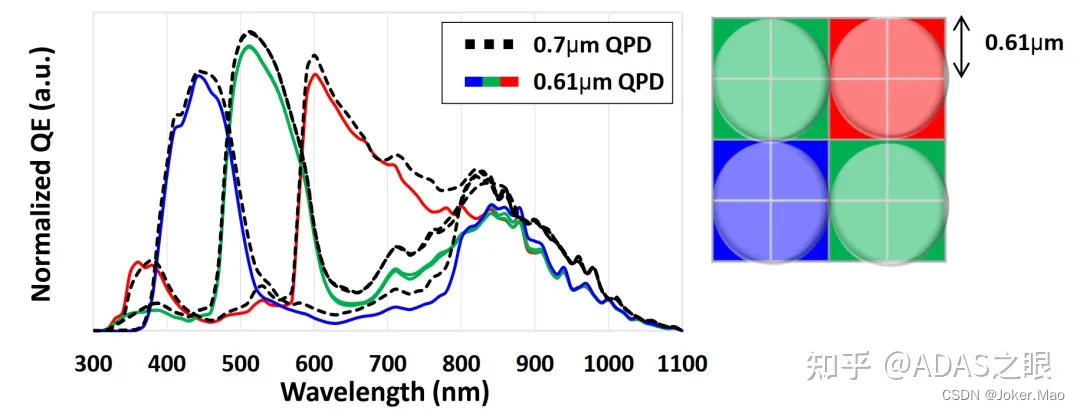

本项工作开发了一种新的40/22nm堆叠式、像素尺寸为0.61µm、200兆像素CMOS图像传感器(CIS)。通过使用22nm逻辑晶圆工艺节点代替40nm完成数字逻辑部分,在保持相同时钟频率的同时,数字功耗降低了一半,同时全高清(FHD)帧速率从240fps提高到480fps。在这项工作中,我们展示了一种新的源极跟随器(SF)晶体管架构,与我们以前的0.7µm像素相比,SF跨导(Gm)高出63%。实现了5.0ke-的全阱容量(FWC),与0.7µm像素相比,具有更好的白像素(WP)性能。我们展示了0.61µm四元光电二极管(QPD)结构,该结构能够在可见光范围内实现与0.7µm QPD相当的量子效率(QE)性能。

1. Introduction

手机行业领域发展迅速,由于各个手机厂商着重于提高多摄像头移动设备的图像质量,因此对高分辨率和小像素间距图像传感器的需求一直在稳步增加。尽管像素间距缩放低于可见光衍射极限,但由于图像信号处理的逐步改进,仍能继续实现更好的图像质量。

高分辨率图像传感器需要更低的功耗和更快的读出速度,因为传感器必须同时管理大量像素。晶片堆叠工艺应用于高分辨率CIS,其中像素和读出电路分别在像素和逻辑晶片中实现,从而允许每个晶片工艺针对其自身目的进行优化。通过在逻辑晶片中采用先进的工艺节点,可以在不影响像素晶片的情况下实现更低的功耗和更快的读出。此外,通过采用先进的工艺节点,可以在更小的面积内以更低的功耗在逻辑晶片中实现更多的图像信号处理器功能,如像素装仓模式或可切换转换增益(SCG)。

此外,小像素间距需要SF晶体管和光电二极管的尺寸收缩。SF晶体管宽度越窄,Gm越小,这是读取速度的重要参数,尤其是在高分辨率图像传感器中。在高分辨率图像传感器中,每个像素阵列列的位线变得更长,导致位线稳定时间更长,导致读取速度更低。时间常数 t, 对于位线可以表示为t = RC=(1/Gm+Rload)C,其中Rload和C分别是位线的负载电阻和寄生电容。从表达式中可以看出t 与Gm成反比。

较小的光电二极管尺寸降低FWC和暗特性。为了获得更高的FWC,必须增加光电二极管的n型离子注入剂量和光电二极管之间隔离处的p型离子注入量,以实现合理的隔离势垒。然而,增加的n型/p-型离子注入剂量会产生高电场,从而降低通过有缺陷的光电二极管硅表面的暗电流和WP。因此,设计更小的光电二极管需要n型/p-型离子注入剂量调谐和硅表面缺陷改善。在这项工作中,我们提出了一种新的CIS,它解决了上述与高分辨率和小像素间距图像传感器有关的问题。

2. Pixel架构与技术

2.1 Sensor架构

下图显示了传感器的框图和横截面,该传感器使用OmniVision Gen2堆叠技术:

传感器晶片采用CIS专用40nm工艺节点。在逻辑晶片中,新采用了22nm工艺节点,而不是我们以前的小像素堆叠传感器中使用的40nm工艺节点。模拟和数字电路针对22nm工艺节点进行了设计和优化,与40nm工艺节点相比,实现了更低的功耗和更高的读出速度。

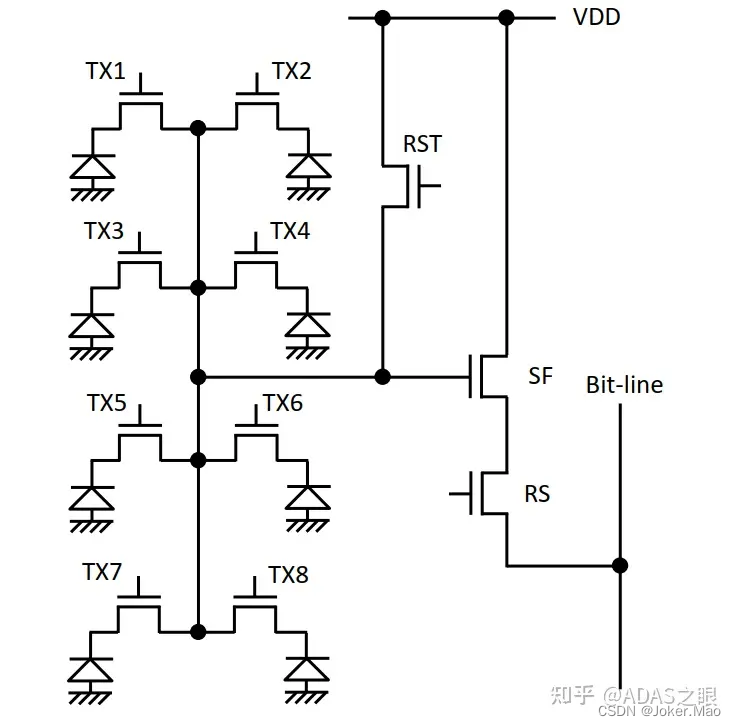

传感器的像素阵列大小为200兆像素(16384(H)x 12288(V)),光学格式为1/1.28”,像素间距为0.61µm。采用2x4共享架构,其电路示意图如下所示:

2.2 Pixel布局

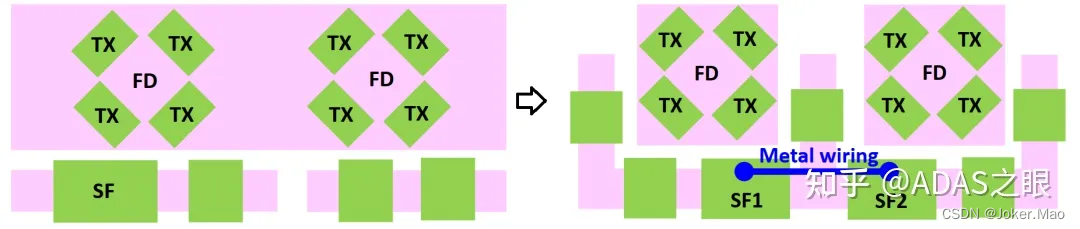

下图显示了本工作中使用的传统布局和新布局之间的像素晶体管布局转变比较(左为传统布局,右为新布局):

每个晶体管通过浅沟槽隔离(STI)进行隔离。在新布局中,两个SF通过金属布线并联连接,这提供了更大的SF宽度。通过采用垂直传输门(VTG),可以将光电二极管转移到更深的硅区域,允许在光电二极管上放置晶体管,从而在晶体管设计中提供更大的灵活性。两个SF的较大SF宽度即使在较小的像素间距中也可以提高Gm,从而在200兆像素CIS中给出合理的位线时间常数。我们还采用了背面深沟槽隔离(BDTI)来隔离每个像素,改善了光学串扰。STI、VTG和BDTI的组合允许对正面和背面硅进行独立的布局优化,使其适合小像素开发。此外,正如上图所示,我们可以包括一个额外的晶体管,它可以用于高动态应用的SCG。

2.3 Pixel性能改进

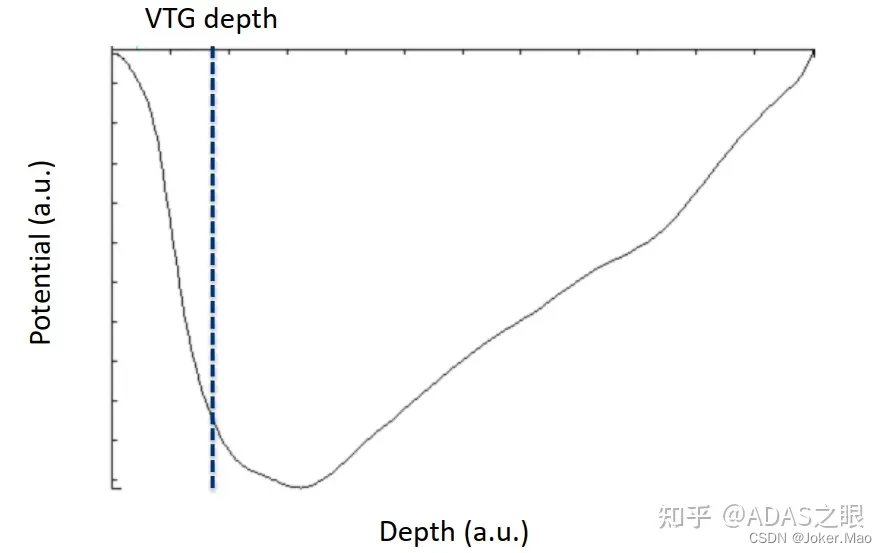

下图显示了深度方向上传感器光电二极管电位剖面的TCAD模拟:

通过增加n型/p-型离子注入剂量和优化电势分布,避免了像素间距收缩导致的FWC降低。我们可以看到,在不牺牲滞后或开花的情况下,潜力在深度上平滑地扩展以增加FWC。然而,由于位于缺陷硅表面的较高电场而导致的暗电流或WP的退化是另一个问题,特别是在通过蚀刻工艺产生缺陷的BDTI界面中。我们采用了最新的BDTI流程,从而改进了WP。

由于较小的片上透镜(OCL)填充因子,小间距像素遭受显著的QE退化。QPD,或具有2x2 OCL的Quad Bayer编码,是一种在2x2像素阵列中使用一个OCL和相同滤色器的设计,可产生高分辨率和高动态范围的图像传感器。QPD是改善小像素图像传感器量化的一项重要技术,并在本工作中得到了实现。

3. 实验与对比

3.1 帧率&Gm指标

与40nm工艺节点相比,22nm工艺节点能够在保持相同时钟频率的同时将数字功耗降低一半,并将FHD帧率从240fps提高到480fps。同时与0.7µm相比,0.61µm像素显示出63%的SF-GM改善,在2亿像素图像传感器中实现了合理的位线常数,如下图所示:

3.2 满井容量

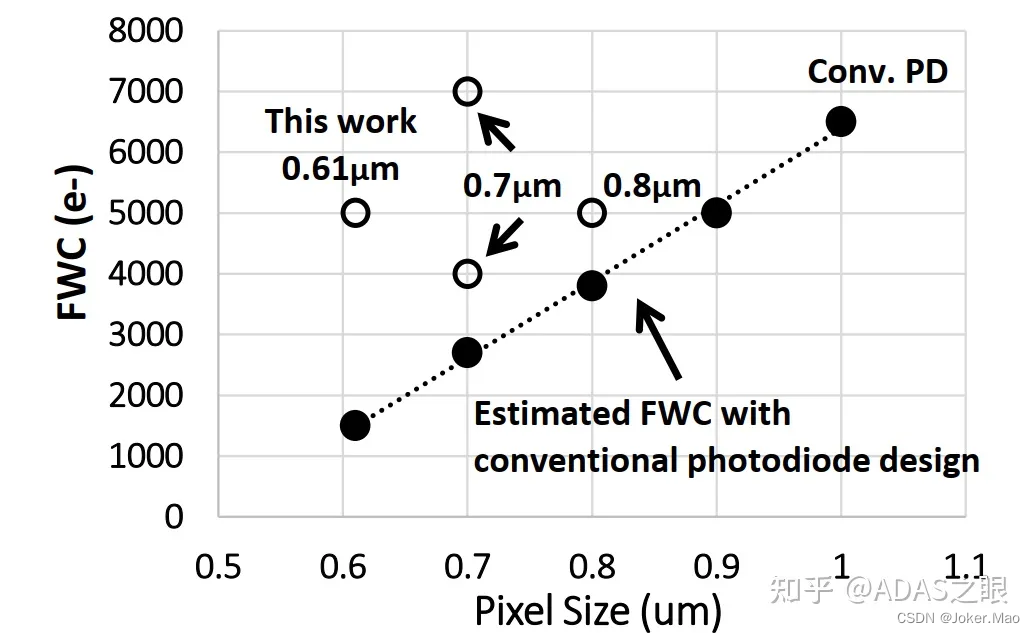

下图显示了与像素间距相关的FWC趋势:

填充的圆圈和虚线代表了基于1.0µm像素的简单像素区域缩放所实现的FWC。空圈显示了我们上一代0.8µm和0.7µm技术的数据。可以看出,0.8µm和0.7µm FWC远高于简单缩放预测的值;这一改进是由深光电二极管技术实现的,该技术在深硅地区精心设计了潜力。我们采用了同样的技术,我们重新设计了0.61µm,在没有滞后的情况下实现了5.0KE-FWC。

3.3 白像素数量

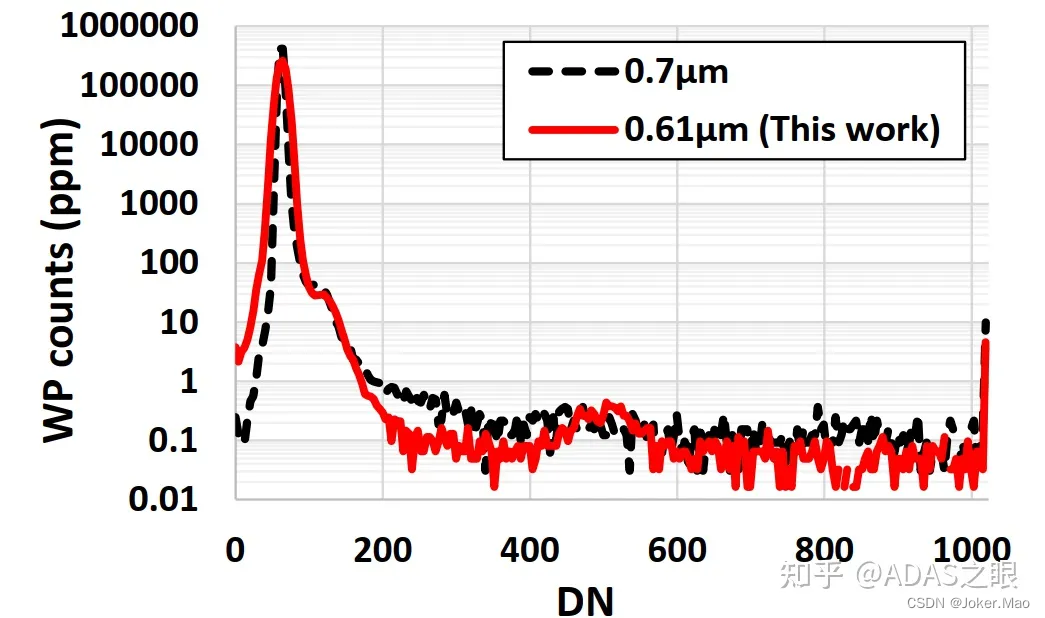

与0.7µm相比,0.61µm像素的WP直方图有所改善,如下图所示:

尽管我们增加了N型/P型离子注入剂量,导致电场更高,但与上一代相比,我们最新的BDTI技术使WP得到了改善。

3.4 QE

下图显示了0.7µm和0.61µm像素之间的QPD QE曲线比较:

在可见光范围内,总体QE性能与0.7µm QPD相当,但在近红外区域可以看到一些退化。

4. 结论

我们开发了一种新的40/22nm 200兆像素堆叠图像传感器,像素大小为0.61µm。表1显示了0.7µm和0.61µm像素之间的性能比较。数字功耗降低了一半,FHD帧速率从240fps提高到480fps。我们的SF-Gm提高了63%。与0.7µm像素相比,实现了5.0keFWC,没有滞后或开花,具有更好的WP性能。我们展示了在可见光范围内与0.7µm相当的QPD QE性能。

最后,该传感器拍摄的样本图像如下图所示:

5. 结束语

今天我们为大家介绍了豪威在IEEE中发表的手机端CIS传感器的技术论文,为大家介绍了消费级Sensor的实现原理与技术架构,可以看出相对于车载CIS,消费级Sensor一般不采用DCG、SubPixel等方式提高DR,因为这样会导致成本的提升。同时其Pixel Size相对于车载也小了很多,因此移动手机端实现HDR的方式一般为多帧曝光合成的方式,这也就是为什么在手机拍摄时移动会造成明显的伪影。

好了今天就到这里,希望今天可以给您带来对于传感器的更深的认知,喜欢的同学可以进行朋友圈分享以及点击文章在看。另外,对论文感兴趣的同学可以fllow我的Github论文仓库AdasTechPapers,公众号回复较慢,后续讲解的论文会在仓库中开源。

如果您对ADAS感兴趣,欢迎关注我的公众号、知乎、Github、CSDN等,同时发表文章中使用源码以及文章会在我的GitHub进行开源,如果您有感兴趣话题也可以后台私信。同时,也欢迎加入我的知识星球以及交流群,获取行业信息、技术论文等一手资料~

如果您对ADAS感兴趣,欢迎关注我的公众号、知乎、Github、CSDN等,同时发表文章中使用源码以及文章会在我的GitHub进行开源,如果您有感兴趣话题也可以后台私信。

)

)

)

《Linux操作系统原理分析之linux存储管理(2)》(18))