目录

- 工作原理

- 发射器 TRANSMITTER(Tx)

- 接收器 RECEIVER (Rx)

- 观测接收器 OBSERVATION RECEIVER (ORx)

- 嗅探接收器 SNIFFER RECEIVER(SnRx)

- 时钟输入 CLOCK INPUT

- SYNTHESIZERS合成

- RF PLL射频锁相环

- Clock PLL时钟锁相环

- External LO Inputs外部LO输入

- 串行外设接口 SERIAL PERIPHERAL INTERFACE(SPI)

- GPIO_x AND GPIO_3P3_x PINS GPIO_x 和 GPIO_3P3_x 引脚

- AUXILIARY CONVERTERS辅助转换器

- 辅助ADC输入 Auxiliary ADC Inputs(AUXADC_x)

- Auxiliary DACs (AUXDAC_x) 辅助DAC (AUXDAC_x)

- JESD204B数据接口 JESD204B DATA INTERFACE

- 电源顺序 POWER SUPPLY SEQUENCE

- 数字预失真(DPD) DIGITAL PREDISTORTION

- JTAG BOUNDARY SCAN JTAG边界扫描

工作原理

AD9371是一款高度集成的RF收发器,可针对各种应用进行配置。该器件在单个器件中集成了提供发射和接收功能所需的所有射频、混合信号和数字模块。可编程性允许将两个接收器通道和两个发射器通道用于 3G 和 4G 蜂窝标准的 TDD 和 FDD 系统。

观测接收机(ORx)通道有两个输入,用于监测发射机输出。该通道具有宽通道带宽,可接收整个发射频段并将其反馈到数字部分以进行纠错。此外,三个嗅探接收器(SnRx)输入可以监控不同的无线电频段(一次一个)。这些通道与两个ORx输入共享基带ADC和数字处理。

AD9371包含4个用于发送链的高速串行接口链路和4个由Rx、ORx和SnRx通道共享的高速串行接口链路(符合JESD204B,子类1标准),为现场可编程门阵列(FPGA)或其他定制集成基带解决方案提供低引脚数和可靠的数据接口。

AD9371还利用集成微控制器内核为直流失调、LO泄漏和正交误差校正提供自校准功能,以在不同的温度和输入信号条件下保持高性能水平。固件随设备一起提供,无需用户交互即可安排所有校准。该器件包括测试模式,允许系统设计人员在原型设计期间调试设计并优化无线电配置。

发射器 TRANSMITTER(Tx)

AD9371采用直接变频发送器架构,由两个相同且独立控制的通道组成,提供实现直接变频系统所需的所有数字处理、混合信号和RF模块。两个通道共用一个频率合成器。来自JESD204B通道的数字数据通过一个完全可编程的 96 抽头 FIR 滤波器,并带有可选的插值功能。FIR输出被发送到一系列转换滤波器,这些滤波器在到达DAC之前提供额外的滤波和数据速率插值。每个DAC都具有可调采样速率,并且一直线性至满量程。

当转换为基带模拟信号时,同相(I)和正交(Q)信号被滤波以消除采样伪影,然后将信号馈送到上变频混频器。在混频器级,I和Q信号被重新组合并调制到载波频率上,以便传输到输出级。每个发射链都提供宽衰减调整范围和细粒度,以帮助设计人员优化信噪比。

接收器 RECEIVER (Rx)

AD9371内置双接收器通道。每个Rx通道都是一个直接变频系统,包含一个可编程衰减器级,后接匹配的I和Q混频器,将接收到的信号下变频到基带进行数字化。

为了实现增益控制,该器件实现了编程增益指数图。该增益图在各个Rx模块之间分配衰减,以便在每个功率电平下实现最佳性能。此外,还支持自动和手动增益控制模式。

接收器包括 Σ-Δ ADC 和可调采样率,可从接收信号产生数据流。信号可以通过一系列抽取滤波器和一个完全可编程的 72 抽头 FIR 滤波器(具有额外的抽取设置)进一步调节。每个数字滤波器模块的采样率可通过改变抽取因子进行调节,以产生所需的输出数据速率。

观测接收器 OBSERVATION RECEIVER (ORx)

ORx 的工作方式与主接收器类似。每个输入都是差分的,并使用专用混频器。ORx输入共用一个基带ADC和基带部分;因此,任何时候都只能有一个处于活动状态。混合信号和数字部分在设计和操作上与主接收器通道相同。该通道可以监视Tx通道并实现纠错功能。它也可以用作通用接收器。

嗅探接收器 SNIFFER RECEIVER(SnRx)

嗅探器接收器提供三个差分输入,可以监控不同的频段。每个输入端都有一个低噪声放大器(LNA),该放大器经过多路复用,为单个混频器供电。该混频器级的输出与ORx接收器混频器多路复用,以馈送相同的基带部分。SnRx 带宽限制为 20 MHz。如果给定应用的带宽和射频性能可接受,则该接收器也可以用作通用接收器。嗅探器通道在 400 MHz 至 4000 MHz 范围内的工作受到限制,对于高于 4000 MHz 的 LO 设置,无法保证性能。

这些接收器输入还提供 LNA 旁路模式,当存在大信号时,该模式会消除 LNA 的增益。

时钟输入 CLOCK INPUT

AD9371需要一个差分时钟连接到DEV_CLK_IN+/DEV_CLK_IN−引脚。时钟输入的频率必须介于10 MHz和320 MHz之间,并且必须具有非常低的相位噪声,因为该信号会产生RF本振和内部采样时钟。

SYNTHESIZERS合成

RF PLL射频锁相环

AD9371内置三个小数N分频PLL,用于生成发射机、接收机和观测接收机使用的RF LO。PLL内置一个内部VCO和环路滤波器,无需外部元件。内部 VCO LDO 稳压器消除了 PLL 额外外部电源的需要。这些稳压器只需要为每个电源提供一个外部旁路电容。

Clock PLL时钟锁相环

AD9371内置一个PLL频率合成器,可生成所有与基带相关的时钟信号和SERDES时钟。该PLL根据系统的数据速率和采样速率要求进行编程。

External LO Inputs外部LO输入

AD9371提供两个外部LO输入,允许与器件一起使用的外部合成器。这些输入必须为所需LO频率的2×。请注意,外部LO选项的操作限制为最大4000 MHz。一对输入专用于接收器LO生成电路,另一对输入为发射器和观测接收器LO生成模块提供输入。请注意,观测接收机可以从Tx LO发生器模块或其自己的专用PLL获取LO。当嗅探器通道使能时,该模块的LO只能来自专用的内部观察通道PLL。

串行外设接口 SERIAL PERIPHERAL INTERFACE(SPI)

AD9371使用SPI与基带处理器(BBP)通信。该接口可以配置为具有专用接收和发送端口的 4 线接口,也可以配置为具有双向数据通信端口的 3 线接口。该总线允许 BBP 使用简单的地址数据串行总线协议设置所有器件控制参数。写入命令遵循 24 位格式。第一位设置总线传输的总线方向。接下来的 15 位设置写入数据的地址。最后八位是传输到特定寄存器地址的数据。

读取命令遵循类似的格式,不同之处在于前 16 位在 SDIO 引脚上传输,最后 8 位从 AD9371 读取,在 4 线模式下在 SDO 引脚上读取,在 3 线模式下在 SDIO 引脚上读取。

GPIO_x AND GPIO_3P3_x PINS GPIO_x 和 GPIO_3P3_x 引脚

AD9371以VDD_IF电源为基准的通用输入/输出信号可针对多种功能进行配置。其中一些引脚在配置为输出时,被 BBP 用作实时信号,以提供许多内部设置和测量。此配置允许 BBP 在不同情况下监控接收机性能。指针寄存器选择输出到这些引脚的信息。用于手动增益模式、校准标志、状态机状态和各种接收器参数的信号都是可通过这些引脚监控的输出。此外,某些引脚可以配置为输入,并用于各种功能,例如实时设置接收器增益。

该器件还包括以VDDA_3P3电源为基准的GPIO_3P3_x引脚,可以向外部元件(如 VGA 或 RF 部分的衰减器)提供控制信号,这些元件通常使用较高的基准电压。

AUXILIARY CONVERTERS辅助转换器

辅助ADC输入 Auxiliary ADC Inputs(AUXADC_x)

AD9371内置一个辅助ADC,该ADC多路复用至四个输入引脚(AUXADC_0至AUXADC_3)。该模块可以监控系统电压,而无需添加额外的组件。辅助ADC为12位,输入电压范围为0.05 V至VDDA_3P3 − 0.25 V。使能时,辅助ADC自由运行。软件对输出值的读取提供锁存于ADC输出端的最后一个值。

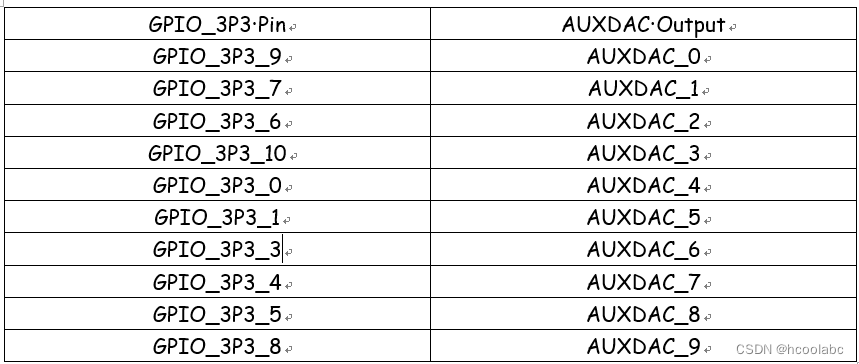

Auxiliary DACs (AUXDAC_x) 辅助DAC (AUXDAC_x)

AD9371内置10个相同的辅助DAC(AUXDAC_0至AUXDAC_9),可提供偏置电压、模拟控制电压或其他系统功能。这些辅助DAC的输入(AUXDAC_0至AUXDAC_9)与GPIO_3P3_x引脚多路复用,如表7所示。辅助DAC为10位,输出电压范围约为0.5 V至VDDA_3P3 − 0.3 V,电流驱动为10 mA。

表 7.AUXDAC输入引脚分配

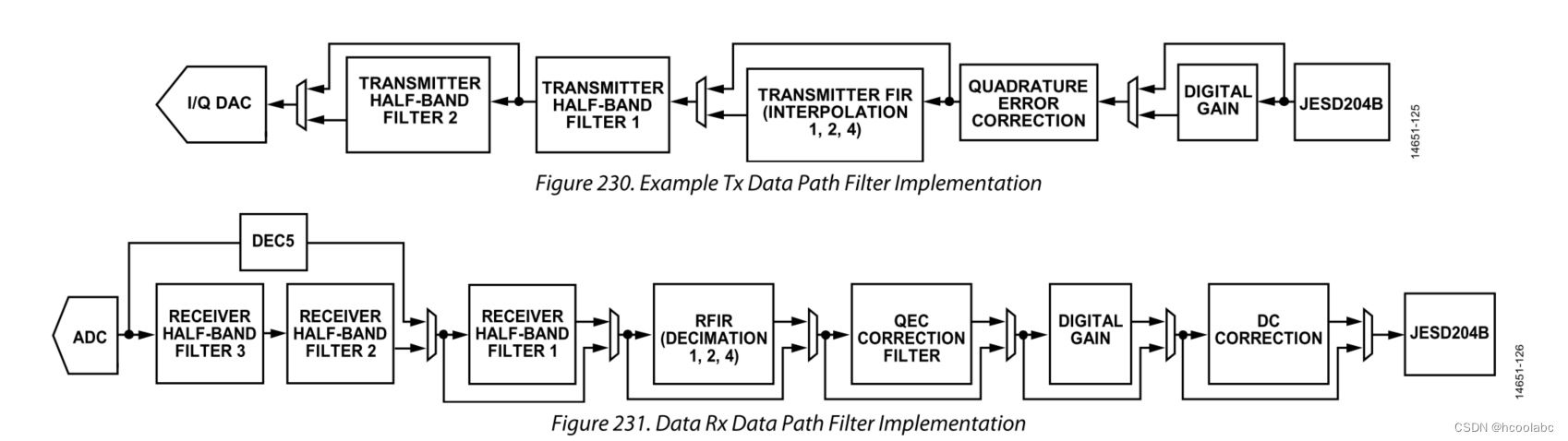

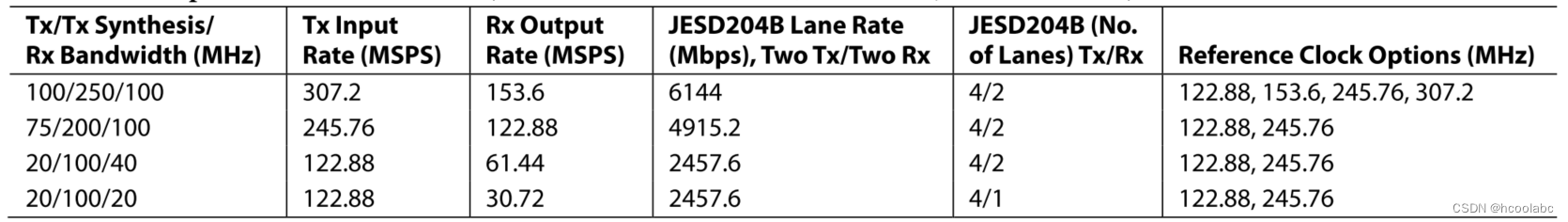

JESD204B数据接口 JESD204B DATA INTERFACE

AD9371的数字数据接口采用JEDEC标准JESD204B子类1。串行接口的工作速度高达 6144 Mbps。JESD204B接口的优点包括减少数据接口布线所需的电路板面积,以及由于需要更少的引脚而提供更小的封装选项。所有接收器和发射器路径中都包含数字滤波,以提供适当的信号调理和采样率,以满足JESD204B数据要求。Tx和Rx路径的数字滤波配置示例分别如图230和图231所示。

Table 8. Example Rx/Tx Interface Rates (Two Rx/Two Tx Channels, Maximum JESD Lane Rates) Rx/Tx 接口速率示例(2 个 Rx/2 Tx 通道,最大 JESD 通道速率)

电源顺序 POWER SUPPLY SEQUENCE

AD9371需要特定的上电时序,以避免不需要的上电电流。最佳上电顺序通过同时上电VDIG和VDDA_1P3(模拟)电源来启动该过程。如果它们不能同时上电,VDIG电源必须首先上电。然后,VDDA_3P3、VDDA_1P8和JESD_VTT_DES电源必须在 VDIG 和VDDA_1P3电源之后上电。请注意,VDD_IF电源可以随时通电。还建议在配置前在电源稳定后切换 RESET 信号。按照上电顺序的相反顺序进行断电。

请注意,VDDA_1P3是指所有模拟1.3 V电源,包括:VDDA_BB、VDDA_CLKSYNTH、VDDA_TXLO、VDDA_RXRF、VDDA_RXSYNTH、VDDA_RXVCO、VDDA_RXTX、VDDA_TXSYNTH、VDDA_TXVCO、VDDA_CALPLL、VDDA_SNRXSYNTH、VDDA_SNRXVCO、VDDA_CLK和VDDA_RXLO。

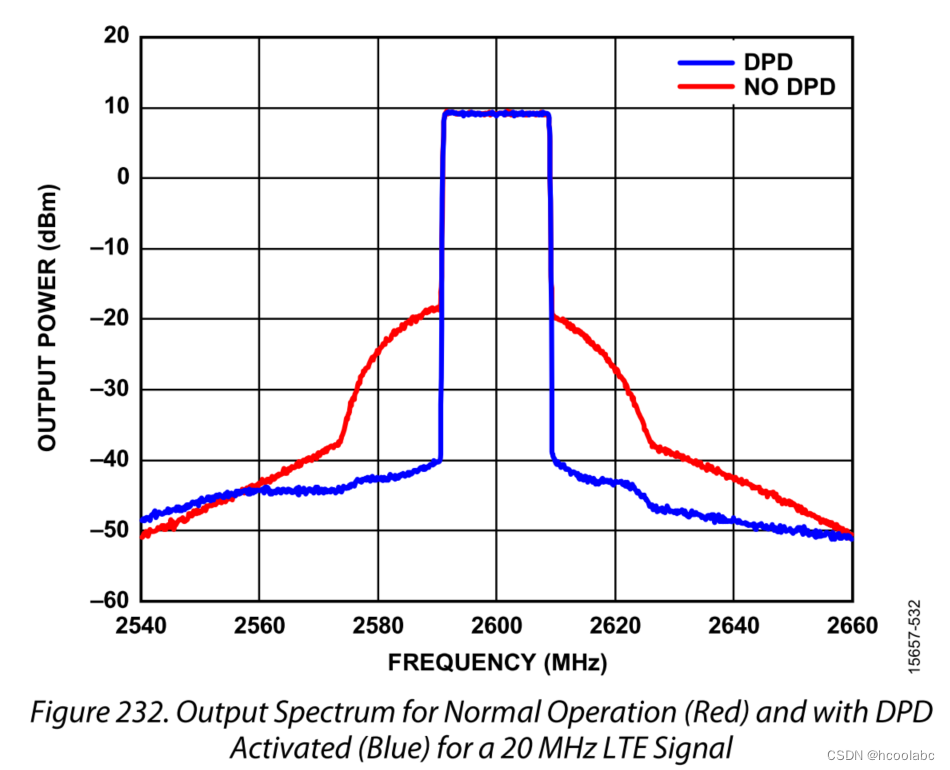

数字预失真(DPD) DIGITAL PREDISTORTION

AD9375 额外增加功能

该器件提供完全集成的 DPD 功能,通过改变数字波形来补偿 PA 响应中的非线性,从而对发射系统的功率放大器 (PA) 的输出进行线性化。DPD执行器和系数计算引擎都集成在一起。此功能使用 ORx 通道来监视 PA 的输出,并计算适当的预失真以使输出线性化。集成的 DPD 功能使系统能够使 PA 更接近饱和,从而在保持线性度的同时实现更高效率的 PA。DPD 针对均方根输出功率范围为 250 mW 至 10 W 的小型蜂窝 PA 进行了优化,最大占用信号带宽为 40 MHz。启用时,DPD 模块消耗的额外功率小于 100 mW。

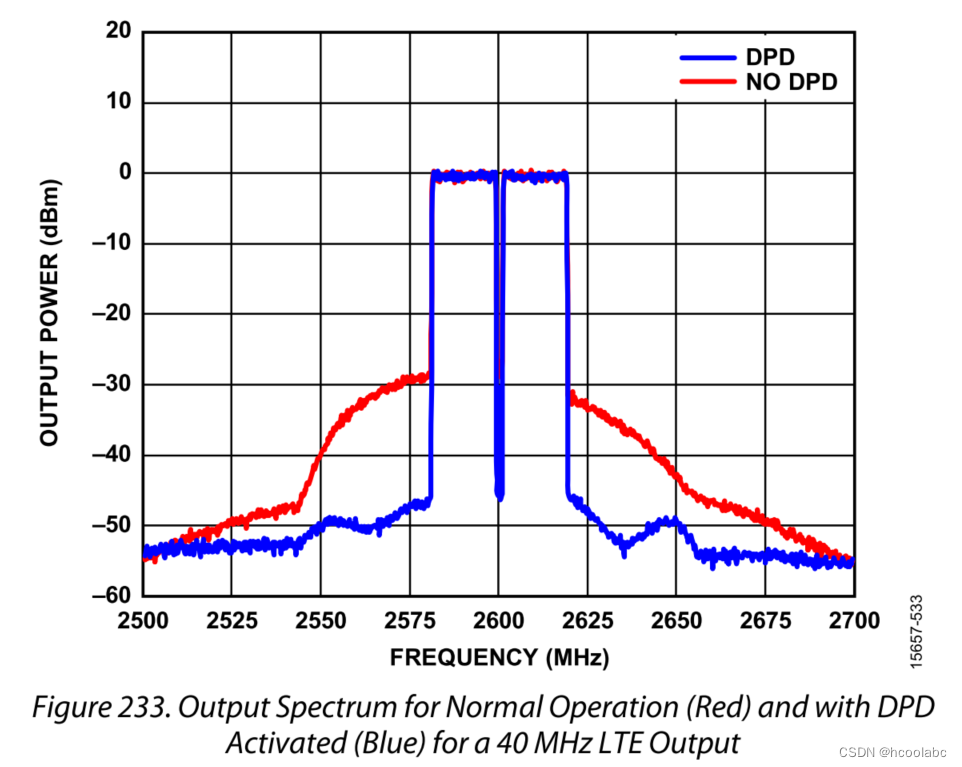

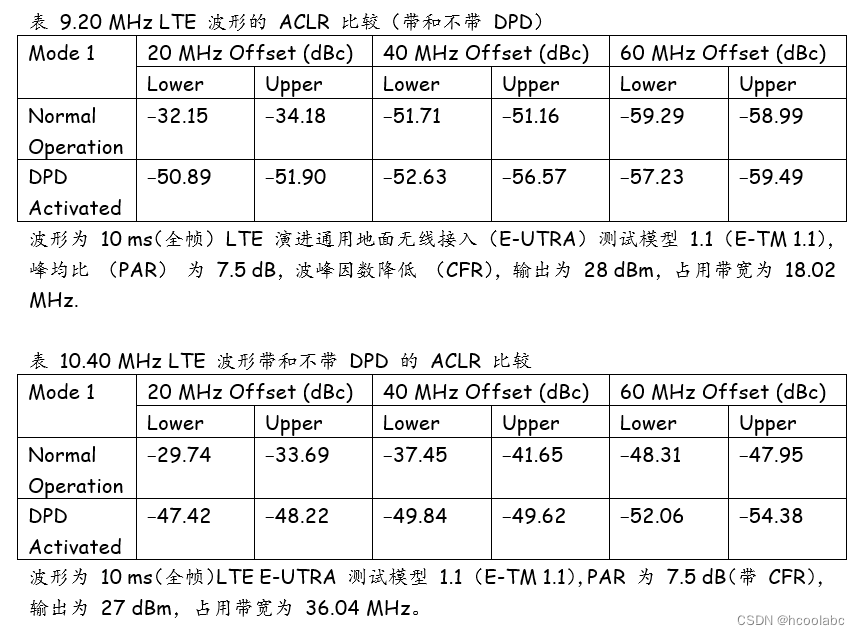

图 232 显示了 20 MHz LTE 信号的性能增强,图 233 显示了 40 MHz LTE 输出的性能增强。在这两种情况下,频段 7 Skyworks SKY66297 高效 PA 都用于演示特定设备的临道泄露抑制比(ACLR) 改进。表 9 和表 10 显示了激活 DPD 时在这两种情况下实现的 ACLR 改进的详细信息。请注意,ACLR的改善幅度很大程度上取决于PA,并且通常会随着信号带宽的增加而降低。

JTAG BOUNDARY SCAN JTAG边界扫描

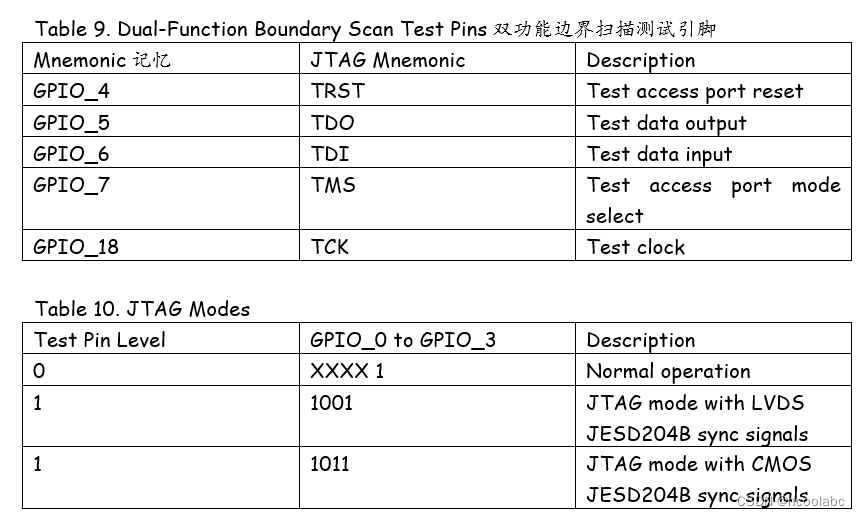

AD9371支持JTAG边界扫描。有五个双功能引脚与JTAG接口相关联。这些引脚如表9所示,用于访问片上测试访问端口。要启用JTAG功能,请根据在软件(LVDS或CMOS模式)中配置所需的JESD204B同步引脚(即SYNCINB0+、SYNCINB0−、SYNCINB1+、SYNCINB1−、SYNCBOUTB0+或SYNCBOUTB0−)的方式,根据表10设置通过GPIO_3引脚的GPIO_0。将TEST引脚拉高以启用JTAG模式。

)

)

)

)