专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

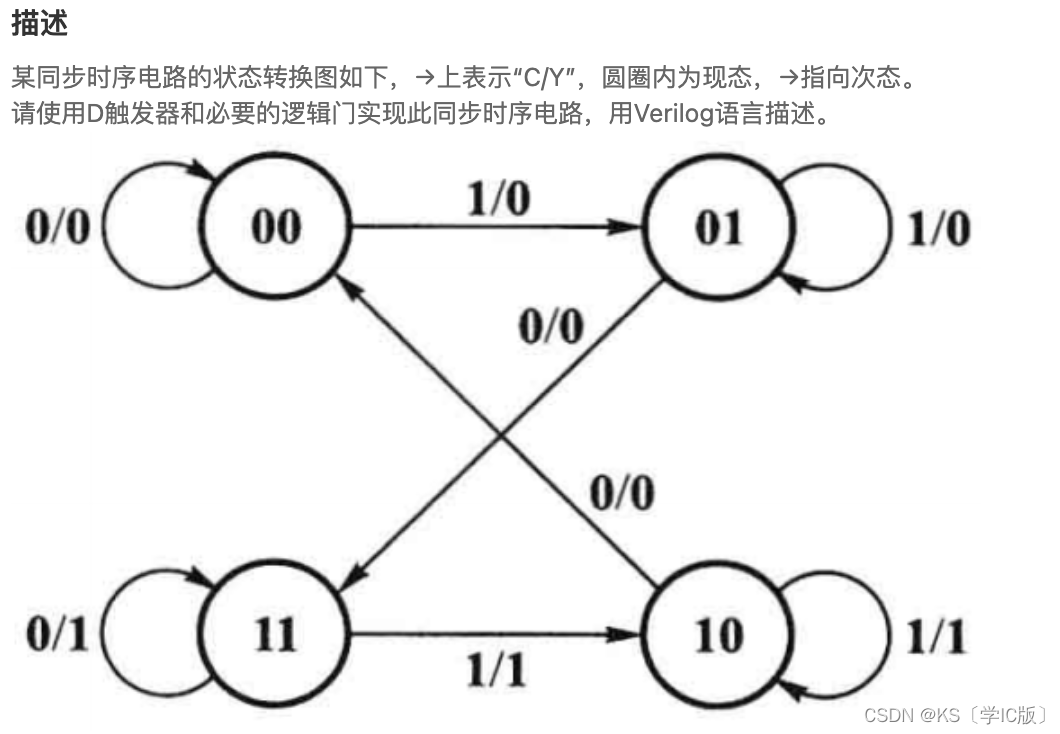

这是一个典型的米利型状态机。三段式即可解决。

米利型状态机:即输出不仅和当前状态有关,也和输入有关。 其中ST0,ST1,ST3的输出可以化简,化简后和C无关。 但是ST2的输出,需要判断输入C。

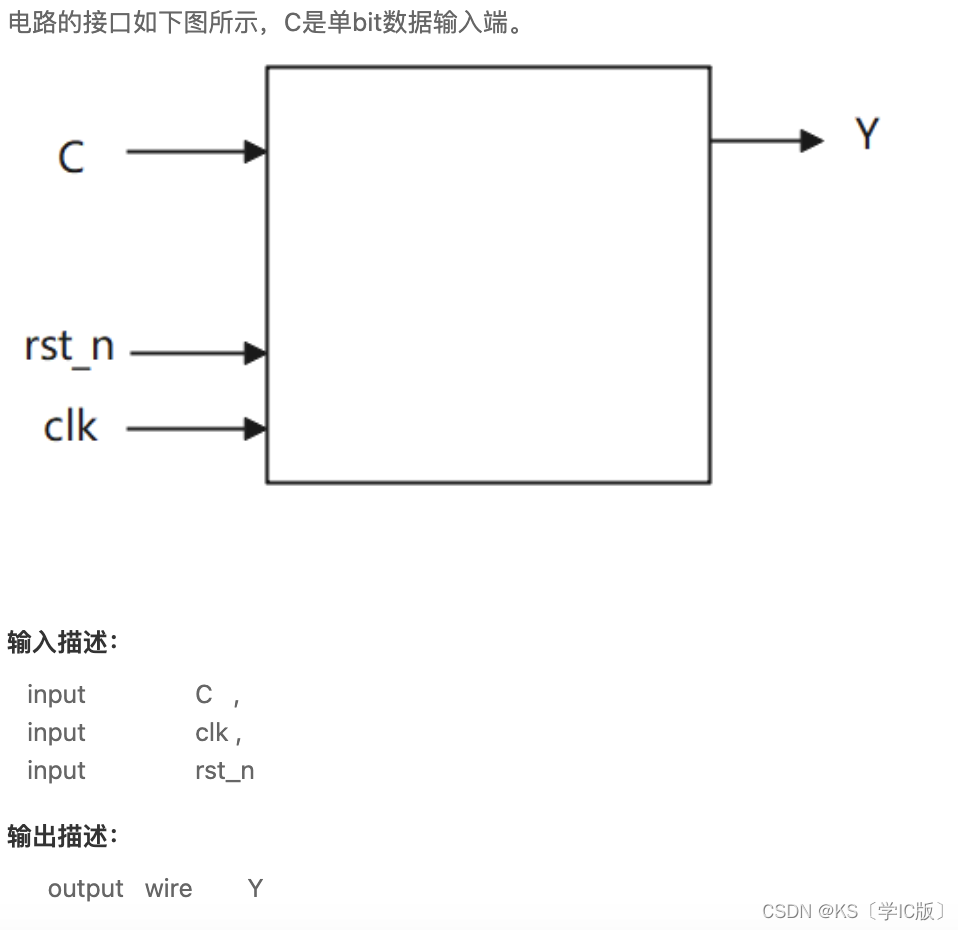

`timescale 1ns/1nsmodule seq_circuit(input C ,input clk ,input rst_n,output wire Y

);parameter ST0 = 2'b00 ; parameter ST1 = 2'b01 ; parameter ST2 = 2'b10 ; parameter ST3 = 2'b11 ; reg [1:0] cur_state ; reg [1:0] nxt_state ; reg Y_r ; always @ (posedge clk or negedge rst_n) begin if (!rst_n) cur_state <= ST0 ; else cur_state <= nxt_state ; end always @ (*) begin case (cur_state) ST0 : begin if (C == 1'b0) nxt_state <= ST0 ; else nxt_state <= ST1 ; end ST1 : begin if (C == 1'b0) nxt_state <= ST3 ; else nxt_state <= ST1 ; end ST2 : begin if (C == 1'b0) nxt_state <= ST0 ; else nxt_state <= ST2 ; end ST3 : begin if (C == 1'b0) nxt_state <= ST3 ; else nxt_state <= ST2 ; end endcase endalways @ (*) begin case (cur_state) ST0 : begin Y_r <= 1'b0 ; end ST1 : begin Y_r <= 1'b0 ; end ST2 : begin if (C == 1'b0) Y_r <= 1'b0 ; else Y_r <= 1'b1 ; endST3 : begin Y_r <= 1'b1 ; end endcaseendassign Y = Y_r ;endmodule

)

)

)