AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

JESD204B相关IP端口信号 : AD9371 官方例程HDL JESD204B相关IP端口信号

裸机程序配置 AD9528、AD9371、FPGA IP: AD9371 官方例程裸机SW 和 HDL配置概述(一)

AD9371 主函数: AD9371 官方例程 NO-OS 主函数 headless 梳理(一)

AD9371 主函数: AD9371 官方例程 NO-OS 主函数 headless 梳理(二)

文章目录

- 前言

- 一、TXDeframer 的 DAC Crossbar 和 Lane Crossbar

- 二、RXFramer 的 ADC Crossbar 和 Lane Crossbar

- 三、ObsRxFramer 的 ADC Crossbar 和 Lane Crossbar

- 四、TX 的 I、Q 映射关系

- 五、RX 的 I、Q 映射关系

- 六、RX_OS 的 I、Q 映射关系

- 七、测试

- 八、总结

前言

从FPGA中的 JESD204B 传输层 tx/rx 基带数据时,I、Q两路 谁占据传输层 组/解帧 时转换器 M0 的位置,谁占据转换器 M1 的位置,才能正确通过AD9371射频 ?

TX传输层要求格式 , [ M3S1, M3S0, M2S1, M2S0, M1S1, M1S0, M0S1, M0S0]

RX传输层输出格式 , [ M3S0, M2S0, M1S0, M0S0]

RX_OS传输层输出格式,[ M1S1, M1S0, M0S1, M0S0]

Lane通道之间的连接关系见 AD9371 官方例程之 tx_jesd 与 xcvr接口映射

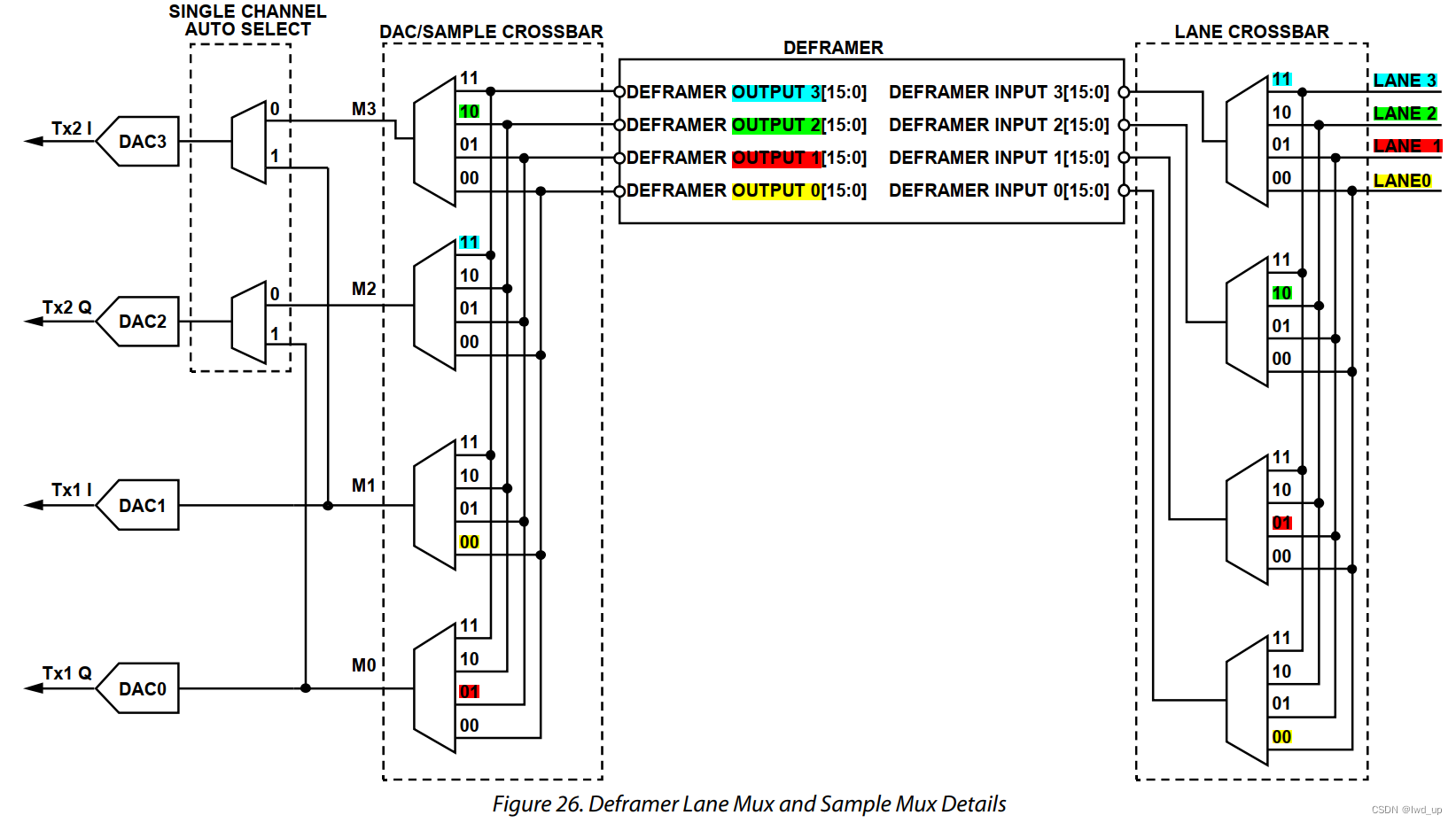

一、TXDeframer 的 DAC Crossbar 和 Lane Crossbar

官方例程 TX 分配 4个 LANE和4个转换器M

DAC Crossbar 被一直配置为 framerADC_XBar = 0xB1 = 1011 0001

Lane crossbar 被一直配置为 laneXbar= 0xE4 = 1110 0100;

即 :

LANE0 —> DEFRAMER INPUT 0 —> DEFRAMER OUTPUT 0 —> Tx1 I

LANE1 —> DEFRAMER INPUT 1 —> DEFRAMER OUTPUT 1 —> Tx1 Q

LANE2 —> DEFRAMER INPUT 2 —> DEFRAMER OUTPUT 2 —> Tx2 I

LANE3 —> DEFRAMER INPUT 3 —> DEFRAMER OUTPUT 3 —> Tx2 Q

即:

SERDIN0 ——> LANE 0 ——>DEFRAMER INPUT 0 ——> DAC0 ——> DEFRAMER OUTPUT 0 ——> Tx1 I

SERDIN1 ——> LANE 1 ——>DEFRAMER INPUT 1 ——> DAC1 ——> DEFRAMER OUTPUT 1 ——> Tx1 Q

SERDIN2 ——> LANE 2 ——>DEFRAMER INPUT 2 ——> DAC2 ——> DEFRAMER OUTPUT 2 ——> Tx2 I

SERDIN3 ——> LANE 3 ——>DEFRAMER INPUT 3 ——> DAC3 ——> DEFRAMER OUTPUT 3 ——> Tx2 Q

二、RXFramer 的 ADC Crossbar 和 Lane Crossbar

官方例程 RX 分配 2个 LANE和4个转换器M

ADC Crossbar 被一直配置为 framerADC_XBar = 0xB1=1011 0001

Lane Crossbar 根据RX 转换器M 的数量

M=4,framerLaneXbar = 0x08=0000 1000; 使用 Rxframer outputs 0 and 2

M=2,framerLaneXbar = 0x04; 使用 Rxframer outputs 0 and 1

文章后续默认 M=4,framerLaneXbar = 0x08;

Rx1 I ——>RXFramer INPUT 0 ——>ADC0 ——> RXFramer OUTPUT 0 ——> LANE 0 ——> SERDOUT0

Rx1 Q ——>RXFramer INPUT 1 ——>ADC1 ——> RXFramer OUTPUT 0 ——> LANE 0 ——> SERDOUT0

Rx2 I ——>RXFramer INPUT 2 ——>ADC2 ——> RXFramer OUTPUT 2 ——> LANE 1 ——> SERDOUT1

Rx2 Q ——>RXFramer INPUT 3 ——>ADC3 ——> RXFramer OUTPUT 2 ——> LANE 1 ——> SERDOUT1

三、ObsRxFramer 的 ADC Crossbar 和 Lane Crossbar

官方例程 ObsRx 分配 2个 LANE和2个转换器M

ADC Crossbar 被一直配置为 framerADC_XBar = 0xB1=1011 0001

Lane Crossbar 被一直配置为 framerLaneXbar = 0x40=0100 0000; 使用 ObsRxframer outputs 0 and 1

Rx_OS I ——> ObsRxFramer INPUT 0 ——>ADC0 ——> ObsRxFramer OUTPUT 0 ——> LANE 2 ——> SERDOUT2

Rx_OS Q ——>ObsRxFramer INPUT 1 ——>ADC1 ——> ObsRxFramer OUTPUT 1 ——> LANE 3 ——> SERDOUT3

四、TX 的 I、Q 映射关系

第一节内容结合 Lane通道之间的连接关系 AD9371 官方例程之 tx_jesd 与 xcvr接口映射 ,可得到TX:

tx_phy0(tx_jesd) ——> SERDIN0 ——> Tx1 I

tx_phy1(tx_jesd) ——> SERDIN1 ——> Tx1 Q

tx_phy2(tx_jesd) ——> SERDIN2 ——> Tx2 I

tx_phy3(tx_jesd) ——> SERDIN3 ——> Tx2 Q

链路层:

而在 axi_ad9371_tx_jesd/tx IP核逻辑中输入数据 tx_data 经过加扰,字符替换标志后,输出 phy_data

tx_data(tx_jesd) ——> phy_data (tx_jesd)

phy_data [ 31: 0] (tx_jesd) = tx_phy0(tx_jesd)

phy_data [63:32] (tx_jesd) = tx_phy1(tx_jesd)

phy_data [95:64] (tx_jesd) = tx_phy2(tx_jesd)

phy_data [127:96] (tx_jesd)= tx_phy3(tx_jesd)

传输层

dac_ddata(tpl_core) ——> link_tdata(tpl_core) ——> tx_data(tx_jesd)

dac_ddata 格式 :[ M3S1, M3S0, M2S1, M2S0, M1S1, M1S0, M0S1, M0S0]

经过 组帧得到 link_tdata,link_tdata格式 Octets LSB first :

[ M3S1[OL], M3S0[OL], M2S1[OL], M2S0[OL], M1S1[OL], M1S0[OL], M0S1[OL], M0S0[OL]]

注意 : MmSn[OL] = { MmSn [7:0] ,MmSn [15:8] }

即:

M0S1, M0S0 ——> M0S1[OL], M0S0[OL] ——> tx_phy0(tx_jesd) ——> SERDIN0 ——> Tx1 I

M1S1, M1S0 ——> M1S1[OL], M1S0[OL] ——> tx_phy1(tx_jesd) ——> SERDIN1 ——> Tx1 Q

M2S1, M2S0 ——> M2S1[OL], M2S0[OL] ——> tx_phy2(tx_jesd) ——> SERDIN2 ——> Tx2 I

M3S1, M3S0 ——> M3S1[OL], M3S0[OL] ——> tx_phy3(tx_jesd) ——> SERDIN3 ——> Tx2 Q

五、RX 的 I、Q 映射关系

第二节内容结合 Lane通道之间的连接关系 AD9371 官方例程之 tx_jesd 与 xcvr接口映射 ,可得到RX:

{ Rx1 Q[7:0],Rx1 Q[15:8],Rx1 I[7:0],Rx1 I[15:8] } ——> SERDOUT0 ——> rx_phy0(rx_jesd)

{ Rx2 Q[7:0],Rx2 Q[15:8],Rx2 I[7:0],Rx2 I[15:8] } ——> SERDOUT1 ——> rx_phy1(rx_jesd)

链路层:

phy_data [ 31: 0] (rx_jesd) = rx_phy0 (rx_jesd) = rx_0 (ad9371_xcvr)

phy_data [63:32] (rx_jesd) = rx_phy1 (rx_jesd) = rx_1 (ad9371_xcvr)

而在 rx_jesd/rx IP核逻辑中,输入数据 phy_data 经过解扰等操作后输出 rx_data

phy_data(rx_jesd) ——> rx_data(rx_jesd) ——> link_data(rx_ad9371_tpl_core/tpl_core)

传输层

link_data(rx_ad9371_tpl_core/tpl_core) ——> adc_data(rx_ad9371_tpl_core/tpl_core)

link_data 格式 :[ M3S0[OL], M2S0[OL], M1S0[OL], M0S0[OL]]

注意 : MmSn[OL] = { MmSn [7:0] ,MmSn [15:8] }

经过 解帧得到 adc_data,adc_data 格式 samples LSB first :

[ M3S0, M2S0, M1S0, M0S0]

即:

M1S0, M0S0 ——> M1S0[OL], M0S0[OL] ——> rx_phy0 (rx_jesd) ——> Rx1 Q,Rx1 I

M3S0, M2S0 ——> M3S0[OL], M2S0[OL] ——> rx_phy1 (rx_jesd) ——> Rx2 Q,Rx2 I

即:

Rx1 I ——> M0S0,Rx1 Q ——> M1S0,Rx2 I ——> M2S0,Rx2 Q ——> M3S0

六、RX_OS 的 I、Q 映射关系

第三节内容结合 Lane通道之间的连接关系 AD9371 官方例程之 tx_jesd 与 xcvr接口映射 ,可得到RX_OS:

Rx_OS I [OL] —— > SERDOUT2 ——> rx_2(xcvr) ——> rx_phy0(rx_os_jesd)

Rx_OS Q [OL] ——> SERDOUT3 ——> rx_3(xcvr) ——> rx_phy1(rx_os_jesd)

Rx_OS 类似 RX 中的形式,简略为 Rx_OS I、Q [OL]

链路层:

phy_data [ 31: 0] (rx_os_jesd) = rx_phy0 (rx_os_jesd) = rx_2 (ad9371_xcvr)

phy_data [63:32] (rx_os_jesd) = rx_phy1 (rx_os_jesd) = rx_3 (ad9371_xcvr)

而在 rx_os_jesd/rx IP核逻辑中,输入数据 phy_data 经过解扰等操作后输出 rx_data

phy_data(rx_os_jesd/rx) ——> rx_data(rx_os_jesd) ——> link_data(tpl_core)

传输层

link_data(tpl_core) ——> adc_data(tpl_core)

link_data 格式 :[ M1S1[OL], M1S0[OL], M0S1[OL], M0S0[OL]]

注意 : MmSn[OL] = { MmSn [7:0] ,MmSn [15:8] }

经过 解帧得到 adc_data,adc_data 格式 samples LSB first :

[ M1S1, M1S0, M0S1, M0S0]

即:

M0S1, M0S0 ——> M0S1[OL], M0S0[OL] ——> rx_phy0 (rx_os_jesd) ——> Rx_OS I

M1S1, M1S0 ——> M1S1[OL], M1S0[OL] ——> rx_phy1 (rx_os_jesd) ——> Rx_OS Q

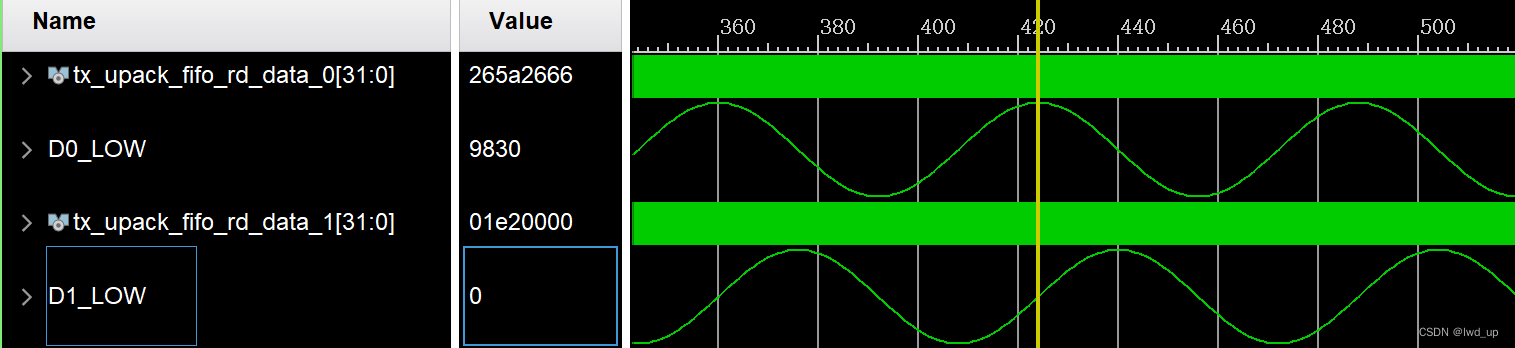

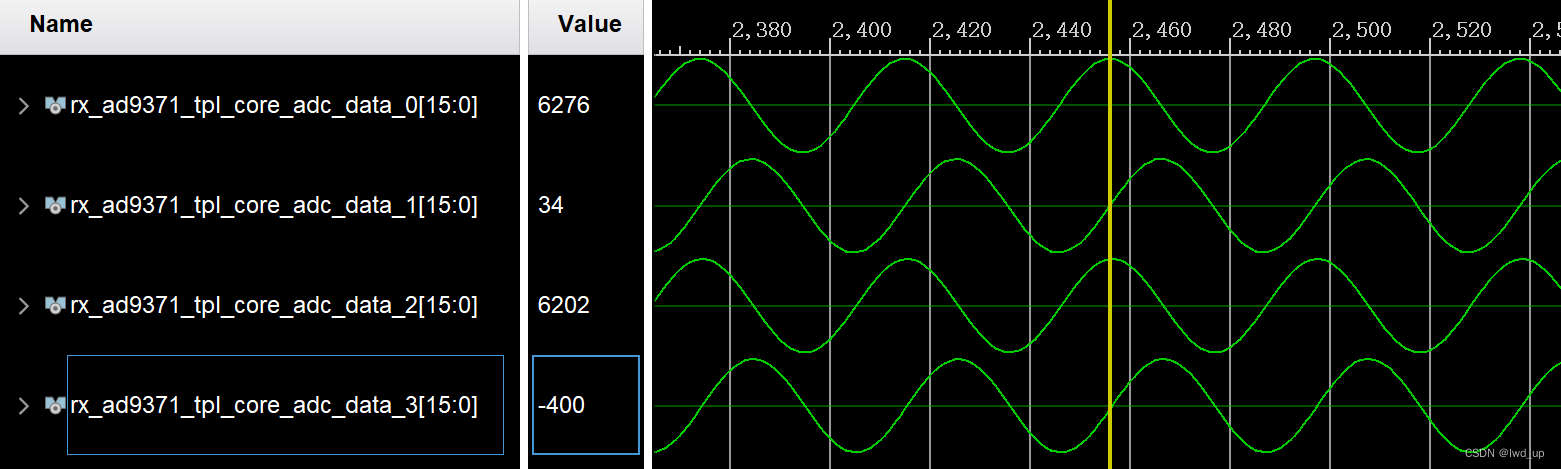

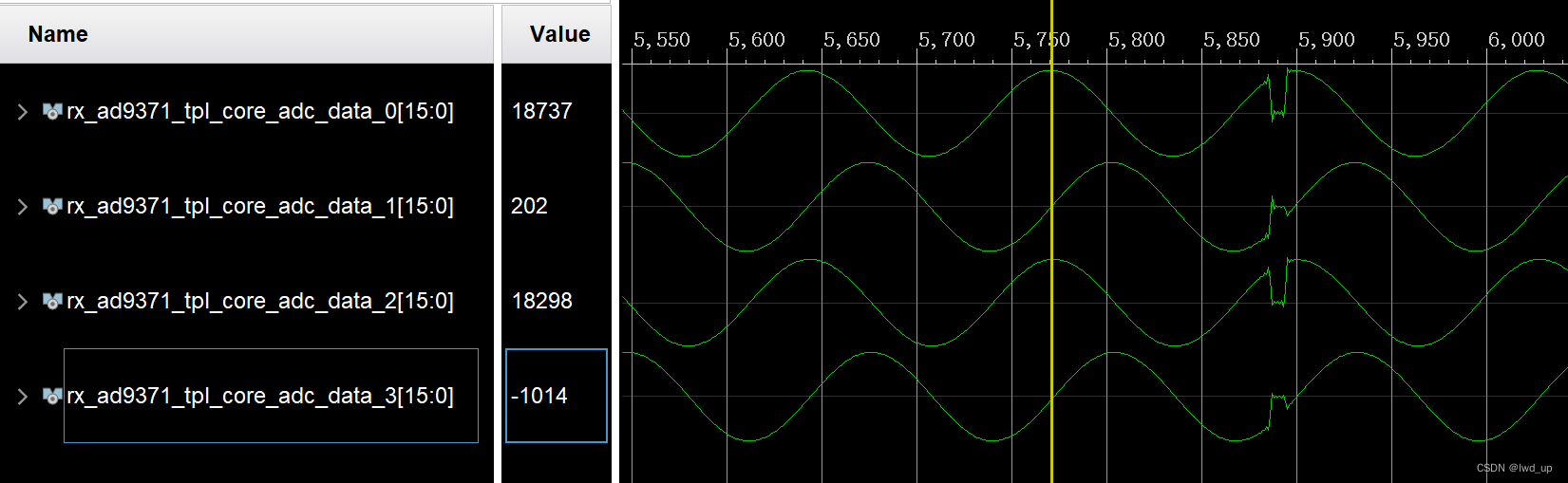

七、测试

TX 端 发送数据如下 ,TX1 和 TX2发送数据相同 (数据来源DMA)

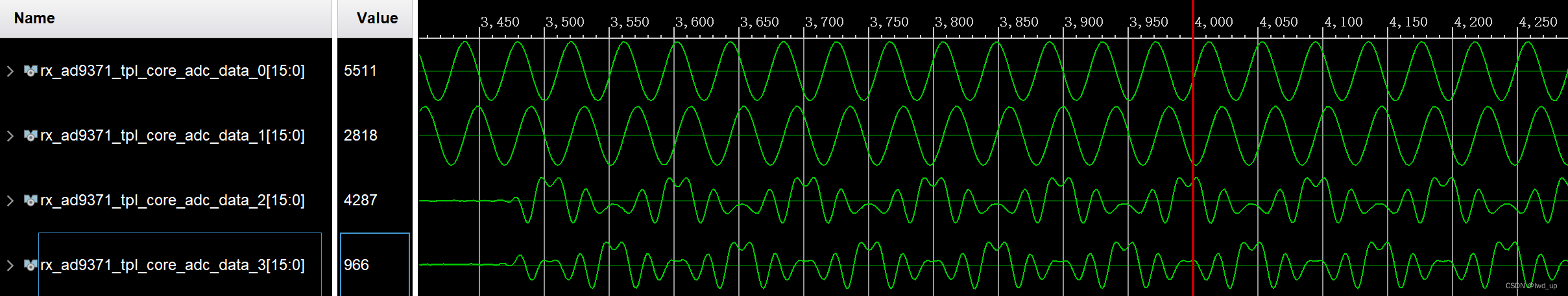

RX 接收的数据如下 (TX选择DDS提供数据)

RX 接收的数据如下 (TX选择DMA提供数据)

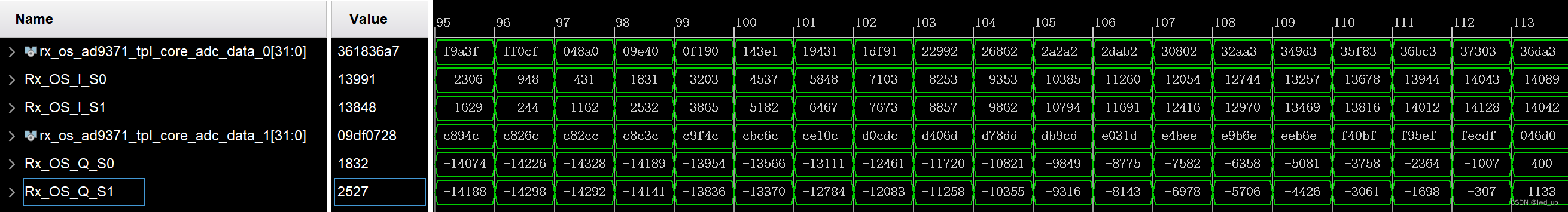

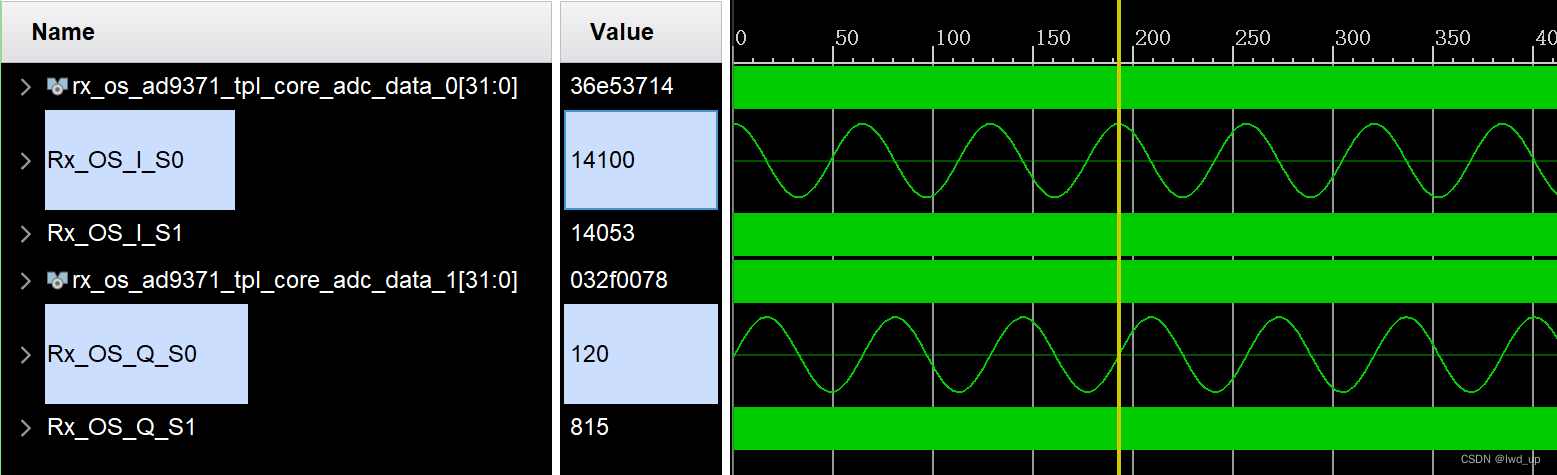

抓取 Rx_OS I 和 Rx_OS Q 信号波形,正如上所述, Rx_OS I S0 在最低 16 位,Rx_OS I S1 次之,Rx_OS Q S1 在最高的16位 。

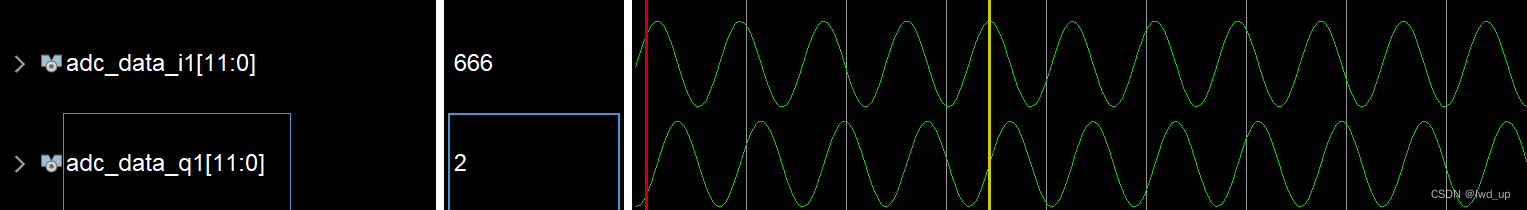

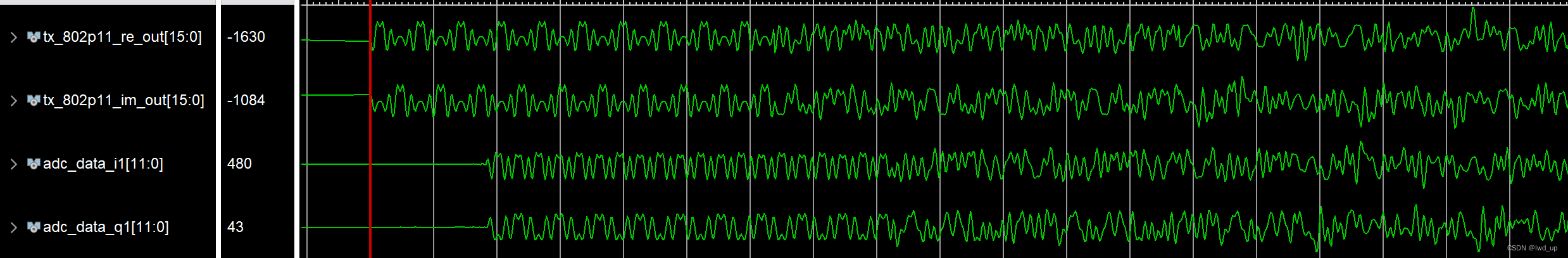

通过使用 AD9361 进一步测试确认 I、Q 数据,AD9371 发送 源自DMA的数据

AD9361 接收信号如下,I 路 COS ,Q 路 SIN ,进一步证实 AD9371 TX 数据格式排布为:

[ Tx2 Q S1,Tx2 Q S0, Tx2 I S1, Tx2 I S0, Tx1 Q S1,Tx1 Q S0, Tx1 I S1, Tx1 I S0 ]

AD9361 发送并接收的基带 I、Q 信号如下

AD9371 的RX_OS接收 AD9361 发送的信号 如下图,进一步证实 AD9371 RX_OS数据格式排布为:

[ Rx_OS Q S1, Rx_OS Q S0,Rx_OS I S1, Rx_OS I S0 ]

AD9371 的 RX2 接收 AD9361 发送的信号 如下图,进一步证实 AD9371 RX 数据格式排布为:

[ Rx2 Q, Rx2 I,Rx1 Q, Rx1 I ]

八、总结

TX 传输层输入 I、Q 排列如下:

[ Tx2 Q S1,Tx2 Q S0, Tx2 I S1, Tx2 I S0, Tx1 Q S1,Tx1 Q S0, Tx1 I S1, Tx1 I S0 ]

RX 传输层输出 I、Q 排列如下:

[ Rx2 Q, Rx2 I,Rx1 Q, Rx1 I]

RX_OS 传输层输出 I、Q 排列如下:

[ Rx_OS Q S1, Rx_OS Q S0,Rx_OS I S1, Rx_OS I S0 ]

,点击停止时会在几秒内缓慢停止,再次点击按钮可以再次旋转,)

)

】linux arm aarch 是 opencv 交叉编译与使用)

![[MySQL] MySQL库的基础操作](http://pic.xiahunao.cn/[MySQL] MySQL库的基础操作)

信息管理系统源码)

,模糊清晰、划痕修复及黑白上色的实践)