1顶层模块:

不能像C语言的h文件那样,把io的定义放在其他文件。

在Verilog中,顶层模块是整个设计的最高层次,它包含了所有其他模块和子模块。

顶层模块定义了整个设计的输入和输出端口,以及各个子模块之间的连接方式。IO的定义通常是放在顶层模块内部,用来定义整个设计的输入和输出端口。

在顶层模块中,我们可以使用 模块IO 来声明下方的空间来定义模块的功能,

通常使用RTL(Register Transfer Level)来实现,也可以编写结构代码或描述性原语。2顶层模块模板:

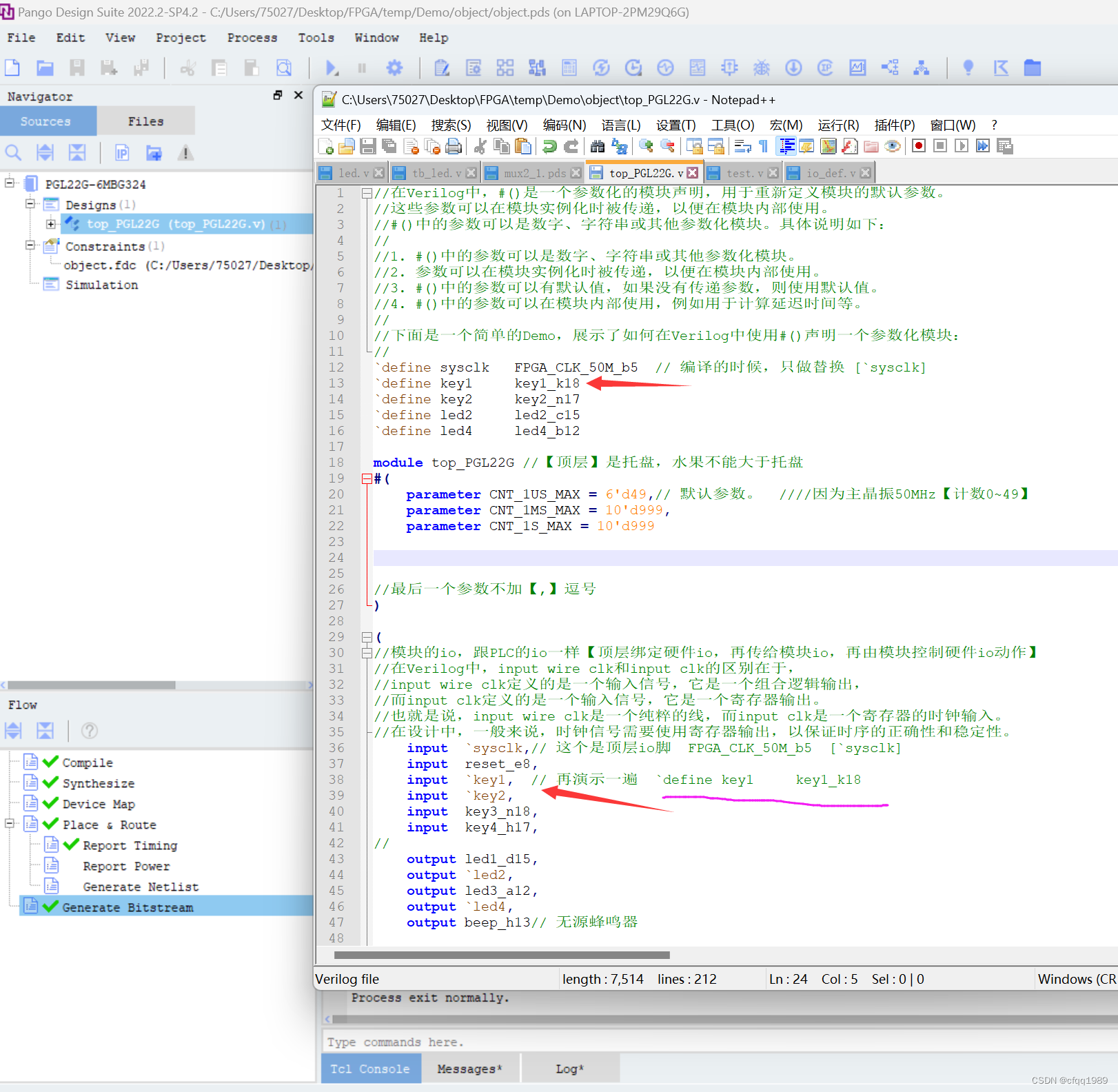

module top_PGL22G

//顶层参数,在加载改模块时,先加载参数

#(parameter CNT_1US_MAX = 6'd49 ,//因为主晶振50MHz【计数0~49】parameter CNT_1MS_MAX = 10'd999 ,// 1ms=1000us;parameter CNT_1S_MAX = 10'd999 //最后一个参数不加【,】逗号

)//模块的io,跟PLC的io一样,程序以集成块的方式展现

(input FPGA_CLK_50M_b5,input reset_e8,input key1_k18,input key2_n17,input key3_n18,input key4_h17,

//output led1_d15,output led2_c15,output led3_a12,output led4_b12,output beep_h13

//【注】最后一个参数不加逗号

);

//===================================

//===内部成员//===================================

//===并联运行的程序//usalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1us <= 6'b0;// cnt_en <= 1'b0;endelse if(cnt_1us == CNT_1US_MAX)// 0~49cnt_1us <= 6'b0;else cnt_1us <= cnt_1us + 6'b1 ;//msalways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1ms <= 10'd0;endelse if((cnt_1ms == CNT_1MS_MAX ) && (cnt_1us == CNT_1US_MAX))// ms满,cnt_1ms <= 10'd0;else if(cnt_1us == CNT_1US_MAX)cnt_1ms <= cnt_1ms + 10'd1 ;// ms加1//salways@(posedge FPGA_CLK_50M_b5 or negedge reset_e8) //【死循环】@敏感【触发条件:上升沿 clk】【运行副本】if(reset_e8==1'b0)begin //50Mhz晶振, 49_999_999 是 1秒1次cnt_1s <= 10'd0;endelse if((cnt_1s == CNT_1S_MAX ) && (cnt_1ms == CNT_1MS_MAX) &&(cnt_1us == CNT_1US_MAX))// s满,cnt_1s <= 10'd0;else if((cnt_1ms == CNT_1MS_MAX)&&(cnt_1us == CNT_1US_MAX))cnt_1s <= cnt_1s + 10'd1 ;// s加1endmodule原来可以,写法上要稍微改下格式

)

数据集)