1.1 基本结构

P1X ECM(Error Control Module)收集从不同的错误源和监控电路发来的错误信号,并通过error pin(ERROROUTZ)对外输出、产生中断并发出ECM reset信号。

P1x-C系列根据产品型号不同,ECM个数也不相同,如下:

对应寄存器基地址如下:

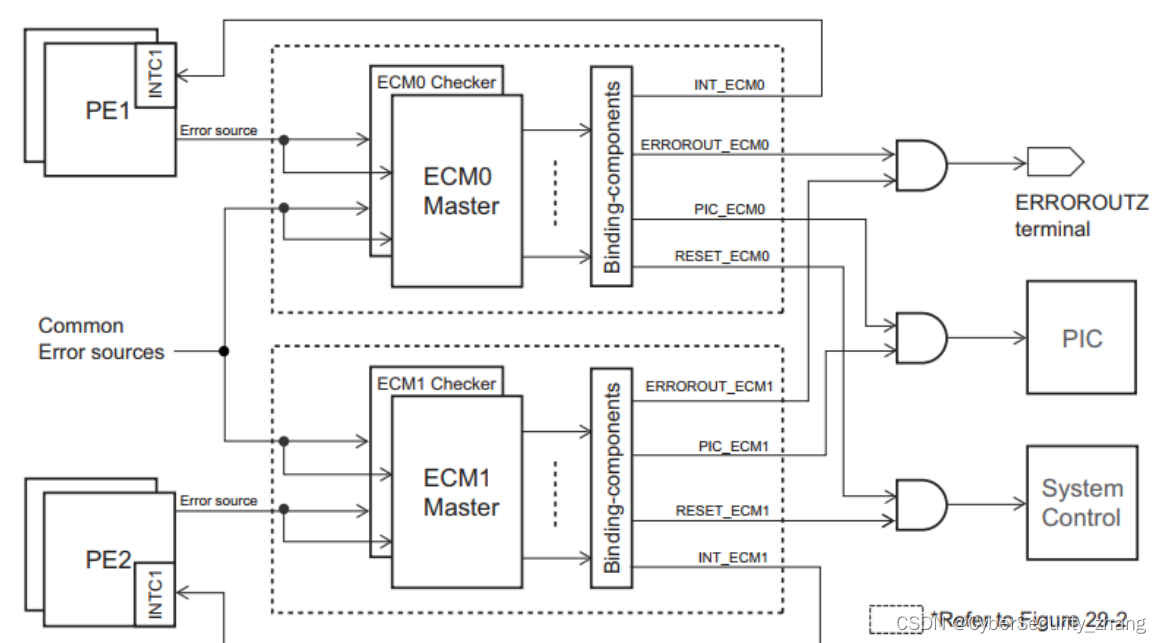

其内部结构框图如下:

两个ECM结构

ECM master和checker结构

1.2 功能总览

1.2.1 功能安全处理方式

- 设置错误Flag

- 生成EI中断

- 生成FE中断

- 触发内部复位:对每个error均可独立控制生成system reset 2

- 通过error pin输出给外部:固定电平/根据计时器输入进行切换

PS:EI\FE等含义

FE level non-maskable interrupt (FENMI)

- 即使已生成另一个FE级别中断FEINT,也将应答FENMI中断。

- 即使CPU系统寄存器PSW.NP = 1,也会应答FENMI中断。

- 无法从FENMI中断返回,也无法恢复

FE level maskable interrupt (FEINT)

- 如果CPU系统寄存器PSW.NP = 0,则可以确认FEINT。如果PSW.NP = 1,则将其屏蔽。

−从FEINT中断返回是可能的,因此恢复也可以。

EI level maskable interrupt (EIINT)

- 如果尚未生成FE级中断(FENMI或FEINT),则可以确认EIINT中断。

- −如果CPU系统寄存器PSW.NP = 0,则可以确认EIINT。

- 如果正在处理PSW.NP = 1,具有更高优先级的EIINT或PSW.ID = 1,则将其屏蔽。

- −可以从EIINT中断返回,恢复也可以。

- −可以为每个中断通道指定中断屏蔽。

- −每个中断通道可以指定16个中断优先级

- −在本节中,对应于中断通道n的EIINT用“ INTn”表示,而EIINT表示对应于中断源xxx,用“ INTxxx”表示。

1.2.2 错误状态记录

ECM集成了错误状态寄存器(3个),可用于从错误标志确认错误状态。

错误flag只能由软件或者POR进行清除,其余复位错误状态不会被清除。

可以看到,这个寄存器是只读的,那么软件可以在什么地方将这些error态清除呢?

用于清除状态寄存器的错误状态。

1.2.3 自诊断/Debug功能

·····通过产生伪错误用于自诊断和调试

伪错误注入时的操作与真实错误发生时的操作相同。掩码到错误引脚输出、中断或错误控制模块复位的所有配置都采用同样的方式。

通过如下寄存器可以输入伪错误

·····ECM内部集成error pin输出的loop-back功能

1.2.4 超时功能

ECM中的delay timer可以在中断请求发生时同时启动;

当delay timer的计数(ECMnDTMR)和比较寄存器(ECMnDTMCMP)中的值匹配时产生该超时错误输出或ECM reset,因为中断处理中该timer没有停止,这个错误flag对应SSE229,正常情况应该是在比较寄存器中配置的时间内完成中断处理。

Ps: SSE229--Error Source Status Reg2 的29bit; 具体对应的Error Source Input为(2*32+29)-1。

与该功能相关的寄存器如下:

ECMnDTMR结构如下:

ECMnDTMCMP结构如下:

1.2.5 Error Output操作

ECM中的Error Output有如下两种模式:

复位之后该pin行为如下:

Hi-Z:高阻态

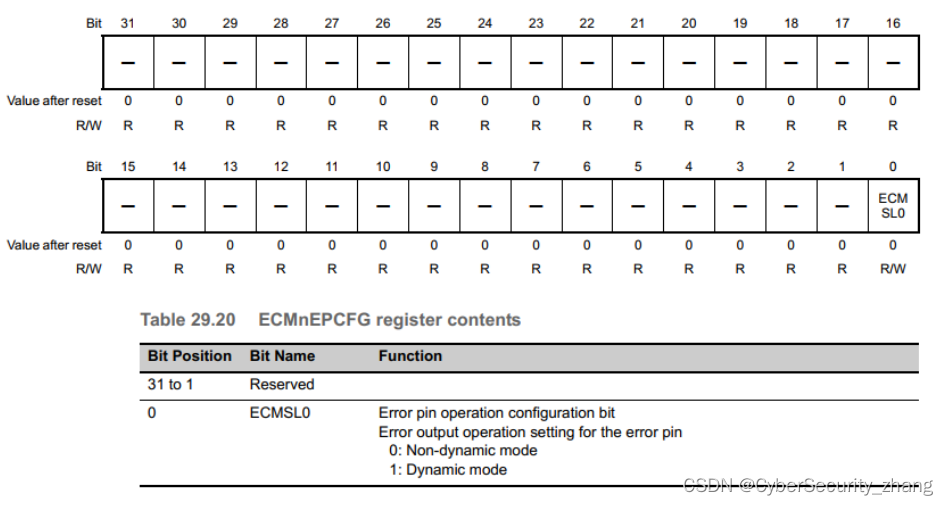

- 动态模式配置

根据timer输入反转电平;使能该模式需要如下步骤:

- 初始化对应Timer GTMAT0O5

- 配置ECMECLR.ECMmECT 位为1,将其设置为高电平,no error状态。

- 配置ECMnEPCFG.ECMSL0位为1,设置为动态模式;

- 启动GTMAT0O5

1.3 与英飞凌对比

| TC3xx | RH850 P1x-C | ||

| 实例个数 | 1(SMU core/stdby) | 1~2(ECM Master/Checker) | |

| Error reaction | Interrupt | Interrupt | |

| NMI | NMI | ||

| CPU Reset | - | ||

| Sys Reset | Sys Reset | ||

| Error Pin Output(FSP协议) | Error Pin Output(低电平/方波) | ||

| 寄存器保护 | SafetyEndinit | Protected Register(有解保护时序要求) | |

| 模块理解难度 | 寄存器配置 | 配置一个Error对应的reaction需要同时设置3个寄存器,理解起来比较困难,但可拓展性强 | 每一个reaction均有独立寄存器配置,配置方法简单 |

| Error Out | FSP协议,较为抽象,但寄存器少,配置方便 | 描述简单,寄存器多,需要深刻理解Delay timer配置的含义 |

)

))

】)