Zynq 7000设备的启动需要正确的电压序列和I/O引脚控制。BootROM的流程由复位类型、启动模式引脚设置以及启动映像来控制。BootROM对所选启动设备的引脚连接有特定的要求。

Zynq 7000 SoC设备具有电源、时钟和复位要求,这些要求必须得到满足,才能成功执行BootROM。

1 电源要求

PS和PL的BootROM电源要求如表6-1所示。

在启动过程中,Zynq 7000的PS(处理系统)和PL(可编程逻辑)部分都需要特定的电源配置。BootROM的启动要求PS和PL的电源都正确配置,以确保系统能够正常启动。此外,对于时钟信号和复位操作也有严格的要求,这些都必须在启动过程中得到满足。

在BootROM执行的早期阶段,BootROM会检查PL是否已上电。如果PL没有上电,BootROM将继续执行。如果PL已上电,BootROM将启动清理周期(清理操作可能包括内存清理、寄存器设置、硬件初始化等,这些步骤对于确保系统的稳定性和可靠性至关重要)。BootROM会等待最多90秒让清理过程完成。如果在这段时间内清理没有完成,那么会发生安全锁定。

如果BootROM需要PL,它会等待最多90秒让PL上电。如果PL在这个时间范围内没有上电,那么系统将关闭,不会提供错误代码。

PL掉电序列包括停止使用PS和PL之间的所有信号、禁用电压电平移位器以及关闭PL的电源。

2 时钟与PLL

PS_CLK参考时钟被路由到设备的多个部分,包括三个PS时钟PLL。PS_CLK的频率会影响设备的启动时间。PLL会将PS_CLK倍频,为各种系统时钟模块生成高频时钟。在需要时,PLL可以被旁路,以便将PS_CLK频率直接传递到系统时钟模块。

如果PLL被启用,那么在启用PLL之前,PS_CLK必须稳定,并且在整个过程中都必须保持稳定。时钟频率必须在数据表指定的操作范围内。

如果PLL被旁路,PS_CLK可以以尽可能慢的速度切换,直至其额定输入频率。这可以用于单步启动过程、用软件控制时钟,或在低时钟频率下操作系统。在低时钟频率下操作系统可能会排除使用设备中的一些模块(例如,USB ULPI时钟的频率必须低于CPU_1x时钟)。

注意:在BootROM执行期间,所有速度等级规格的最大频率为500 MHz。

3 复位操作

3.1 系统复位

有两种类型的系统复位:POR和非POR。

POR复位会重置整个系统,包括所有寄存器。除了eFuse和BBRAM之外,所有状态都会丢失。

非POR复位会被记录在slcr.REBOOT_STATUS寄存器中。非POR复位也会导致BootROM执行,但BootROM会保留关于前一个启动的安全级别的知识,存储在devcfg.CTRL [SEC_EN]位中。

非POR复位的来源包括PS_SRST_B引脚和内部系统复位。

3.2 外部复位信号引脚

有两个外部复位引脚,PS_POR_B和PS_SRST_B:

PS_POR_B

唯一用于采样引导模式引脚捆绑电阻的复位。对于上电序列,PS_POR_B输入必须保持低电平,直到VCCPINT、VCCPAUX和VCCO_MIO0达到其最小工作电平,以确保PS eFUSE的完整性。

对于掉电序列,在VCCPINT达到0.80V之前,必须满足以下四个条件中的至少一个(条件必须保持为真,直到VCCPINT降至0.40V,以确保PS eFUSE的完整性):

①PS_POR_B输入被置为低电平,

②PS_CLK输入的参考时钟被禁用,

③VCCPAUX低于0.70V,

④VCCO_MIO0低于0.90V。

在最后一个PL电源开始上升时,PS_POR_B不得取消断言。在此窗口期间断言PS_POR_B可能导致锁定事件。

PS_SRST_B

用于强制系统复位。它可以被绑定或拉高,并且在PS电源上升期间可以保持高电平。PS_SRST_B复位是非POR复位。

在BootROM从POR复位执行时,不得断言PS_SRST_B信号,否则会发生锁定事件,阻止BootROM完成系统启动过程。要从这种类型的锁定中恢复,必须断言PS_POR_B复位。Boot ROM完成执行并移交给FSBL/用户应用程序所需的时间取决于多个因素。有关如何确定特定用户配置的启动时间的详细信息,请参阅“启动时间参考”。

3.3复位信号时序

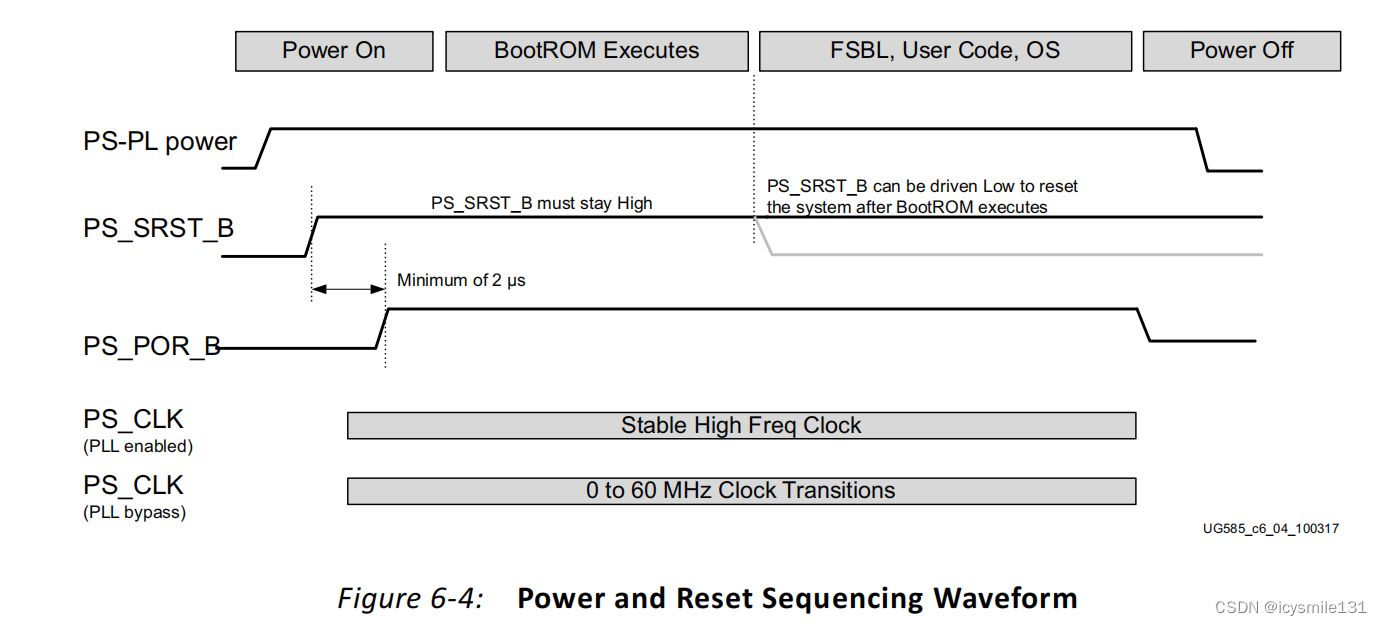

启动设备所需的复位时序如图6-4所示。如果在BootROM执行期间断言PS_SRST_B,则会发生系统锁定,而不会生成错误代码。

3.4 内部复位

内部复位都是非POR复位。包括

• 软件控制复位:向slcr.PSS_RST_CTRL [SOFT_RST]写入1。

• 看门狗定时器:AWDT0、AWDT1和SWDT控制器。

• JTAG接口和调试。

4 引导模式引脚设置

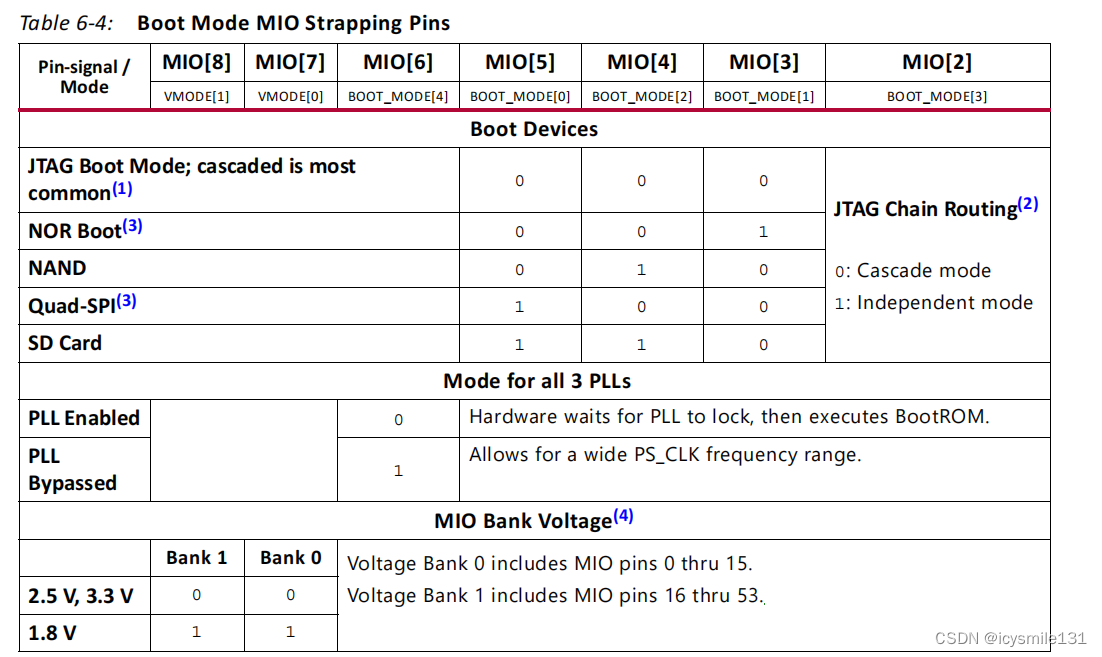

有7个引导模式捆绑引脚,它们使用MIO引脚[8:2]在板上进行硬件编程。这些引脚在PS_POR_B去断言后不久由硬件采样,并将它们的值写入软件可读寄存器以供BootROM和用户软件使用。

板上的硬件必须将每个捆绑引脚MIO[8:2]连接到20kΩ的上拉或下拉电阻。模式引脚的编码如表6-4所示。上拉电阻表示逻辑1,下拉电阻表示逻辑0。

五个引脚BOOT_MODE[4:0]用于选择引导模式、JTAG链配置以及是否旁路PLL。这些引脚采样的值被写入slcr.BOOT_MODE的[BOOT_MODE]和[PLL_BYPASS]位字段。

另外两个引脚VMODE[1:0]用于选择两个MIO电压组的电压信号电平。这些引脚采样的值被写入slcr.GPIOB_DRVR_BIAS_CTRL的[RB_VCFG]和[LB_VCFG]位字段。VMODE设置由BootROM用于最初设置MIO_PIN_{53:00}寄存器以选择所选的I/O信号标准。VMODE[0]控制MIO引脚15:0,而VMODE[1]控制MIO引脚53:16。上拉使BootROM选择LVCMOS18。下拉选择LVCMOS33,它与LVCMOS25兼容。

FSBL/用户代码可以更改JTAG链、PLL和MIO引脚的I/O电压标准的初始引导模式设置,这些设置基于单个MIO引脚。

5 启动设备的I/O引脚连接

有些引脚连接是所有启动模式都必需的,而其他连接则取决于启动模式引脚捆绑和BootROM Header信息。在BootROM执行完毕后,用户代码可以根据需要重新配置I/O引脚连接。

对于所有启动配置,以下连接是必要的:

①PS电源供应

②PS_POR_B、PS_SRST_B和PS_CLK_B

对于特定的启动设备,MIO连接如下:

①Quad-SPI(自动检测1、2、4或8位接口)

②SD存储卡(SDIO 0,MIO引脚40-47)

③NAND(自动检测8或16位接口)

④NOR(CS 0)

⑤JTAG(PLJTAG接口),通常用于级联模式

这些连接确保了启动设备与处理器之间的正确通信和数据传输。例如,Quad-SPI接口用于高速读写和擦除数据,而SD存储卡接口则用于与SD卡进行数据交换。NAND和NOR接口分别用于连接不同类型的闪存芯片。JTAG接口则用于调试和编程。

在设计和配置这些连接时,需要仔细考虑引脚的功能和特性,以确保系统的稳定性和性能。同时,也需要注意不同启动模式可能需要不同的引脚连接配置,因此在实际应用中需要根据具体需求进行选择和调整。

)

(C++实现))

之小部件(二):如何使用滑动条部件)

)

)

)