9月14日,Arm发布了新的处理器内核:V2和E2,在官网已经可以看到相关的TRM 手册了。。

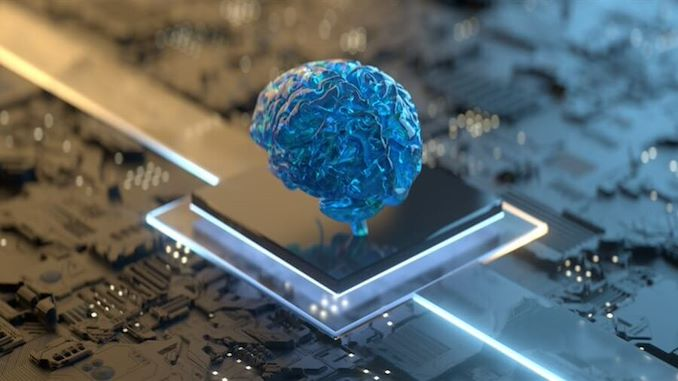

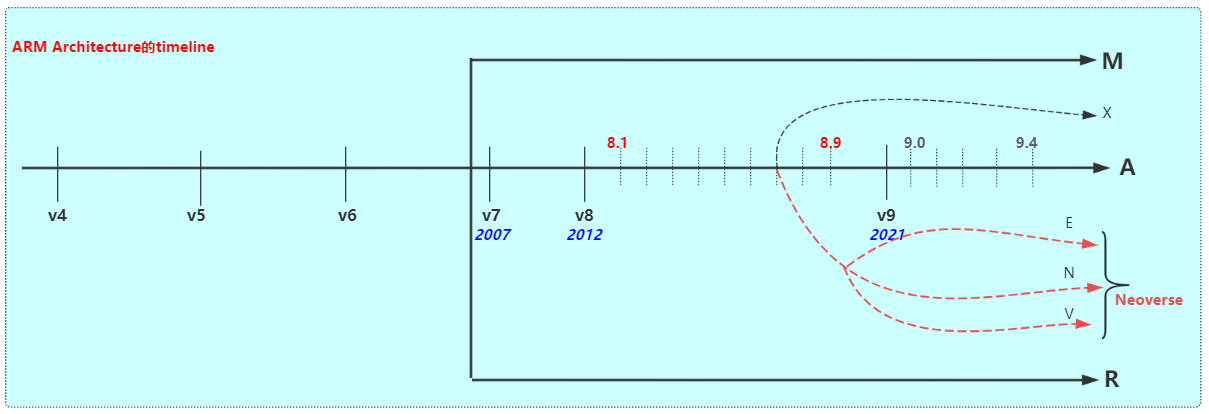

四年前,Arm发布了Neoverse系列的CPU设计。Arm决定加大力度进军服务器和边缘计算市场,专门为这些市场设计Arm CPU内核,而不仅仅是回收以消费者为中心的Cortex-A设计。因此,Arm开始以更积极的方式进军基础设施市场。这些努力为Arm及其合作伙伴带来了越来越丰厚的回报,得益于亚马逊的Graviton和Ampere Altra CPU等产品,他们终于能够在服务器CPU市场中占据重要份额。

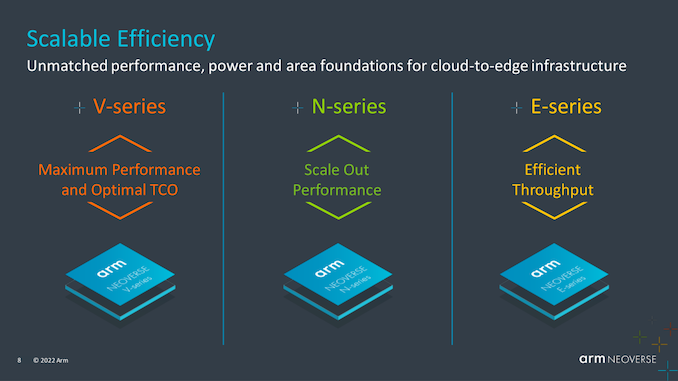

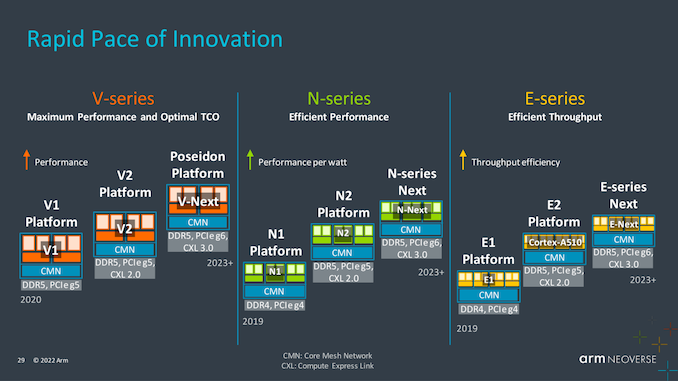

然而,随着Arm CPU最终实现了过去十年未能实现的市场渗透率,Arm需要确保不会满足于现状。在该公司的Neoverse核心设计的三个系列中——高效的E、灵活的N和高性能的V——该公司已经推出了第二代N核心,恰当地称为N2。现在,该公司正准备用下一代V和E核心更新Neoverse系列的其余产品,并于今天发布了Neoverse V2和Neoverse E2核心。这两种设计都将为HPC和其他服务器客户带来Armv9架构,并显着提高性能。

Arm Neoverse V2:Armv9助力高性能计算

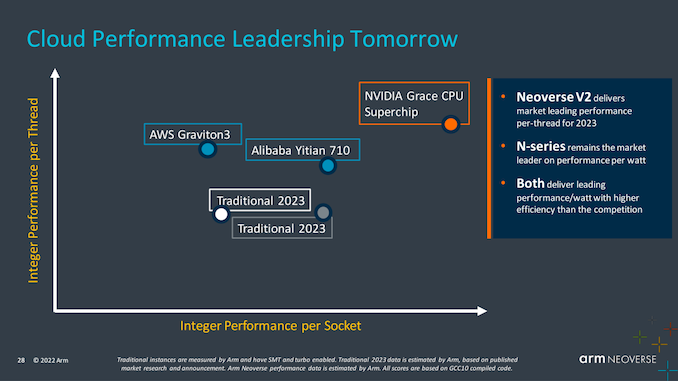

领导Arm新CPU核心IP的是该公司的第二代V系列设计Neoverse V2。完整的V2平台代号为Demeter,标志着Arm高性能V系列内核的首次迭代,以及该内核系列从Armv8.4 ISA到Armv9的过渡。虽然这只是Arm第二次尝试服务器专用高性能核心,但请不要误会:Arm的目标是雄心勃勃。该公司声称Neoverse V2 CPU将提供市场上最高的单线程整数性能,超越AMD和英特尔的下一代设计。

虽然Arm本周发布的公告没有对新架构进行全面深入探讨,而且更令人恼火的是,该公司没有谈论具体的PPA指标,但Arm提供了对一些变化和功能的高级概述,这些功能将随V2平台一起提供。可以肯定的是,V2 IP现已完成并交付给客户(尤其是NVIDIA),但在2023年第一批基于该IP的芯片发布之前,Arm在某种程度上对V2的说法含糊其辞。

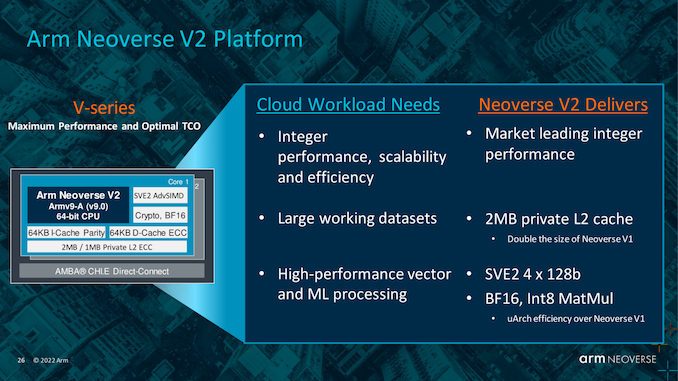

首先也是最重要的,Armv9的升级带来了最新Arm架构的全套功能。其中包括作为架构基础功能的安全性改进(对于云共享环境尤其方便)以及Arm较新的SVE2矢量扩展。

对于后者,Arm做出了一个有趣的改变,重新配置了矢量引擎的宽度;V1使用2个管道256位SIMD实现SVE(1),而V2则转向4个管道128位SIMD。最终结果是V2的累积SIMD宽度并不比V1宽,但执行流程已更改为并行处理大量较小的向量。这一变化使得SIMD管道宽度与Arm的Cortex部件相同(均为128位,SVE2的最小尺寸),但这确实意味着Arm不再充分利用可扩展性通过使用更大的SIMD来实现SVE的一部分。我希望一旦Arm进行了全面的V2深入研究,我们就会明白为什么Arm会采取这条路线,因为我很好奇这是否纯粹是一种效率游戏,还是更类似于整个Arm生态系统的同质化设计。

除此之外,值得注意的是,虽然Arm的演示幻灯片将bfloat16和int8 matmul列为功能,但这些并不是新功能。尽管如此,Arm仍承诺V2的SIMD处理将比V1提供更高的微架构效率。

更广泛地说,V2还将引入更大的L2缓存大小。V2设计支持每个核心高达2MB的私有二级缓存,是V1最大大小的两倍。V2还将进一步改进Arm的整数处理性能,但该公司目前尚未透露更多细节。从架构的角度来看,V1借鉴了Cortex-X1 CPU的设计,如果V2再次借鉴X2的设计,也不会太令人惊讶。在这种情况下,像Snapdragon 8 Gen1和Dimensity 9000这样的消费芯片应该可以提供一个关于预期结果的宽松参考。

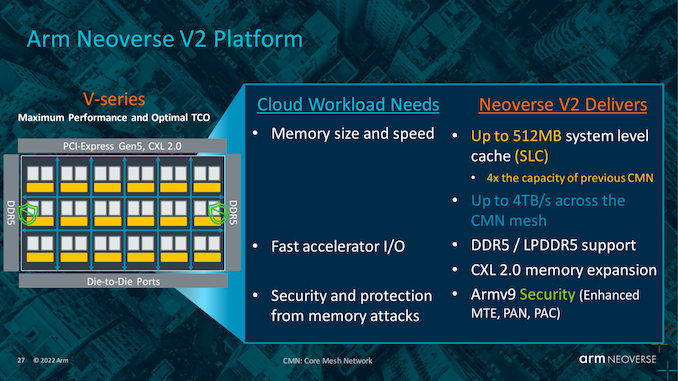

对于Demeter平台,Arm将重复使用其CMN-700网状织物,该织物首次在V1代中引入。CMN-700仍然采用现代网格设计,在12x12配置中支持多达144个节点,并且适合与DDR5内存以及用于I/O的PCIe 5/CXL 2连接。因此,严格来说,V2并没有在结构层面带来任何新东西——甚至512MB的SLC也可以通过V1 + CMN-700设置完成——但这确实意味着CMN-700网格及其功能现在是V2前进的基线。

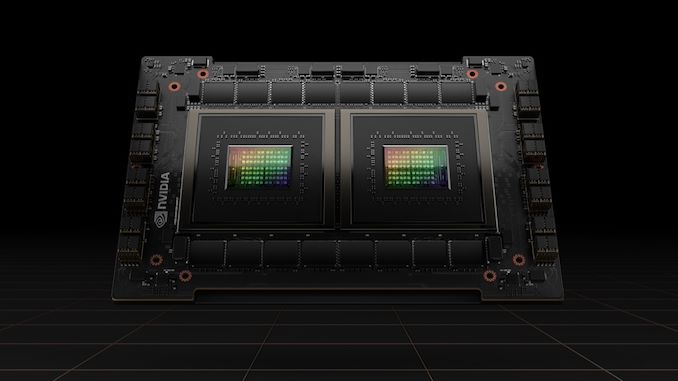

Neoverse V2核心将成为下一代高性能Arm服务器CPU的基石。这里事实上的旗舰产品将是NVIDIA的Grace CPU,它将是2023年推出的首批(如果不是第一个)V2设计之一。NVIDIA此前曾宣布Grace将基于Neoverse设计,因此本周的公告Arm最终证实了长期以来的怀疑,即Grace将基于下一代Neoverse V核心。

NVIDIA则计划在几天内举办秋季GTC活动。因此,随着NVIDIA寻求在明年发布之前推广该芯片,我们很可能会听到更多有关Grace及其Neoverse V2基础的信息。

Neoverse E2:Cortex-A510与N2配合使用

除了Neoverse V2的发布之外,Arm还利用本周的简报发布了Neoverse E2平台。与V2的发布不同,这是一次规模小得多的公告,Arm仅提供了少量技术细节。最终,E2的辉煌日子将在晚些时候到来。

也就是说,E2平台正在交付给合作伙伴,着眼于与现有N2平台的互操作性。为此,Arm将Cortex-A510 CPU(Arm的小型/高效Cortex CPU内核)与CMN-700网格配对。此举旨在通过提供N2的替代CPU核心,为服务器运营商/供应商提供更大的灵活性,同时仍提供Arm网格的现代I/O和内存功能。强调这一点的是,E2系统背板甚至与N2背板兼容。

Neoverse Next: Poseidon, N-Next, and E-Next

最后,Arm本周发布的公告让我们可以一睹该公司所有三个Neoverse平台的未来路线图,不出所料,Arm正在开发每个平台的更新版本。

值得注意的是,所有三个平台都要求添加PCIe 6支持和CXL 3.0支持。这将来自Arm的CMN网状网络的下一个迭代,正如Arm今天所做的那样,该网络在所有三个平台之间共享。

与此同时,有趣的是看到Poseidon的名字再次出现在Arm的路线图中。回到Arm的第一个Neoverse路线图,Poseidon是Arm的500万/2021平台的名称,此后该位置被N2和V1/V2以各种形式占据。由于V2直到2023年才会登陆硬件,Poseidon/V3还需要数年时间,但Arm保留代号可能有一定意义(例如新的微架构)。

但首先推出的将是N-Next平台——可能是Neoverse N3。Neoverse N平台领先其他平台一代(N2于2020年首次发布),它将成为下一个需要更新的平台。N3将于2023年向合作伙伴推出,Arm广泛宣传新一代性能和效率改进。

CocosCreator UI组件(二))

![[npm]脚手架本地全局安装1](http://pic.xiahunao.cn/[npm]脚手架本地全局安装1)

)