单周期定时循环详解

单周期定时环路是FPGA编程中最强大的结构之一。单周期定时循环中的代码更加优化,在FPGA上占用更少的空间,并且比标准While循环中的相同代码执行得更快。单周期定时环路将使能链从环路中移除,以节省FPGA上的空间。由于删除了额外的使能链寄存器,因此单周期定时环路中的所有操作都可以在单个时钟周期内完成。此外,消除使能链开销减少了FPGA上使用的总空间,因为不再需要用于使能链的触发器。单周期定时环路是安全关键和控制应用的重要工具,其中快速环路速率很重要

LabVIEW自动优化单周期定时循环(SCTL)内的代码。与While循环内的相同代码相比,SCTL内的代码执行更快,占用FPGA终端资源更少。在FPGA终端上使用While循环时,While循环每执行一次需要占用多个时钟周期,While循环包含启用链寄存器。While循环每次执行需要占用的时钟周期的数量取决于循环内的代码。在FPGA终端上使用单周期定时循环时,单周期定时循环将在一个时钟周期内执行完循环内的所有代码。在FPGA目标上使用单周期定时循环减少了执行周期和资源占用,因为单周期定时循环不包括启用链寄存器。如果单周期定时循环包含已初始化的移位寄存器,循环第一次执行前占用一个时钟周期,以初始化移位寄存器的值。单周期定时循环类似于HDL中的定时进程。

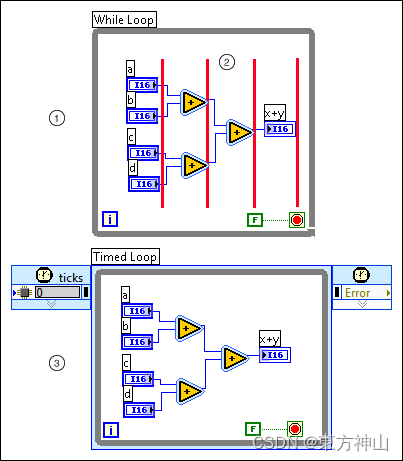

下列图示展示了执行相同代码的While循环和单周期定时循环之间的区别。

下面列出了上述程序框图的要点。

|

| 执行While循环内的代码需要四个时钟周期,不包括While循环占用的两个时间周期作为额外开销时间。 |

|

| 红色垂直线表示每个时钟周期内While循环执行的结束位置。 |

|

| 如时钟周期对于代码而言足够长,同样的代码放在单周期定时循环内,可以在一个时钟周期内执行完毕。 |

您也可使用单周期定时循环减少FPGA VI中的执行周期,以优化代码。如下图所示。

如上图所示,如果在While循环中使用单周期定时循环,则将TRUE常量连接到条件接线端,使得定时循环内的代码在While循环的每个周期执行一次。

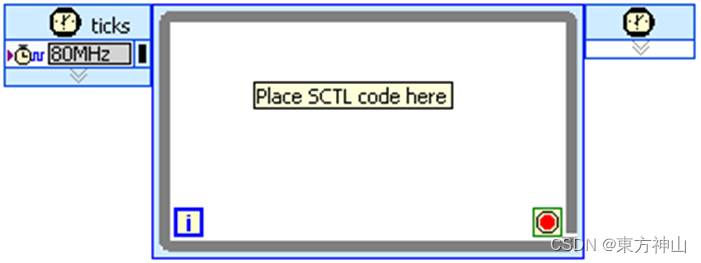

下图显示了使用 SCTL 在一个时钟周期内执行一些数据处理的示例。 While 循环中的相同操作需要大约 7 个时钟周期,包括 While 循环的开销。

FPGA模块单周期定时环路与标准LabVIEW定时环路的不同之处在于FPGA定时环路的时序与您指定的FPGA时钟的时钟速率完全对应。通过配置单周期定时环路使用FPGA目标基时钟以外的时钟,可以在FPGA VI中实现多个时钟域。您可以通过在单周期定时环路的输入节点(input Node)的输入源名称(Source Name)上连接一个值或在“配置定时环路”对话框中指定控制单周期定时环路的FPGA时钟。

运行在基于windows或实时目标上的VI中的定时循环将在指定的周期内依次执行一个或多个子图或帧。相比之下,FPGA VI中的单周期定时环路在与FPGA时钟相同的周期内执行一个子图。当您希望开发具有多速率计时功能、精确计时、循环执行反馈、动态变化的计时特性或多个执行优先级级别的VIs时,请使用单周期Timed Loop。右键单击结构边框以添加、删除、插入和合并框架。

FPGA时钟

基本时钟

是硬件中存在的数字信号,可以用作FPGA应用程序的时钟。

FPGA目标可以支持多个基本时钟,尽管一些目标在添加目标时只向Project Explorer窗口添加受支持的基本时钟的子集。如果您使用的FPGA目标在将目标添加到LabVIEW项目时不包括项目浏览器窗口中所需的FPGA基本时钟,则可以向LabVIEW项目添加新的基本时钟。

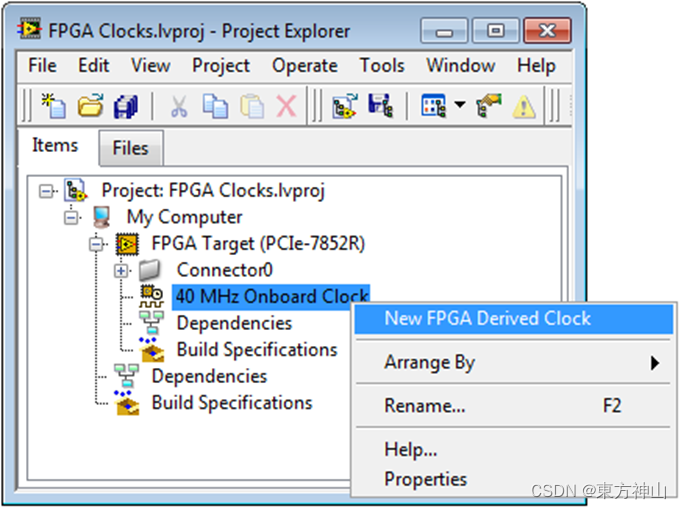

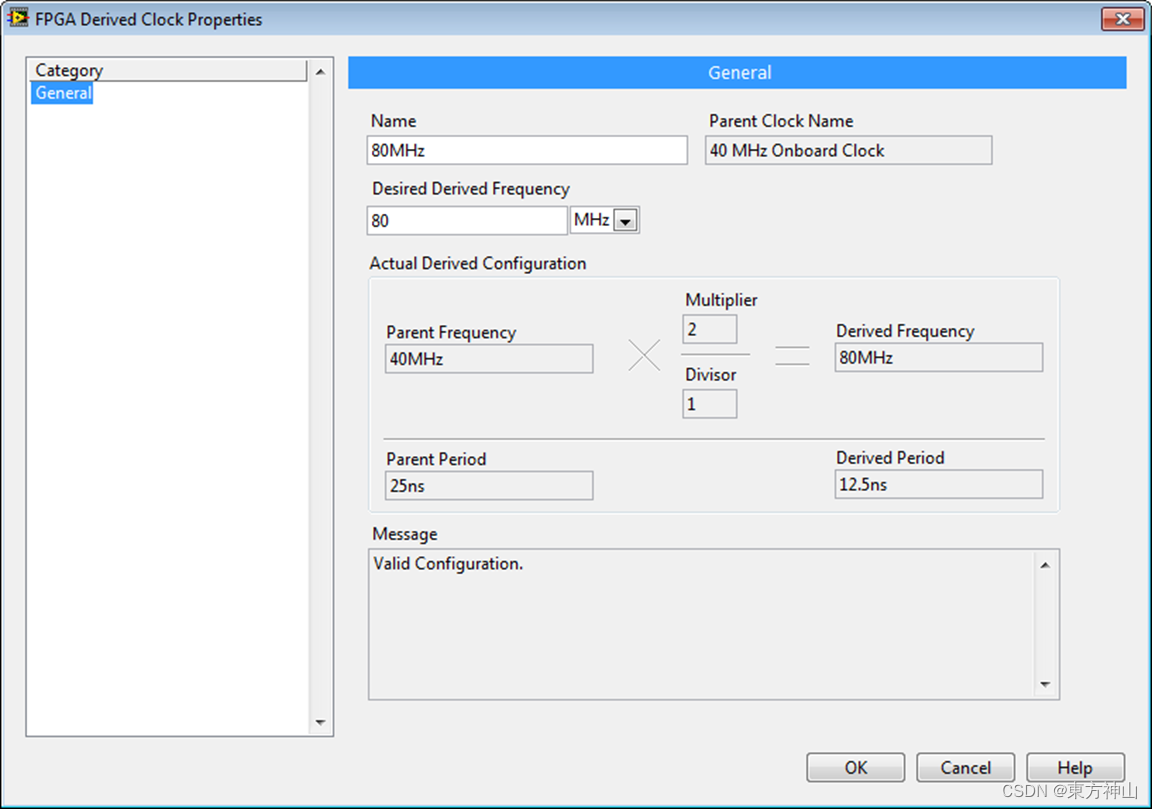

衍生时钟

是您从基本时钟创建的时钟,您可以将其用作FPGA应用程序的时钟。您可以在LabVIEW项目中从FPGA基本时钟派生额外的时钟。

如果FPGA目标不支持FPGA派生时钟或您添加的FPGA基本时钟,则快捷菜单中的新FPGA派生时钟选项将变暗。

顶层时钟

您可以在Project Explorer窗口中为FPGA目标定义顶级时钟。顶层时钟是FPGA VI在单周期定时循环之外使用的时钟。FPGA目标默认使用FPGA基时钟之一。如果FPGA目标允许,可以配置FPGA基时钟,并将其设置为项目中的顶级时钟,以控制执行速率。如果FPGA目标不允许您以您想要的方式配置FPGA基本时钟,则可以使用派生时钟。对FPGA派生时钟的支持因FPGA目标而异。有关更多信息,请参阅特定的FPGA目标硬件文档。

单周期Timed Loop内的代码以基本时钟或派生时钟速率执行,具体取决于使用哪个时钟作为源。顶层时钟控制单周期定时循环之外代码的执行速率。

每个FPGA目标提供至少一个时钟来控制FPGA的内部操作。FPGA目标时钟确定FPGA VI框图上单个VI和功能的执行时间。您可以编译具有更快时钟速率的FPGA vi,以获得更高的性能。

然而,并不是所有的FPGA VIs都可以在更快的时钟速率下正常编译。如果您选择的时钟速率对于FPGA VI来说太快了,编译状态窗口会通知您编译失败。您必须选择较低的时钟频率,然后再次尝试编译。

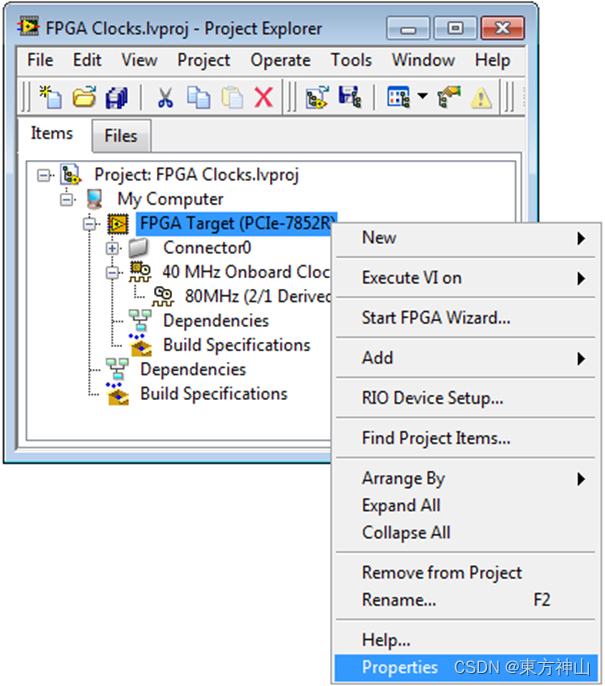

在“项目资源管理器”窗口中右键单击FPGA目标,在弹出的快捷菜单中选择“属性”,可以更改FPGA目标的顶层FPGA目标时钟速率。在“FPGA Target属性”对话框的“顶层时钟”页面中,可以设置顶层时钟。您还可以通过双击输入节点并在配置定时环路对话框中选择时钟速率来更改FPGA VI内单周期定时环路的时钟速率。

您可以选择FPGA目标顶级时钟或从FPGA目标基本时钟派生的时钟。

如果在FPGAVI中更改顶层FPGA目标时钟速率或单周期定时环路时钟速率,则必须重新编译FPGAVI

单周期定时循环FAQ:

什么是单周期定时循环?

(SCTL)是LabVIEW定时循环结构的一种特殊用途。在FPGA VI中使用时,定时循环结构始终是SCTL。当与FPGA终端一起使用时,此循环将在您选择的FPGA时钟的一个时钟滴答内执行所有函数。默认时钟是40 MHz的 FPGA全局时钟。您可以将SCTL与派生时钟一起使用,以40 MHz以外的速率为循环提供时钟。在与FPGA终端一起使用时,无法动态更改定时循环的时序属性。

程序使用SCTL执行的速度有多快?

在FPGA VI中使用传统的While循环至少需要3个滴答才能执行每次迭代。这是因为在编译的FPGA VI中使用了启用链。对启用链的解释超出了本文档的范围,其用于确保将FPGA VI编译为位文件时的数据流进行传递。

此外,尽管如果没有数据依赖性,函数并行执行,While循环内的每个函数都需要至少执行一个tick。使用SCTL,循环内的所有函数必须在单个时钟滴答内执行。

在FPGA VI中使用SCTL的性能优势将根据循环中的内容而有所不同。如果您的代码可以在SCTL中成功编译而不是正常循环,您代码的运行性能显着提高。

SCTL 是否更有效利用 FPGA 资源?

是。由于您的逻辑是在硬件中组合实现的,因此代码生成的FPGA配置使用的资源更少。 SCTL不会进行添加、保存结果,然后相乘、保存结果,而是在一个时钟滴答中完成,而不必在两者之间保存结果。这节省了FPGA资源,因为在操作之间不需要触发器来保存每个先前操作的结果。

在SCTL内部可以使用所有函数和结构吗?

否。超过一个时钟滴答的函数,例如模拟I / O函数或任何等待的函数都无法在SCTL内部使用。此外,如果循环内部有一个逻辑链,执行时间超过一个时钟滴答,则该逻辑不能在SCTL内部使用,并且VI将无法编译。

序列结构可以放在SCTL中,但在FPGA上执行之前将从代码中删除。

有一个不能在SCTL中使用的功能列表。有关各个VI的SCTL支持和定时信息的更多信息,请参见LabVIEW帮助。

- 模拟周期测量VI

- 巴特沃斯滤波器VI

- 离散延迟VI

- 导数函数

- FIFO清除函数

- FPGA I / O方法节点,除了一些FPGA目标

- FPGA I / O属性节点,除了一些FPGA目标

- 中断VI

- 1维查找表 VI,选中Interpolate data复选框

- 循环定时器VI

- 如果至少一个节点在循环内同时至少一个节点在循环外部,则为同一I / O资源配置多个FPGA I / O节点

- 如果您使用多个实例,则不可重入的子VI

- 陷波滤波器VI

- PID VI

- 商和余数

- 自反函数

- 1D数组转置函数

- 正弦波发生器VI

- 单精度浮点运算

- 平方根函数

- 定时循环

- 等待Express VI

- 等待发生函数

- while循环

我可以使用流水线技术在SCTL内部执行更多逻辑吗?

是。您可以使用移位寄存器或反馈节点来实现逻辑并行执行,并在SCTL的连续迭代之间传递数据;因此,整个逻辑链在多个SCTL迭代上执行。与FPGA VI中的任何并行实现一样,这使用额外的FPGA资源。

如果SCTL中的逻辑无法在一个滴答中执行,会报错吗?

是的,虽然在尝试编译FPGA VI之前,LabVIEW通常不会报告与时序相关的错误。编译中有两个不同的点,您可能会遇到与SCTL相关的错误。首先,当LabVIEW FPGA尝试将VI编译为VHDL代码(生成中间文件)时,如果在SCTL中使用了任何不受支持的函数(例如,商和余数),则会收到错误对话框。此框出现只需几秒钟(完整的VHDL编译过程不会开始)。

即使您在SCTL中避免使用不受支持的函数,如果SCTL包含足够的逻辑,使得循环仍无法在单个时钟周期内执行,则编译将因定时违规而失败。在Xilinx工具的实际编译期间会发生此类错误,并且可能会在编译中停留几分钟(或更长时间)。如果遇到这样的错误,请尝试减少SCTL中的逻辑或修改算法以允许VI成功编译。

SCTL是一项高级功能吗?

是。虽然某些任务可以在SCTL中非常简单地实现,但有些任务可能比较困难。例如,如果使用SCTL,则无法使用等待函数来实现高速数字协议。您必须使用状态机,以便循环的每次迭代只需要一次滴答。 SCTL为需要它的应用程序提供了速度和效率,但使用起来可能很棘手。在某些情况下,使用传统的While循环可能更合适。

我可以使用更快的全局时钟SCTL吗?

是的,但是在80 MHz或更高频率下编译的SCTL中可以执行的功能更少。

SCTL可以嵌套While循环吗?

单周期定时循环不能嵌套在其他单周期定时循环中。删除嵌套循环或将顶层循环替换为普通的 While 循环。

什么是组合路径错误?

组合路径是 FPGA 上一个寄存器的输出与另一个寄存器的输入之间的逻辑路径。 寄存器将数据存储在FPGA上并在时钟的上升沿更新数据。 长组合路径需要更多时间来执行并限制时钟域的最大时钟速率。

长组合路径通常是单周期定时循环中的一个问题,因为输入寄存器和输出寄存器之间的逻辑必须在您指定的时钟速率的一个周期内执行。 在单周期定时循环中,组件内部和组件之间的寄存器被移除,从而增加了寄存器之间的组合路径的长度。 如果组合路径中的代码未在一个时钟周期内执行,LabVIEW将在编译失败对话框中返回时序违规。

注意 深度嵌套的 Case 结构也会导致 LabVIEW 在编译失败对话框中返回时序违规。

要减少组合路径的长度,首先要尽可能简化逻辑。 将逻辑简化为最简单的形式后,您可以通过将逻辑划分为离散步骤并对设计进行流水线化来进一步缩短组合路径的长度。

)

)

)

)

)