Xilinx FPGA模式配置

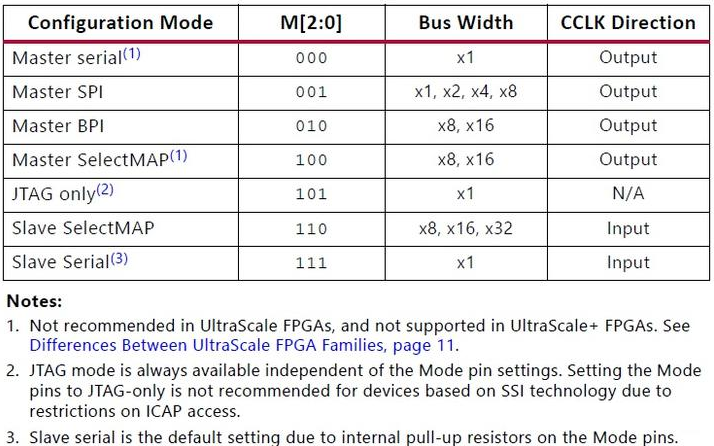

Xilinx UltraScale FPGA有7种配置模式,由模式输入引脚M[2:0]决定。七种模式如图1所示。

图1 7种配置模式

7种模式可分为3大类,

1、JTAG模式(可归为从模式);

2、主模式;

3、从模式。

- 主模式分为Master Serial模式、Master Parallel模式;

- 从模式分为Slave Serial模式、Slave Parallel模式。

主模式:

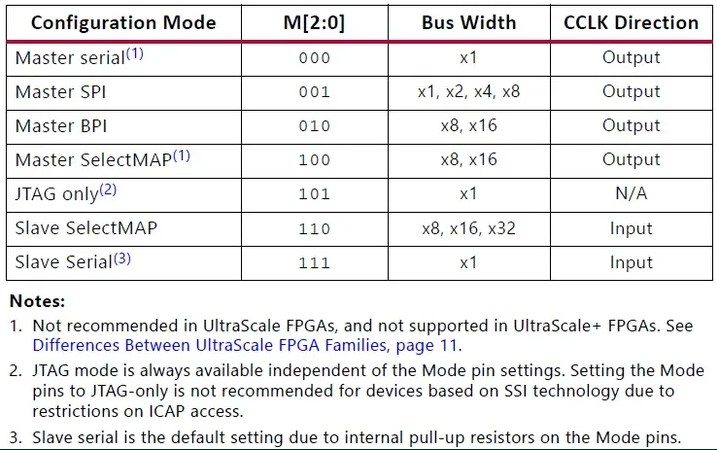

自加载FPGA配置模式,通常称为主模式,可用于串行或并行数据传输路径。在主模式下,FPGA的配置位流通常驻留在同一板上的非易失性存储器中。FPGA内部产生称为称为CCLK的配置时钟信号,FPGA通过闪存发送时钟或地址来控制配置过程。其框图如图2所示。

图2 主配置模式

从模式

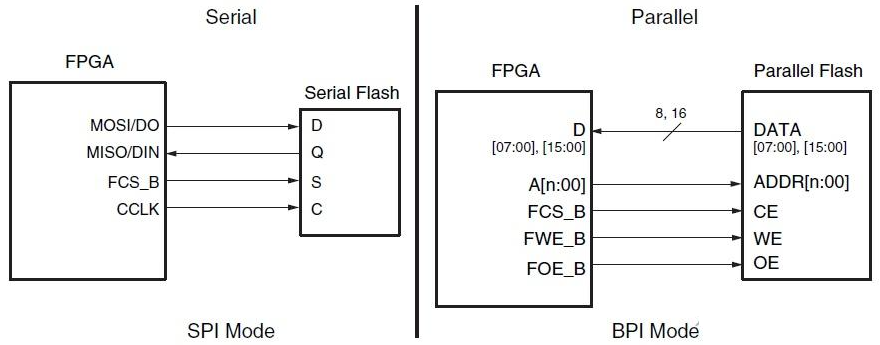

外部控制加载FPGA配置模式,通常称为从模式,也可用于串行或并行数据传输路径。在从模式下,外部处理器、微控制器、DSP处理器或测试器将配置图像下载到FPGA中,如图3所示。从配置模式的优点是FPGA比特流几乎可以驻留在整个系统的任何地方。比特流可以与主机处理器代码一起驻留在闪存中,驻留在硬盘中或者通过网络连接的某个地方。

图3 从配置模式

从串行模式是一个简单的接口,由时钟和串行数据输入组成。从SelectMAP模式是x8、x16或x32位宽处理器的外围接口,包括芯片选择输入和读写控制输入。

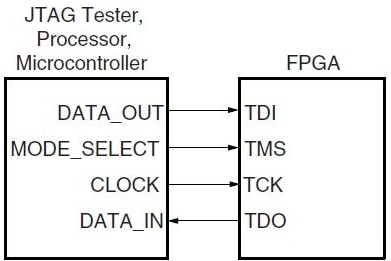

JTAG连接

JTAG模式同样是串行配置模式,广泛用于原型制作和板测试。四引脚JTAG边界扫描接口在板载测试设备和调试硬件很常见。Xilinx基于UltraScale架构的FPGA编程电缆使用JTAG接口进行原型下载和调试。如图4所示。

图4 JTAG配置模式

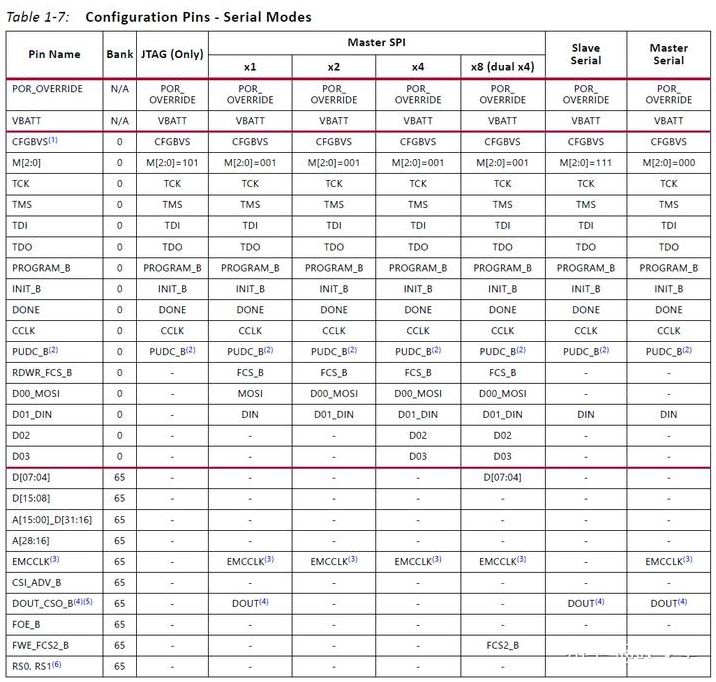

串行配置模式详情:

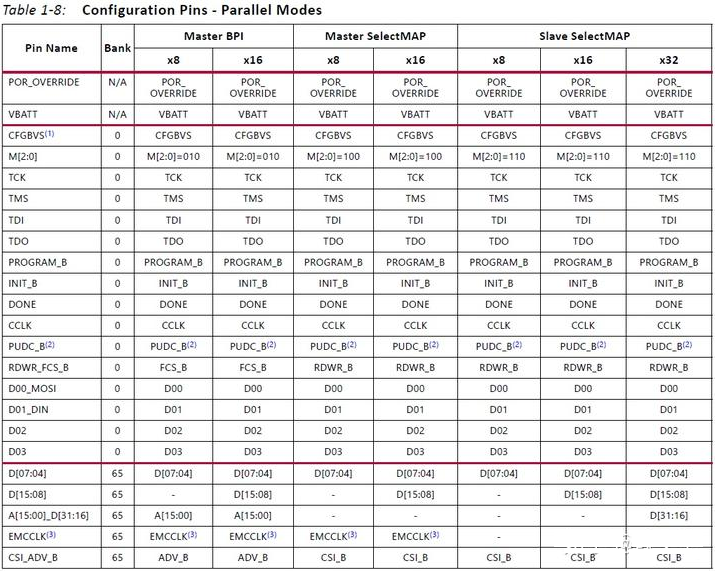

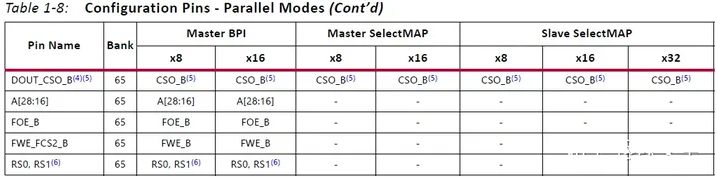

并行配置模式详情:

总结:

1. 在设计电路图时,为选择最优的FPGA配置方案,需主要考虑以下4个方面:总体设置,下载速率,成本,配置灵活性。

2. 在主模式下,FPGA自动加载配置文件数据,该配置文件数据存储于板载ROM里;从模式下,通过外部MCU/处理器将配置文件数据加载到FPGA中。

3. 用作配置FPGA的专用管脚在配置完成后不能够被用作普通IO管脚,而非专用管脚在配置完毕后即被释放,可用做普通IO管脚。

4. 电路设计时,一定要对M[2:0]管脚进行正确的电平设定。为了今后扩展需要或者暂时不确定为FPGA选择何种配置模式,可为M[2:0]管脚同时预留上拉和下拉电阻,便于灵活选择。

(SpringBoot三板斧、SpringBoot Actuator))

)

)

MOV)