参考文献:

一、绪论

1.1 背景

“串行替代并行”:

串行传输使用差分信号传输以传输更长距离;

并行传输因串扰无法长距离传输;并行线路对信号偏斜量的要求,限制了最大的传输速率。

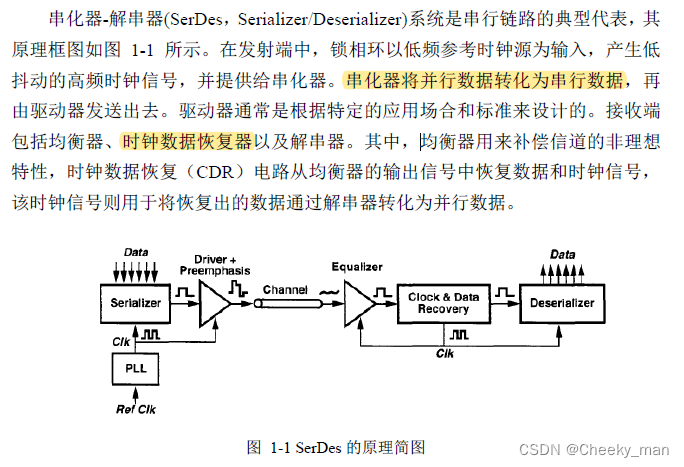

SerDes=Serializer + Deserializer

Serializer:用于Tx端,译为串行器,将并行数据转化为串行数据(并转串)。

PLL:时钟源,以低速参考时钟作为输入,产生低抖动的高频时钟信号,供给Serializer。

Channel:传输串行信号(数据信号+时钟信号)的物理链路,存在非理想效应。

Equalizer:均衡器,消除链路中的非理想特性。

CDR:时钟数据恢复器,因为时钟和数据是通过同一channel一起传输的,接收端需要区分。

Deserializer:用于Rx端,译为解串器,从串行数据中恢复出并行数据。

高频对背板的影响较大,会使ISI(码间干扰)恶化,因此采用均衡器对信道进行补偿。

二、高速串行链路基础

本质上,高速接口的作用就是保住发射出的信号和接收之后提供给后续电路的信号具有良好的信号完整性。

2.1 随机二进制数据

长串连续的0或1会给数据恢复等带来影响,因此有通信协议规定了最大连续序列长度。

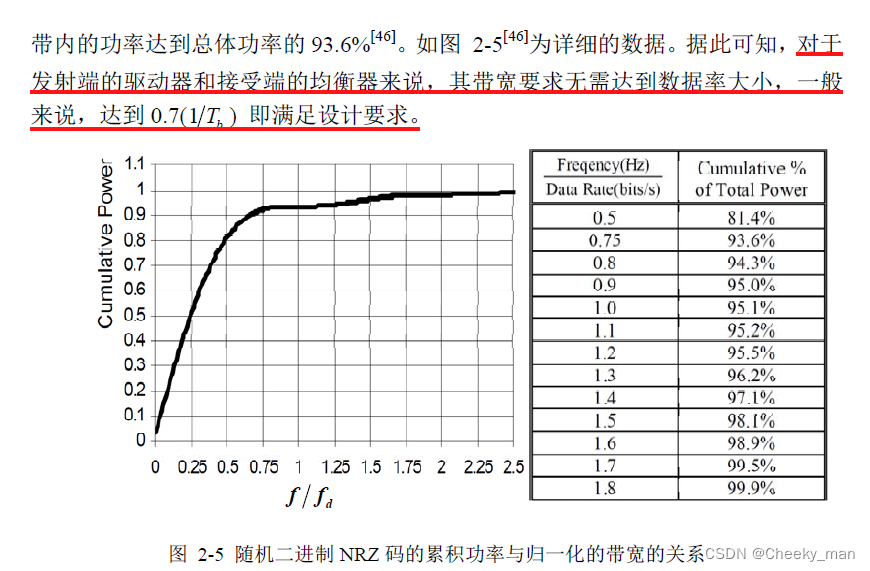

信号的频率分量的功率随频率增加而大幅下降。

对于Tx端的driver和Rx端的Equalizer来说,其带宽要求无需达到数据率大小,一般来说,达到0.7*数据率即可。

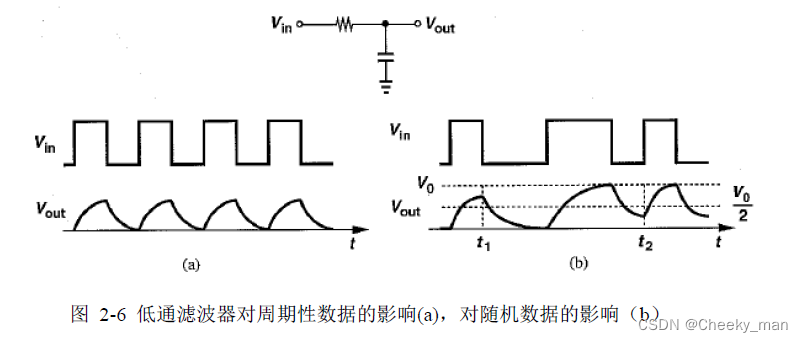

理想的周期性方波,通过LPF时,其高频分量受到衰减,因此时域上表现出上升时间和下降时间不再为0.

而对于随机二进制数据,连续1的出现,会使输出电平接近V0;连续0的出现,使其接近0,这种输出电平随数据保持时间的变化,导致判决阈的确定十分困难。

以上就是ISI现象:输出信号因输入而出现了“拖尾”。

---C++)

—— 神经网络自然语言处理(2)实际应用)

)

)