硬块规划器

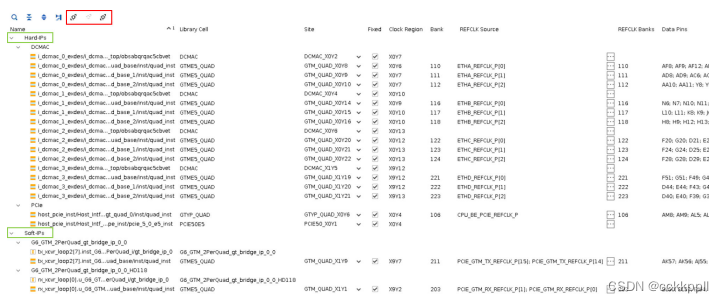

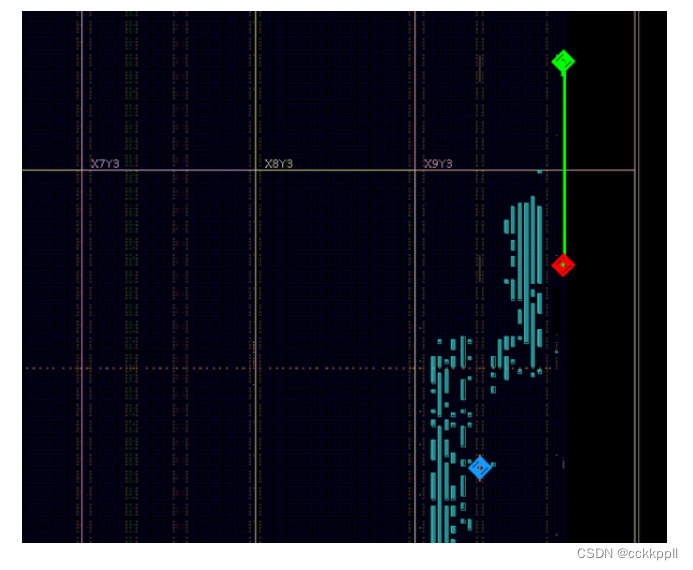

Versal自适应SoC的硬块规划GT组件从通用/通道更新为AMD的GT_QUAD粒度Versal™ 自适应SoC。为了启用某些GT共享用例,对GT向导流进行了修改使用Vivado IP集成商。使用Vivado IP集成商构建使用单个或多个GT_ QUAD。连接到GT_QUAD的自定义IP的设计条目为通过桥接IP,桥接IP通过Block Automation实例化、配置和连接单个或多个基于GT Quad的IP。因为GT_ QUAD可以在多个IP之间共享,GT_QUAD和REFCLK位置未在IP积分器中分配。硬块规划器提供了一个直观的用户界面来分配GT_QUAD和REFCLK位置。Hard Block Planner(硬块规划器)窗口将GT_QUAD分组到硬IP下,如PCIe®和DCMAC。此外,它提供了一种易于使用的机制,可以使用设备站点。硬块规划器在设备窗口中提供位置的视觉反馈REFCLK引脚的GT_QUAD和硬IP块。它还列出了设计中的软IP在硬IP旁边的单独下拉菜单下(以绿色突出显示),以便于规划其相关的GT区块。支持的硬IP列表包括DCMAC、MRMAC、PCIe®、,CPM和ILKN。一旦您打开一个合成设计,它就会读取和处理网表对象收集设计中可用的所有硬IP。此计划器允许您在中交叉探测位置用于更改或分配站点的设备窗口视图。中的“硬块规划器”选项只有在打开综合设计或实现的设计后,才会显示Windows菜单。坚固的Block Planner窗口顶部有3个按钮(以红色突出显示)。左边的第一个按钮标记蓝色的所有硬块、红色的所有相关联的GT和绿色的REFCLK源。中的按钮中间对所选择的IP组执行相同的操作。右侧的最后一个按钮将删除标记从所有项目中清除设备视图。这些按钮可用于快速浏览设备视图中IP及其相关GT的相对位置。

使用硬块规划器

要创建硬块规划的设计,请完成以下步骤

1.创建一个以AMD Versal为目标的项目™ 自适应SoC。在这个实验室中,您可以创建PCIe®针对xcvc1902-vsvd1760-1LP-i-L的设计。确保不要在中指定源在创建RTL项目时选中此时间选项。

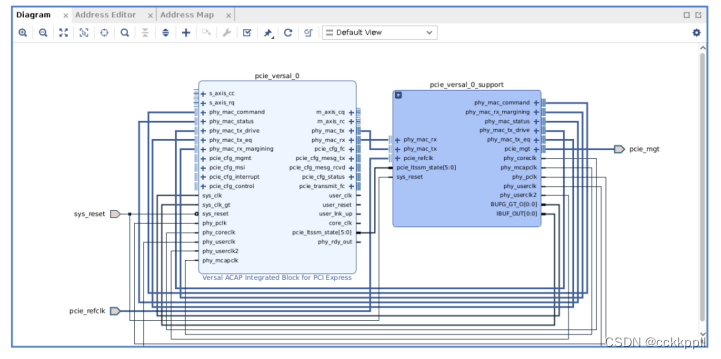

2.项目加载后,单击BD画布中的+按钮添加Versal ACAP IntegratedPCI Express IP的块。

3.在BD画布上添加IP后,单击出现的Run Block Automation功能区BD画布上方。

4.运行块自动化实例化pcie_versal_0_support块。此块包含PCIE与外部世界通信所需的GT模块。

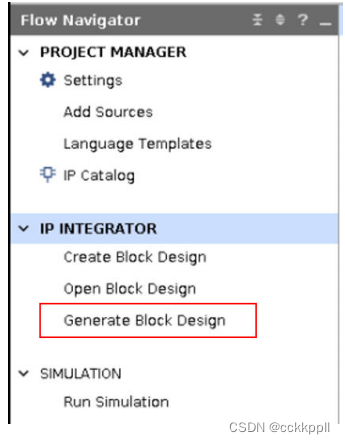

5.块自动化完成后,单击IP下的“生成块设计”选项“流导航器”窗口的“集成器”菜单。当出现后续提示时,将设置保留为默认设置,然后单击“生成”按钮。

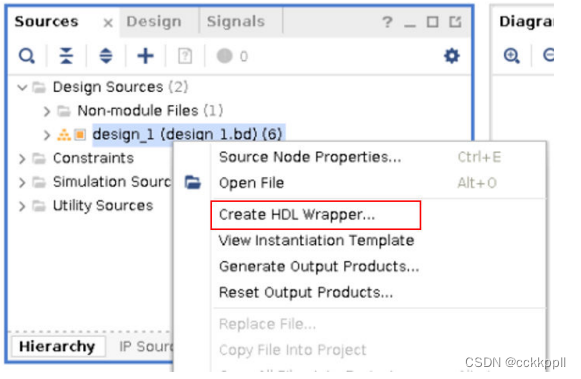

6.在合成设计之前创建一个顶级的HDL包装器。

7.下一步是综合设计并打开综合设计。硬块只有打开合成设计后,Windows菜单中的“计划器”选项才会出现。

8.打开综合设计后,硬块规划器读取并处理网表对象并收集设计中可用的所有硬IP。此计划器允许您交叉调查设备窗口视图中用于更改或分配站点的位置。

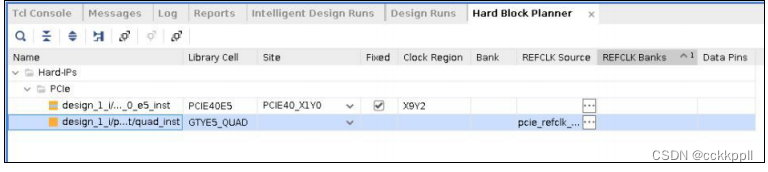

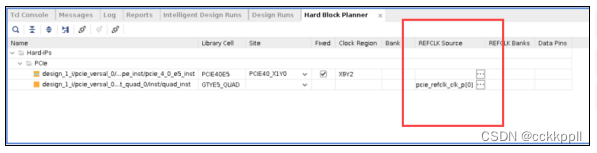

9.在您当前的设计中,您有两个硬IP(PCIE40E5和GTYE5_QUAD),它们的位置可以使用硬块规划器工具进行规划。您可以通过选择下拉菜单来执行此操作菜单,然后从列表中选择合适的网站。

注:PCI Express硬IP的站点由IP Integrator中的PCI Express IP预先确定。

10.对于GT_QUAD,您也可以使用REFCLK source规划REFCLK源的放置柱

11.在硬块规划器窗口中选择PCIe®硬IP组。The Show Hard IP“选定IP组的连接”选项变为可用。选择该图标以标记该组中的硬IP为蓝色,相关的GT为红色,REFCLK源为绿色。

)

)

--数据应用之内部报表及数据分析)