专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

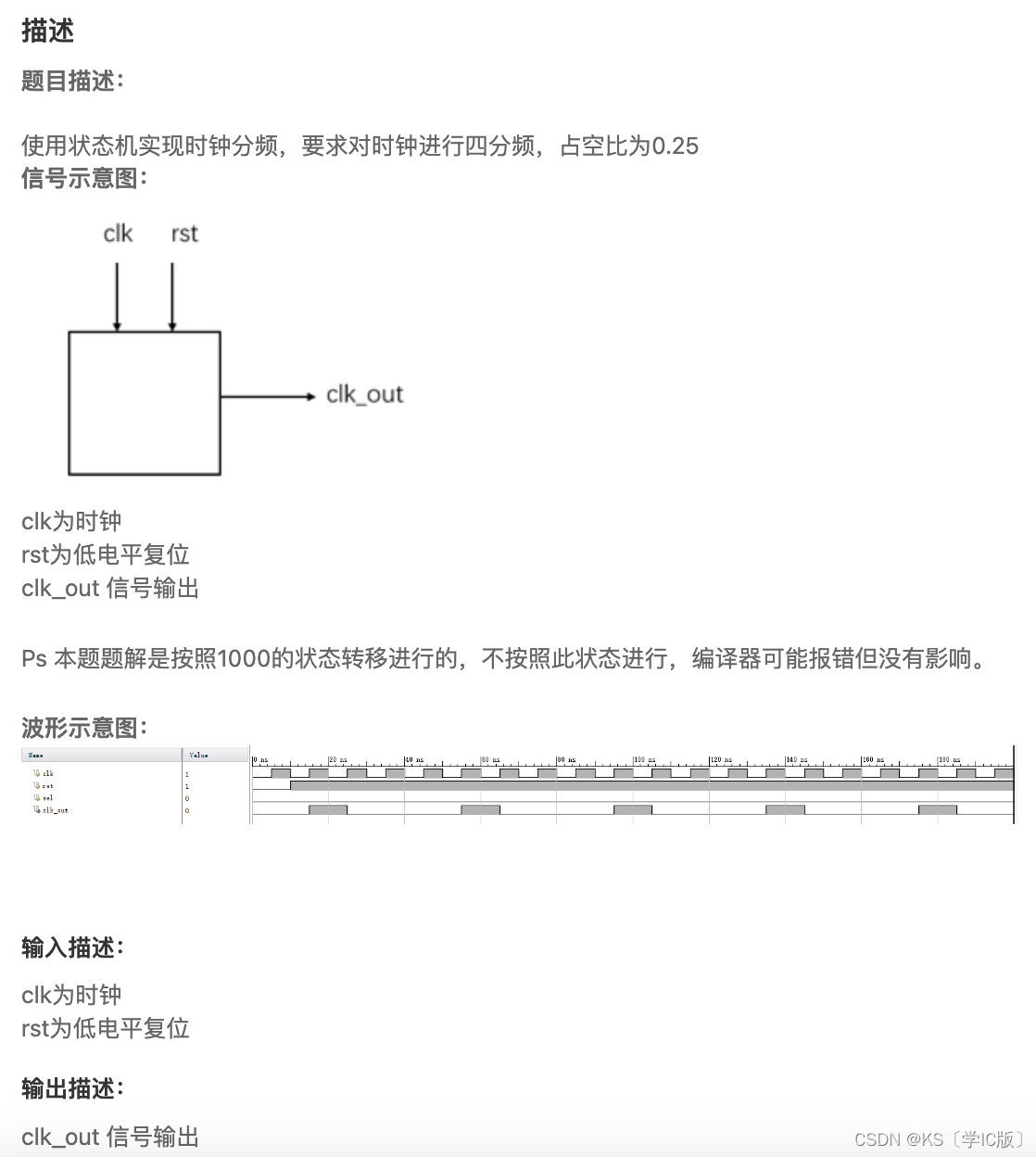

状态机写法

`timescale 1ns/1nsmodule huawei7(input wire clk ,input wire rst ,output reg clk_out

);//*************code***********//parameter S0 = 0, S1 = 1 , S2 = 2 , S3 = 3 ; reg [2:0] state, nstate ; always @ (posedge clk or negedge rst) if (~rst) state <= 0 ; else state <= nstate ; always @ (*) case (state) S0 : nstate = S1 ; S1 : nstate = S2 ; S2 : nstate = S3 ; S3 : nstate = S0 ; default : nstate = S0 ; endcasealways @ (posedge clk or negedge rst) if (!rst) clk_out <= 0 ; else if (state == S0) clk_out <= 1 ; else clk_out <= 0 ; //*************code***********//

endmodule不用状态机的写法

`timescale 1ns/1nsmodule huawei7(input wire clk ,input wire rst ,output reg clk_out

);//*************code***********//reg [2:0] cnt ; always @ (posedge clk or negedge rst) if (!rst) cnt <= 0 ; else cnt <= cnt == 3 ? 0 : cnt + 1 ; always @ (posedge clk or negedge rst) if (!rst) clk_out <= 0 ; else if (cnt == 0) clk_out <= 1 ; else clk_out <= 0 ; //*************code***********//

endmodule

)

详细教程)