Timing Borrow技术又称为cycle stealing技术,主要是利用latch的电平敏感特性,通过有效电平获取数据,通过无效电平保持被锁存的数据,主要用于解决路径时序不满足电路要求的情况。

通过TimingBorrow可以对电路进行加速,当路径延迟较大时,可以通过借用latch的部分时间实现数据的锁存从而可以提高设计运行的频率。采用TimingBorrow设计时,一定要注意前级电路借用时间与后级电路剩余时间之间的关系,某些情况下,timing borrow的错误理解会对综合和后端实现产生严重的时序问题,需要正确理解和规范使用。

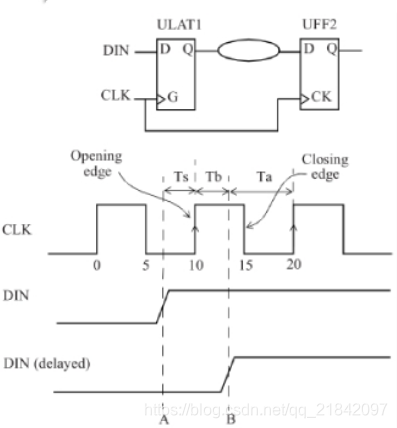

我们先从锁存器说起:在一个锁存器中,时钟的一个沿之后,会使得锁存器变得透明(即这个时钟沿打开了锁存器,使得锁存器的输出与数据输入相同),我们把这个沿叫做opening edge;时钟的另一个沿之后,会关闭锁存器(即这个时候数据输入即使有任何变化,锁存器输出也不会改变),我们把这个沿叫做closing edge。

一般来说,锁存器的输入数据应该在时钟有效沿之前准备好,但是由于锁存器在时钟有效电平时是透明的,因此,数据能在时钟有效沿之后到达,可以向下个时钟周期“借时间”(borrow time)。需要注意的是,一旦“借时间”,用于后级电路的时间会减少。

以上图为例,如果输入数据在B时刻到达,那么相当于向下一个时钟借了Tb时间。但是,这样减少了锁存器到下一个寄存器UFF2的时间,时间只剩下了Ta。

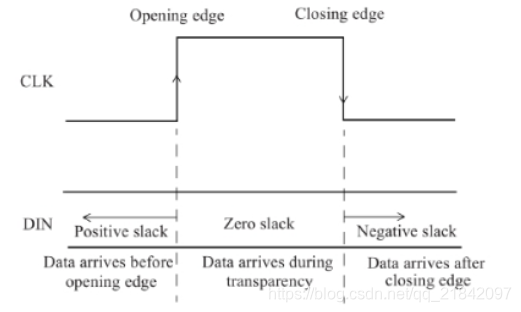

- 如果数据在锁存器的opening edge之前到达,那么其行为与寄存器类似。opening edge会捕获数据并且opening edge作为下一时序路径的起点将数据传输出去。

- 如果数据在opening edge与closing edge之间(锁存器透明)到达,那么会产生timing borrow。借出的时间会决定下一时序路径的起点。

对于Timing borrow的情况,我们会依据下图分为三种:

如果数据在negative slack到达,那么timing borrow技术也失效了,会导致时序违背(violation)。

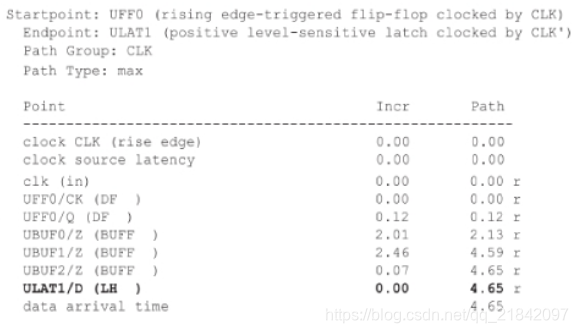

我们来看看在positive slack的时序报告:

这里我们不需要进行time borrow。

)

)

Hibernate高级配置)

)