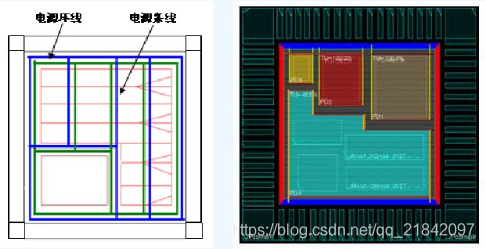

电源规划是给整个芯片的供电设计出一个均勻的网络,它是芯片物理设计中非常关键的一部分。电源规划在芯片布图规划后或在布图规划过程中交叉完成,它贯穿于整个设计中,需要在芯片设计的不同阶段对电源的供电网络进行分析并根据要求进行修改。,主要分三部分内容进行分析:电源网络设置、数字与模拟混合供电、单电源与多电源供电电源网络设置。其中电源环线(power ring)和电源条线(power stripe)的设置为主要工作。

如上图所示,左图中左下角为硬核部分,硬核部分的上方和右侧的电源线称为模块电源环。右图是多电源多电压中应用的电源环分布示意图。

芯片供电是通过I /O 单元来实现的,在做电源规划和电源网络设计时,首先要做电源预算(power budgeting),商用产品惯例认为总的误差应当控制在5%之内。它包括从电源网络和PCB板级到封装bonding之间的波动(约为1%),再到电源I /O 单元和电源环之间的波动(约为1%)和最终直至标准单元之间的电压降(约为3% ) 。更准确的预算则通过功耗分析的手段来做定量计算。

一、电源网络的设计

这里阐述的电源网络设计是针对于普通的I /O 单元四方分布的数字芯片设计,对于复杂的数模混合设计以及多电源设计将在后面的分别阐述。供电网络设计主要内容有以下几部分组成:

- 电源连接关系的定义,又称为global net connect。

- 芯片核内(core)部分的电源环设计,又称为power ring。

- 芯片内所包含的硬核(如RAM、ROM以及IP、COT模块等)的电源环设计。

- 芯片核内纵横交错的电源网格的设计,又称为power stripe。

- 芯片的供电单元与电源环的连接,又称为I /O 单元power。

- 芯片内部电源网格和硬核电源环连接部分的设计,又称为ring pins。

- 将标准单元的供电网络与核内电源网格总连接设计,又称为followpins。

- I /O供电单元电源环的设计,又称为I /O单元power ring。

最后我们还需要对电源网格进行检查,检查是否存在短路和开路以及供电不足等问题。对于Flip Chip的设计,供电网络的设计还包括电源凸点bump的设计以及布线。下面分别介绍各部分的内容。

1、全局电源

在电源网格设计中,首先要对电源进行定义,主要包括:全局电源的定义以及连接关系的定义。全局电源网络连接(global net connect)是指把相应的端口和网络连接到合适的电源和接地网络上去,从而使得我们针对整个设计可以正确无误地顺利完成供电网络设计、电源布线、详细布线和功耗分析等步骤。这些终端和网络的连接信息一部分包含在Verilog网表中,另一部分则包含在相应的LEF文件当中。

通过Verilog网表中的定义,我们可以把以下几种类型的网络连接到相应的全局电源和接地网络上去。

- 电源和接地网络

它是将网表中每个标准单元和模块等的电源和接地网络连接到合适的全局电源和接地网络上去。这些标准单元和模块等的电源和接地网络互连关系,在Verilog网表中主要通过关键字“wire”进行定义。

- 接高电压和接低电压网络

它是将接高电压和接低电压网络连接到合适的全局电源和接地网络上去。它们之间的互连关系,在Verilog网表中主要通过关键字“ 1'b0”、“ 1'b1”、“supply 0”,以及“supply 1”进行定义。

- 电源和接地端口

它是将供电端口和接地端口连接到合适的全局电源和接地网络上去。诸如“VDD、vdd、vdd!”和“VSS、vss、gnd!”等就是这些电源和接地端口和网络在LEF文件中定义的名称。

- 填充单元网络

它是将供电端口连接到合适的全局电源和接地网络上去。在添加填充单元前后,均可通过手工指定相应的连接关系。

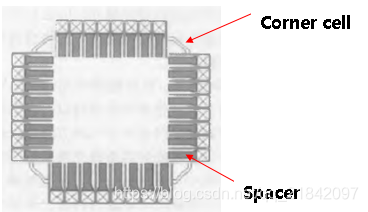

I / O 的拐角单元(corner cell)和I / O 填充单元(filler,spacer)。 因为I / O 在芯片周围通常需要摆放成类似戒指(ring)一样的环形,因此通过这两个单元可以填充I /O单元之间的空隙以使它们形成电源和地的环状网。

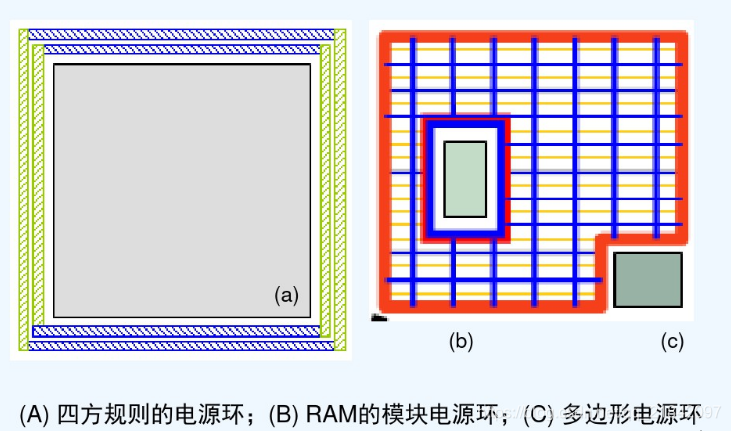

2、电源环线

电源环线(power ring)是指为了均勻供电,包围在标准单元周围的环形供电金属,它也是连接供电I /O 单元和标准单元的桥梁,供电I /O 单元通过金属连接到电源环,标准单元通followpins连接到电源环,从而构成了供电I /O 单元给标准单元以及硬核供电。电源网格是为了平均分布电流,缩短电流回路,在有效减小电压降的同时,避免由于电流分布不均时造成的热点(hot spot)现象以及电迁移(EM,electromigration)问题。

电源环的设计主要有3个参数:电源环的宽度、电源环的间距d 以及电源环的对数n。电源环的参数也是根据功耗计算得来。

- 电源环的宽度

根据整个芯片的供电峰值电流以及厂家所给的设计规则中所允许的电流密度以及电源环的对数n所决定。

式中,是芯片的峰值电流

是厂家工艺库给出的电流密度上限

是电源环的数目

是调整因子,根据芯片的供电I /O单元分布而定

- 电源环的间距

电源环的间距根据厂家所给的设计规则中的最小间距决定,一般情况下为最小间距的2倍左右,但是也有工程师提出尽量减小电源环之间的间距,从而增大电源环的耦合电容,从而起到过滤电源噪声的作用。

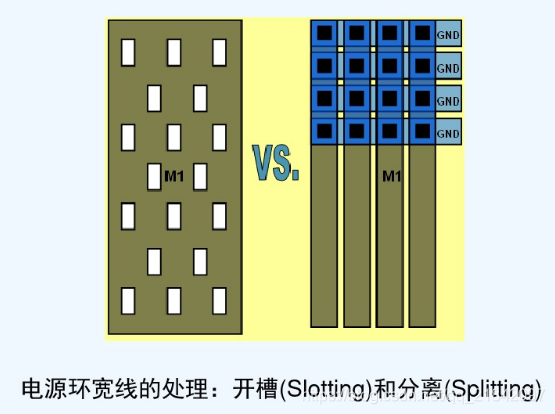

除以上两个参数外,在芯片的制造过程中,一般宽线需要打孔散热,所以厂家会制定宽线的规则。一般情况下,希望单个电源环的宽度不要超过厂家规定的宽线规则,从而避免打孔,打孔在芯片设计中又称为slotting,更好的办法是用splitting。电源环的对数n 由芯片的面积、厂家的设计规则、金属的层数等多种因素决定。当金属的层数较多时,可以选用多层金属布置电源环,从而有效减小电源环的宽度和减小电源环所占据的芯片的面积。

在有些设计中,还需要对硬核及RAM设计电源环,RAM以及硬核电源环宽度的设定也是根据硬核的供电电流决定,其设计的方法与核内的电源环相同,只需要指定电源环的所有参数便能自动生成。很多厂家提供的硬核在设计时已经产生了电源环,当应用到芯片顶层时只需要将电源网格连接到硬核内部自身的电源环即可,从而减小不必要的面积浪费。

3、电源条线

芯片内部纵横交错的电源网格(power grid)或“电源条线"(power stripes)设计有专门的理论和算法。电源网格通常为均匀分布,电源条线通常是不规则或不均匀分布,电源网格可以看成是电源条线的特例。简单说明电源条线相关内容。

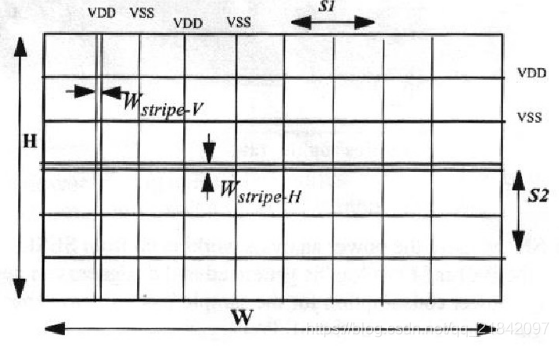

从上图中我们看出,电源网格中重要的4 个参数分别是:纵向电源条线的宽度,横向电源条线的宽度

;横向电源条线的间距

;纵向电源条线的间距

。其中纵向电源条线的宽度

与横向电源条线的间距

成正比关系,也就是说宽度较大,间距就可以较大,电源条线的分布可以稀疏一点;横向电源条线宽度值较小,间距也应该小一点,电源条线的分布需要密集一点。与纵向电源条线相比较,横向电源条线的宽度

与其间距

的正比关系也存在,但是由于在横向有很多标准单元的followpins的存在,需要的横向电源条线比纵向电源条线要少很多。

对于和

的设定,有以下几个经验规则:

的分布间隔一般取垂直布线间距(pitch)的整数倍,其目的是充分利用布线通道其值不能太大,一般情况下不要超过最小二输入与非门宽度的4倍。每一层金属的pitch在物理库中都有相应的定义。

-

的最大值取标准单元库中最小与非门宽度的4倍。当芯片的利用率较高,布线拥塞程度较大时,一般选择细密的电源网格。如果芯片的利用率非常低,那么将电源网格设计得越宽,其线上的电阻越小,电压降越小。

-

的取值一般是标准单元高度的整数倍,通常选择1倍或者2 倍。

电源条线所选用的电源层也根据LEF中的规定所选,纵向必须用偶数层走线,横向必须用奇数层走线。由于高层金属具有较小的寄生电阻,用高层金属走线可以有效地减少电压降。

二、数模混合供电

即使是纯数字电路芯片设计,通常也要用到一个模拟模块PLL作为时钟信号发生器。今天的SoC设计中,数模混合电路则更加普遍,A/D、D/A及PLL等模拟模块的集成到处可见。在数模混合供电设计中,需要特别注意电源信号之间的干扰和隔离,因而需要建立不同电源区域(power domain)。在布局前一般需作如下几点考虑和处理:

- 模拟模块的工作区域一般放置于芯片的某个角落。当设计中有多个模拟单元时,将多个模拟单元的位置应相对集中在芯片的某个角落,其中间不应该混合放置数字模块。

- 模拟区域需要单独供电,给模拟信号供电的I /O 单元应放在模拟模块边上,尽量缩短供电线路的长度。

- 在模拟模块的周围布置保护隔离环(guarding ring),从而实现数字信号和模拟信号电源之间的隔离。

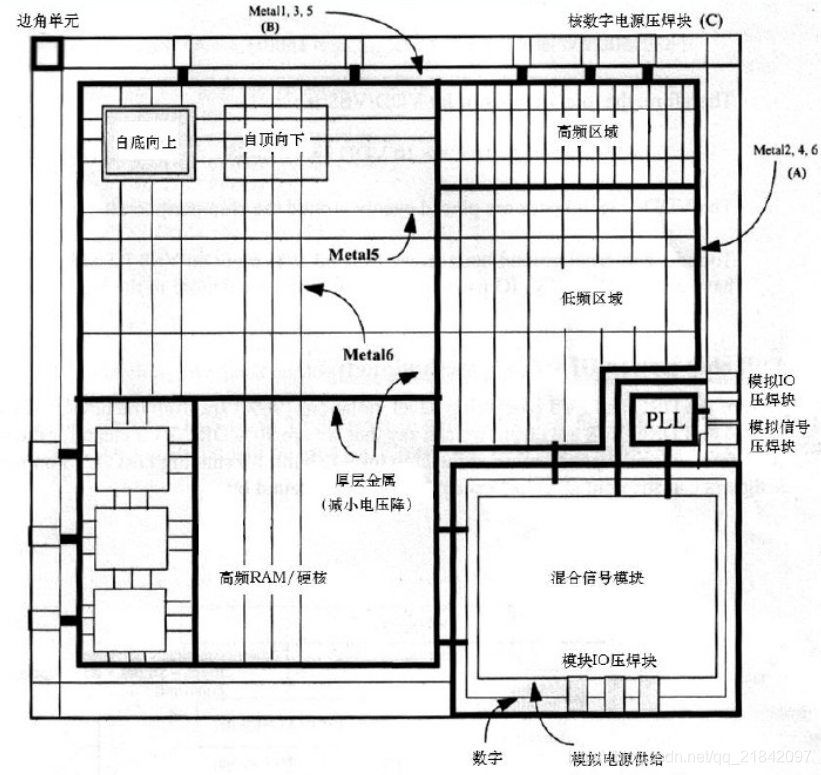

如上图所示,电源规划中的一些细节问题如下

- 数模信号模块的放置。模拟PLL和模拟信号模块处于芯片的右下角,右下角的I /O 单元均为模拟信号用的信号端口,在PLL和模拟信号模块的周围放置的都是低频信号模块,以避免数字信号跳变对模拟信号的影响。

- 数模信号模块的供电。模拟PLL和模拟信号模块均分别具有数字供电和模拟供电两部分组成,其中模拟供电在内部,数字供电在外部,两个模块之间的模拟供电环是相通的,在外围的数字供电部分与芯片的数字供电部分相联合,在其底下加上保护环(guarding ring)用以隔离。在有些设计中,在条件允许的情况下或者严格要求下,既具有模拟供电也具有数字供电的模拟单元,数字供电部分也需要单独供电,并与核内的其他数字供电部分保持隔离。

- 数模信号模块中的电源环。电源环设计可以采用多层金属完成,从而节约电源环的宽度,降低电源环所占据的芯片面积。数模信号模块中的电源环分别处理,相互独立。

- 数模信号模块中的电源网格。数模信号模块中的电源网格设计采用高层金属完成布线,在高频区域,电源网格较为密集,而在低频区域电源网格较为稀疏。

- 数模信号模块中的电源设计方案。在整个芯片中,模块的电源设计部分采用了自上而下和自下而上的两种设计过程,这是模块电源的典型设计方法。

三、多电源供电

在数字芯片设计中,多电源供电(MSV,muki-Siipply voltage)早就被用来处理数模混合电路的供电。在数模混合电路的供电方案中,MSV专指多组电源同样电压(如均为1.2 V)供给不同电路(数字、模拟)。随着低功耗设计技术的更多应用,同一芯片中则更多地采用多组电源多组电压供电(MSMV,multi-supply multi-voltage)的方案。除了保留传统的MSV的方法外,其中,关键模块采用高电压供电,频率较低的模块采用低电压供电是有效降低功耗的一种方法。

1、电源规划

每一个电压域当中都必须有完整的电源和地线电源环。在创建电源环时,可以采用传统的方法,即根据布图规划的情况指导工具完成设计,也可以通过自动供电网络设计工具(APP,automatic power planner)为每一个电压域指定一个合适的模板来进行设计,其步骤如下:

- 创建芯片核心电源环,其方法与单电源环设计一致,单电源环只有一对供电,而多电源环有多对电源供电,故而会占用较大的面积。

- 为每一个电压域和硬宏单元模块创建一个模块电源环。在多电压设计中,首先需要定义电压域的内容,即每个电压域的工作电压和所包含的模块,如果为相应电源环所指定的电源和地线网络同电压域定义的电源和地网络不匹配,工具则会产生相应的警告提示。

- 为宏单元(硬核)模块创建模块电源环。

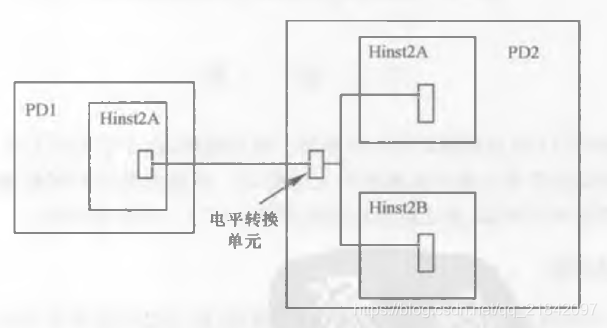

2、电平转换单元的插入

在多个电源供电时,不同的工作电压区之间需要插人电平转换单元(VLS,voltage level shifter),其步骤如下:

- 读入相应的电平转换单元表。

- 在内部电压域网络上插入电平转换单元。

3、隔离单元的插入

当设计中存在被关闭的电压域,为了不使关闭区域与非关闭区域相互影响,必须在所有的接口处添加隔离单元(isolation cell),并要:①检查出所有需要添加隔离网络的信号端口 ;②在相应的接口信号处添加隔离单元。

四、总结

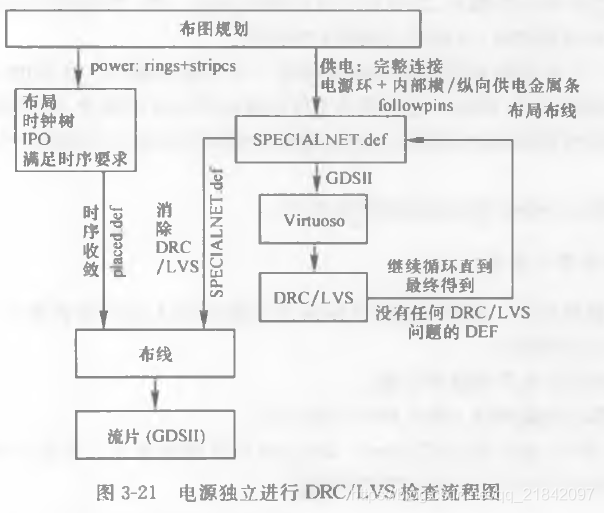

布图规划与布局之间的电源规划工作越来越复杂,其重要性也越来越大。设计中发现,不少DRC/LVS问题与电源规划或电源设计有关。大多数的模块级或芯片级DRC和LVS错误都是由供电问题引起的。由于DRC/LVS工具对于电源的抽取是通过一定的规则来提取,因此对于结构相同的电源部分,工具并不能很好地识别,从而会造成LVS的错误。因此在用sign-off的工具进行LVS检查时,设计者可以“剔除”掉除电源和接地网络外的所有其他单元和模块,单独运行仅仅针对供电网络的DRC/LVS检查和仅对内部网络的检查,其流程如图:

:Regullar Expressions的使用)

)

)