01、 引言

图像传感器目前用于多种应用。自 1969 年电荷耦合器件 (CCD) 发明以来,固态图像传感器已蔓延到各种消费市场,例如小型摄像机和数码相机。自 2005年以来已成为主流固态图像传感器的 CMOS 图像传感器在为 CCD 开发的技术的基础上不断发展。除了目前最大的图像传感器市场智能手机之外,对图像传感器的需求正迅速扩大到用于安全的网络摄像头、用于工厂自动化的机器视觉以及用于辅助驾驶和自动驾驶系统的汽车摄像头。

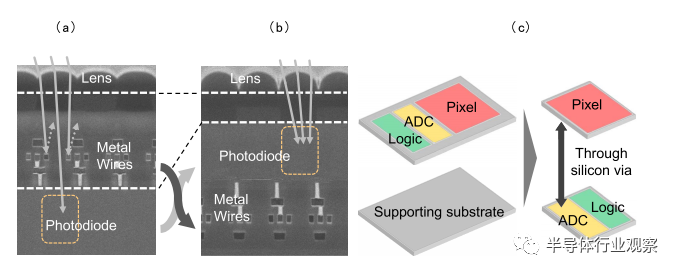

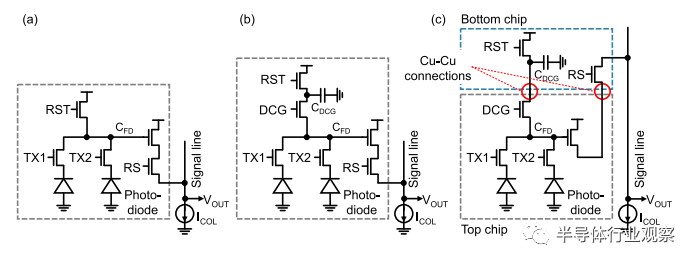

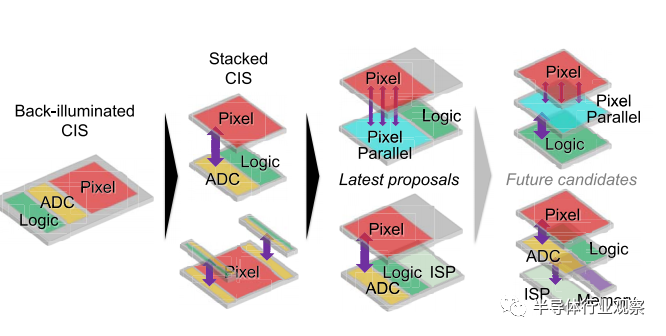

CMOS图像传感器技术的一个主要转折点是背照式(BI)图像传感器的成功开发,这使得图像传感器的堆叠结构的发展成为可能,如图1所示。在最初的前照式 (FI) 结构中,很难减小传感器的像素尺寸,因为入射光必须由光电二极管通过金属线包围的间隙收集。由于背照式(BI)结构大大提高了灵敏度并允许金属布线的灵活性,而且由于晶圆键合和极其均匀的晶圆减薄技术,它已成为图像传感器的热门产品。图像传感器逐渐向堆叠结构发展,其中逻辑电路直接集成在基底晶片上。堆叠工艺允许更先进的CMOS工艺中高度并行的模数转换器 (ADC) 和信号处理元件的更高集成度,独立于为像素光电二极管定制的传感器工艺。堆叠设备结构继续极大地改变图像传感器架构。

图 1. CMOS 图像传感器的结构。(a) FI 结构,(b) BI 结构,和(c)具有通孔的堆叠结构。

本文回顾了具有堆叠设备的图像传感器架构的发展趋势,以显著加速性能改进、扩展传感能力以及集成连接到传感器层的边缘计算功能。第二部分介绍了堆叠设备配置的不同传感器架构,这些架构通过高度并行的列并行 ADC 实现高像素分辨率和高帧率成像。第三部分介绍了一些使用像素间距 Cu-Cu 连接(pixel-pitch Cu–Cu connections)实现的高级像素电路,这些电路对于在实际像素分辨率下实现更好的像素性能至关重要。像素间距 Cu-Cu 连接也使传感器架构逐渐向像素并行数字化方向发展。第四部分介绍了扩展传感能力的传感器架构的一些进展,例如空间深度、时间对比传感和不可见光成像。第五部分介绍了集成边缘人工智能 (AI) 加速器的视觉传感器。最后,第六部分给出了一些结论。

02、使用超过百万像素的电影录制

电影录制需要至少每秒 30 或 60 帧 (fps) 的帧速率,即使像素数量正在从 200 万像素高清 (HD) 格式增加到 800 万像素 4K 格式。此外,更高的帧速率操作,例如 120、240 或 1000 每秒传输帧数(fps),可以提供慢动作回放。自 1997 年提出列并行 ADC 架构以来,通过增加并行 ADC 的数量和加快 ADC 操作本身的速度,帧速率得到了改善。由于可以将最佳工艺技术应用于传感器像素和外围设备,堆叠结构有助于充分提高帧速率。传感器制造需要几种离子注入工艺来形成具有低结泄漏的光电二极管和晶体管。然而,逻辑工艺(the logic process)需要低电阻和高速晶体管。对于像素来说,三层或四层布线通常就足够了,但逻辑电路大约需要十层布线。所使用的堆叠技术可以缓解同一芯片上非堆叠图像传感器的冲突约束,包括传感器像素和逻辑电路。

A. 双列 ADC 架构

目前,大多数 CMOS 图像传感器包括一个像素阵列、数千个以列并行结构组织的 ADC 和逻辑电路。如图 2(a) 所示,位于像素阵列外部的硅通孔 (TSV) 以高度并行的方式将像素列连接到 ADC。在 2013 年推出的第一个堆叠 CMOS 图像传感器 中,列 ADC 的模拟和数字部分分别被分成顶部和底部芯片,如图 2(b) 所示。2015 年,提出了双列 ADC 架构,并在 16M 像素下实现了 120 fps 的帧速率,其中列 ADC 完全移至底部芯片,如图 2(c) 所示。传感器芯片采用用于光电二极管的 90 纳米传感器定制工艺制造,仅使用 NMOS 逻辑。而逻辑芯片采用 65 纳米标准 CMOS 工艺制造。由于列 ADC 可以独立于传感器芯片来实现,因此 ADC 可以高度集成。除了提高帧速率外,还将冗余并行 ADC用在通过平均多个模数 (AD) 转换来降低噪声,如图 3 所示。一个像素的输出同时分配给两个 ADC,两个数字输出相加以再现图像帧。两个 ADC 的时序相位略有不同,以通过降低其噪声信号之间的相关性来实现降噪。

图 2. 堆叠 CMOS 图像传感器的实现。(a) 光电二极管和逻辑电路之间的 TSV 连接。(b) 首个堆叠的 CMOS 图像传感器。(c) 双列 ADC 架构。

图 3. 双列 ADC 架构的简化框图(左)和噪声特性的改进(右)。

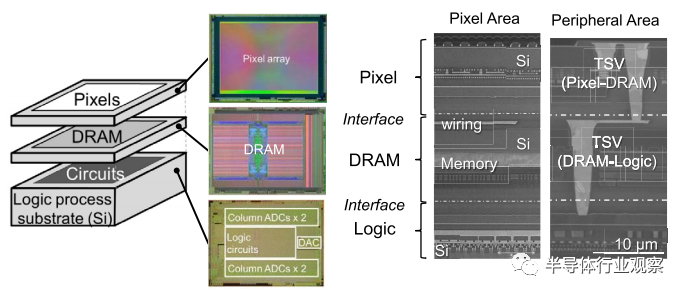

B. 具有动态随机存取存储器 (DRAM) 的三层堆叠 CMOS 图像传感器

随着像素和并行 ADC 数量的增加,图像传感器会输出大量数据。2017 年,提出了一种三层堆叠的 CMOS 图像传感器以记录 960 fps 的慢动作视频,如图 4 所示;三层之间通过硅通孔(TSV)连接,从并行 ADC 获得的数据缓存在第二层 DRAM 中,以实现慢动作捕捉。对于超慢动作录制,当来自 ADC 的数字数据通过 102-Gbit/s 总线临时缓冲在 DRAM 中时,该传感器可以在全高清分辨率下以 960 fps 的速度运行。当传感器在 30 fps 的电影拍摄过程中检测到用户的触发或场景中的快速运动时,读出速度将变为 960 fps。在 DRAM 中一次最多可以存储 63 帧全高清分辨率,并在随后的电影捕捉过程中输出缓冲数据。

图 4. 带有 DRAM 的三层堆叠 CMOS 图像传感器。

C. 用于Large Optical Format芯片堆叠于晶圆之上(Chip-on-Wafer)技术

迄今为止推出的堆叠式 CMOS 图像传感器是在晶圆上晶圆 (WoW) 键合工艺中制造的。然而,由于传感器和逻辑芯片的尺寸必须相同,这种工艺并不总是最佳的选择,特别是对于大光学格式(a large optical format),另一种堆叠方法涉及 CoW 键合,如图 5 所示。当尺寸与光学格式(optical format)相同的逻辑芯片完全充满高度并行的 ADC 和数字构建块(digital building blocks)时,面积效率在 WoW 键合中是最佳的。然而,如果逻辑电路小于光学格式(optical format),则 CoW 配置有最佳的面积效率,而 WoW 配置存在成本问题。

图 5. 大型光学格式图像传感器的 WoW 和 CoW 键合工艺的面积效率。

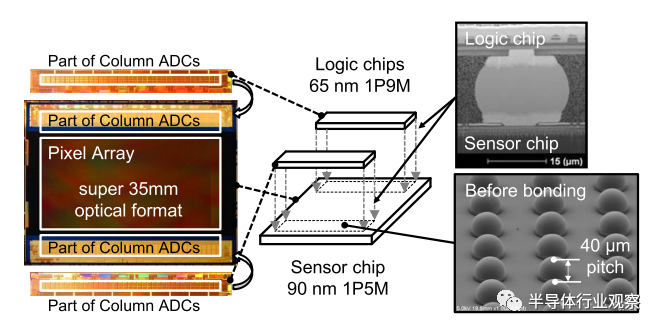

2016 年报道了一种使用 CoW 键合工艺的堆叠 CMOS 图像传感器[12],实现了具有超 35 毫米光学格式(optical format)的广播摄像机的全局快门图像传感器。在这里,两个切开的逻辑芯片采用 65-nm CMOS 工艺设计,具有并行 ADC 和微凸块(microbumps),并堆叠在为全局快门像素定制设计的大型传感器芯片上,如图 6 所示。具有高纵横比的切开的逻辑芯片通过间距为 40 µm 的微凸块连接到传感器。因此,连接总数约为 38 000。该传感器还允许通过 800 万像素以 480 fps 的速度进行超慢动作回放。

图 6. 使用 CoW 键合工艺的堆叠式 CMOS 图像传感器。

图 7 显示了大型光学格式图像(large optical-format)传感器的性能趋势, 2021 年,全 35 毫米格式(full-35-mm-format)图像传感器具有 5000 万像素和 250 fps。为了增加并行 ADC 的数量并逐步增加静态随机存取存储器 (SRAM) 帧缓冲区,使用 WoW 工艺来实现高性能。另一方面,CoW 工艺用来平衡成本效率和大型光学格式(large optical-format)传感器的性能。2021 年还推出了 3.6 英寸图像传感器,具有 1.27 亿像素和四个使用 CoW 工艺堆叠的逻辑芯片。CoW 工艺的下一个挑战是提高晶片上芯片放置的吞吐量,以提高生产率。

图 7. 大型光学格式图像传感器的性能趋势。

03、像素并行架构

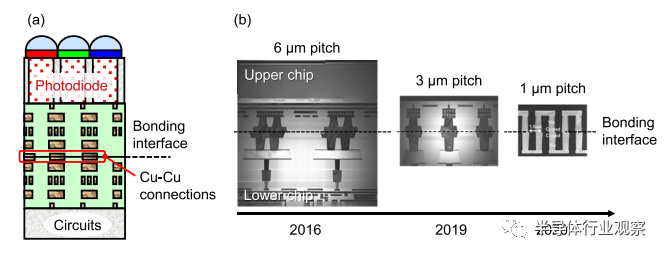

在上一节中,使用堆叠器件的传感器架构主要用于提高基于列并行 ADC 架构的帧速率。本节介绍了基于使用细间距 Cu-Cu 连接(fine-pitch Cu–Cu connections)的像素并行架构的一些进展。在这里,传感器和逻辑层之间的连接已从 TSV 更改为混合键合的 Cu-Cu 连接,如图 8(a) 所示。在 TSV 配置中,信号线被传送到像素阵列外围的逻辑层。相比之下,Cu-Cu 连接可以直接集成在像素下方,并且这些连接允许增加连接的数量。关于 Cu-Cu 连接间距的最新趋势如图 8(b)所示。图像传感器的混合键合过程中需要数百万个没有连接缺陷的 Cu-Cu 连接,而随着大量触点的稳定连接,触点间距逐渐减小;此外,最近报道了 1-µm Cu-Cu 混合键合间距。这些细间距连接将使像素并行电路架构能够以实际的像素尺寸制造。

图 8.Cu-Cu 连接间距趋势 (a) 简化的器件结构和 (b) 横截面。

A. 堆叠像素电路扩展

文献中已经提出了许多技术和实现方式,通过像素电路扩展来提高像素性能,例如满阱容量 (FWC) 、,并实现附加功能,例如全局快门、。图 9(a) 和 (b) 分别显示了单转换增益和双转换增益的像素配置。较小的电容 CFD 会经历来自光电子的高电压摆幅,以实现低噪声读出,但它很容易被大量信号电子饱和。然而,具有双转换增益的像素通过两个转换增益之间的顺序操作切换,可以在 CFD 上实现低噪声读数,在 CDCG 上实现高动态范围 (HDR) 读数;此外,附加晶体管和电容器的面积开销通过限制像素尺寸可以减小的量限制实现高像素分辨率。2018年,提出了具有双转换增益的堆叠像素电路扩展;通过像素平行的Cu-Cu连接在底部芯片上实现了额外的电路,如图9(c)所示。通过在 20 和 200 µV/e- 的转换增益之间切换,成功显示了 1.5-µm 像素具有 83.8 dB 的动态范围和 0.8 e-rms 的低噪声。如图 10 所示,像素级堆叠电路配置已应用于电压域全局快门功能和具有双转换增益的像素。2019 年展示了快门效率超过 100 dB 的 2.2 µm 全局快门像素。具有双转换增益和电压域全局快门的最先进像素分别实现了0.8µm和2.3 µm的像素尺寸,没有像素级堆叠电路扩展;然而,堆叠像素配置仍有望为增强较小像素的像素性能。

图 9. 像素电路配置 (a) 具有单转换增益,(b) 具有双转换增益,以及 (c) 具有双转换增益并堆叠像素平行 Cu-Cu 连接。

图 10. 通过像素平行 Cu-Cu 连接堆叠的电压域全局快门的像素电路配置。

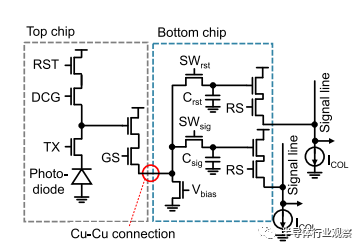

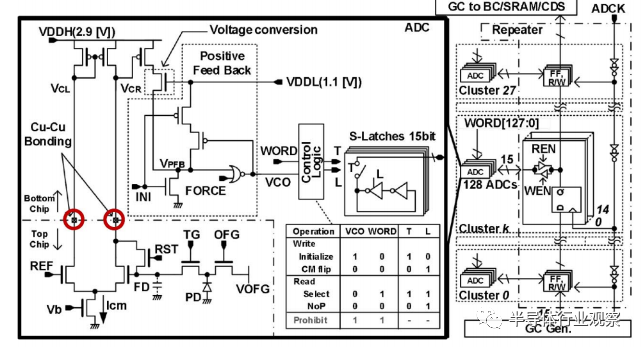

B. 像素并行 ADC

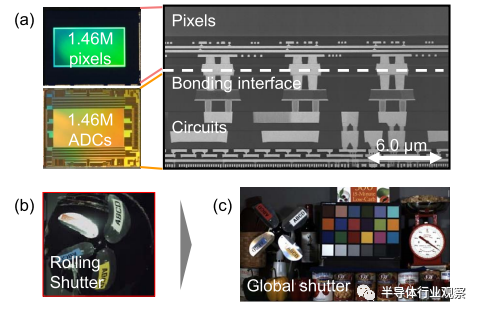

自 2001 年提出像素并行数字化概念以来,也提出了具有混合键合工艺的像素平行 Cu-Cu 连接的堆叠图像传感器。复杂电路中的像素内区域开销(within-pixel area overheads)绝对限制了像素分辨率,但 2017 年提出了具有阵列并行 ADC 架构的 410 万像素堆叠图像传感器,接着2018年提出了具有 146 万像素并行ADC的堆叠图像传感器 。由于混合键合工艺的细间距 Cu-Cu 连接,像素并行 ADC 架构已经实现了 Mpixel 分辨率。如图 11 所示,单斜率 ADC 用于像素并行和传统列并行架构,但没有源跟随器电路。像素内晶体管放大器直接集成在比较器中,通过两个 Cu-Cu 连接将每个像素连接到底部芯片。由于计数器的面积限制,格雷码被分配到像素内(in-pixel)的锁存器,数字读出管道(digital readout pipelines)已经使用像素阵列下的 ADC 实现。

图 11. 像素并行 ADC 的电路配置。

图12(a)显示了具有像素并行ADC架构的原型芯片;尽管每个 ADC 仅以 6.9 µm 的像素间距实现,其中比较器的静态电流限制为 7.74 nA,但由于有效的带宽控制,本底噪声被抑制到 8.77 e−rms。所有像素并行 ADC 同时作为全局快门运行;因此,如图 12(c) 所示,在使用原型捕获的图像中没有观察到如图 12(b) 所示的滚动快门焦平面失真。仍在继续开发像素并行 ADC 架构。2020 年的最新的一项工作显示像素间距为 4.6 µm,动态范围为 127-dB,噪声为 4.2e−rms,一项工作像素间距为 4.95 µm,噪声为 2.6e−rms。

图 12. 像素并行 ADC 的芯片实现。(a) 芯片显微照片。(b) 使用滚动快门操作和 (c) 使用全局快门操作捕获的图像。

C. 像素平行光子计数器

光子计数成像,也称为量子成像,是一种实现具有无噪声读出和 高动态范围成像(HDR) 的图像捕获的有前途的技术。使用单光子雪崩二极管 (SPAD) 的光子计数图像传感器是通过堆叠技术实现像素并行数字化的挑战之一。雪崩电流由单个光电子触发,在没有来自模拟前端电路的任何噪声的情况下,该事件可以数字化地视为光子计数。这需要为每个 SPAD 实现复杂的电路;而具有像素连接的堆叠器件结构具有高度集成的光子计数成像的潜力。

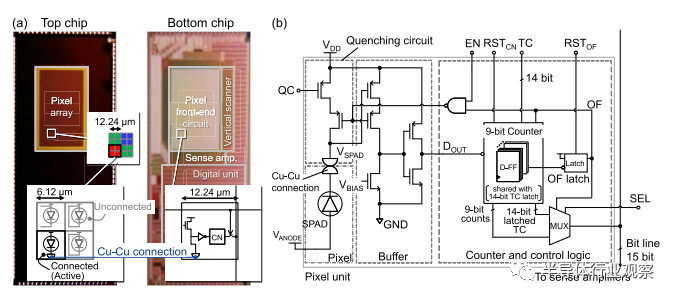

2021 年报道了一种动态范围为 124 dB 并使用子帧外推架构(subframe extrapolating architecture)的 SPAD 光子计数图像传感器 。一个背照式( BI) 单光子雪崩二极管(SPAD )像素阵列堆叠在底部芯片上,读出电路通过像素平行的 Cu-Cu 连接,如图 13(a) 所示。图13(b)是像素单元的简图。每个像素都有一个 9-b 数字纹波计数器 (CN),用于计算入射光子的数量。来自计数器的溢出进位 (OF) 返回到淬灭电路以控制 SPAD 激活并锁存时序代码 (TC)。然后将 14-b时序代码 (TC) 分配给所有像素,并在 OF 标志发生变化时覆盖计数器,如图 14 的时序图所示。读出光子的 9-b 计数或锁存的 14-b TC,并且在弱光条件下准确获得所有光子计数,而不会出现计数器溢出。但是,当计数器在高光条件下溢出时,溢出像素会记录时间,并外推整个曝光期间的实际入射光子数。

图 13. 光子计数图像传感器。(a) 芯片配置。(b) 简化的像素电路图。

图 14. 光子计数与子帧外推的时序图。

如图 15(a) 所示,已经证明了 124 dB 的动态范围,信噪比 (SNR) 没有任何下降。在高光条件下计数器溢出后的 SNR 在扩展的动态范围内保持在 40 dB,因为真正的光子计数操作可以计数多达 10 240 个光子,即 9 位 × 20 子帧。图 15(b) 显示了以 250 fps 拍摄的 HDR 图像;由于全局快门和 20 子帧 HDR 操作,即使使用 225 rpm 的旋转风扇,也没有观察到运动伪影。20 子帧外推有效地抑制了运动伪影,如图 15(c) 所示。SPAD 需要大约 20 V 的高偏置电压以及低电源电压下的像素并行触发检测器。由于不同电源电压之间的器件隔离,通常难以实现具有小间距的 SPAD 像素。然而,堆叠器件结构有效地分离了 SPAD 和 CMOS 逻辑层,从而加速了具有 SPAD 和扩展功能的小像素配置的开发。

图 15. 光子计数的测量结果。(a) 动态范围和信噪比。(b) 捕获的 HDR 图像。(c) 具有运动伪影抑制的捕获图像。

04、传感能力的扩展

除了之前介绍的动态范围和全局快门功能之外,堆叠设备技术不仅增强了传感器架构的图像质量,还增强了传感功能,例如空间深度、时间对比传感和不可见光成像。

A. 空间深度

如第 III-C 节所述,具有 Cu-Cu 混合键合的堆叠器件结构是实用 SPAD 技术在广泛应用中的一种有前景的方法,并将 SPAD 像素间距减小到小于 10 µm。为了提高光子检测效率 (PDE) 并减少小像素间距的光学串扰,2020 年报道了一种包含全沟槽隔离 (FTI) 和 Cu-Cu 键合的 BI SPAD 像素阵列 。如图 16 所示,在 BI 堆叠 SPAD 结构中,SPAD 像素阵列对入射光完全开放,所有像素晶体管都在底部芯片上实现。金属埋入式 FTI 有助于抑制与相邻像素的串扰。10-µm 间距 SPAD 像素具有 7-µm 厚的硅层,以提高近红外 (NIR) 光谱测量的灵敏度,并在 850 nm 和 940 nm 处分别实现了31.4% 和 14.2%以上的高 PDE。

图 16. SPAD 器件结构。(a) FI SPAD。(b) BI-stacked SPAD。

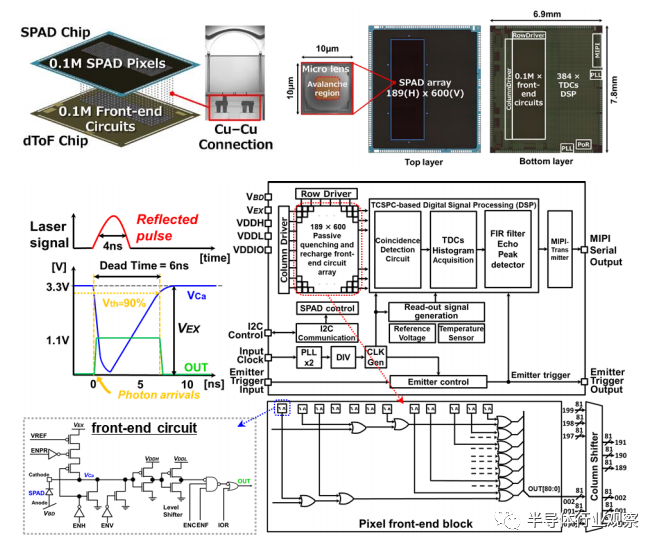

据报道,2021 年,一种使用了 BI 堆叠 SPAD, 189 × 600 SPAD 直接飞行时间 (ToF) 传感器 用于汽车 LiDAR 系统。所有的像素前端电路都在SPAD阵列下的底层芯片中实现,如图17所示。在 LiDAR 系统中,当接收到反射的激光脉冲时,SPAD 会在 6 ns 的死区时间内产生一个触发脉冲,并将其传送到时间数字转换器 (TDC)。顶部和底部芯片分别使用具有 10 个铜层的 90-nm SPAD 和 40-nm CMOS 工艺。由于采用堆叠结构,传感器包括重合检测电路、TDC 和数字信号处理器 (DSP) 作为深度感测的构建模块。直接 ToF 传感器在高达 200 m 的扩展范围内表现出 30 cm 的距离精度,使其能够在 117k 勒克斯的阳光条件下检测具有 95% 反射率的物体。

图 17. 带有直接 ToF 深度传感器的 BI 堆叠 SPAD。

BI堆叠SPAD结构是基于SPAD的成像和深度传感的突破,具有改进的特性。与将电路放置在每个 SPAD 旁边的传统像素相比,BI 堆叠结构提高了量子效率,并将 SPAD 和电路分成最佳硅层。因此,堆叠实现克服了 SPAD 传感器的传统限制,适用于更广泛的应用。

B. 时间对比传感

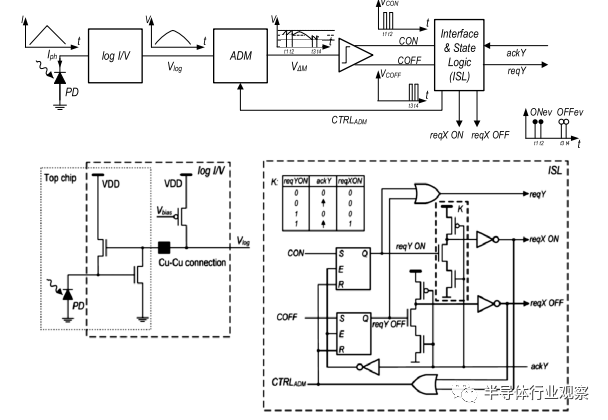

基于事件的视觉传感器 (EVS) 检测超过预设相对阈值的单个像素时间对比度,以跟踪相对光变化的时间演变,并为绝对强度的无帧像素级测量定义采样点。自 2006 年首次报告 EVS以来,已经提出了许多使用 EVS 的应用,例如由于记录数据的时间精度导致的高速低功耗机器视觉、对时间冗余的固有抑制导致减少后处理成本和广泛的场景内 DR 操作 。尽管像素尺寸在 2019 年通过 BI 结构减小到 9 µm 的间距,但由于大量像素级模拟信号处理,EVS 遭受了大像素尺寸和通常小分辨率的困扰。因此,EVS 特别受益于具有像素级 Cu-Cu 连接的堆叠器件结构的进步。

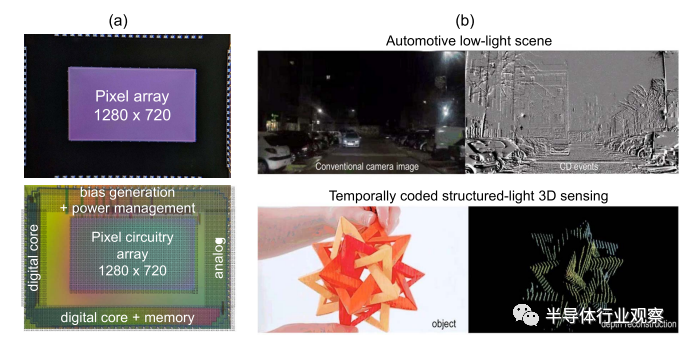

2020 年报道了 1280 × 720 4.86-µm 像素间距 BI 堆叠 EVS。图 18 显示了对比度检测 (CD) 功能的像素框图以及像素内异步读出接口和状态逻辑块的示意图。光电流被转换为电压信号 Vlog,然后通过使用电平交叉比较器检测的异步增量调制 (ADM) 获得对比度变化。图 19(a) 中的 BI-stacked EVS 实现了 1-µs 行级时间戳、每秒 10.66 亿个事件 (eps) 的最大事件率,以及 35 nW/像素和 137 pJ/事件的数据格式化流水线 用于高速低功耗机器视觉应用。图 19(b) 显示了一些示例应用的传感器操作。大约 1 勒克斯的交通场景记录展示了低光对比敏感度。低延迟像素和高速读出操作带来的高时间精度允许传感器在 3D 深度传感应用中解码时间编码的结构光图案。图 20 显示了 EVS 中像素间距的趋势。由于堆叠设备技术,对于百万像素的实际使用案例EVS 的像素尺寸现在低于 5 µm 间距。

图 19. BI-stacked EVS 及其应用示例。(a) 芯片显微照片。(b) 应用实例。

图 20. EVS 中像素间距的趋势。

C. 不可见光成像

堆叠器件技术还有助于在混合集成中使用非硅光电探测器实现不可见光成像。具有混合集成的非硅光电探测器的示例包括 InGaAs 光电探测器、Ge-on-Si光电探测器和有机光电导膜。在本节中,总结了使用 Cu-Cu 混合键合的 InGaAs 传感器的最新成果。

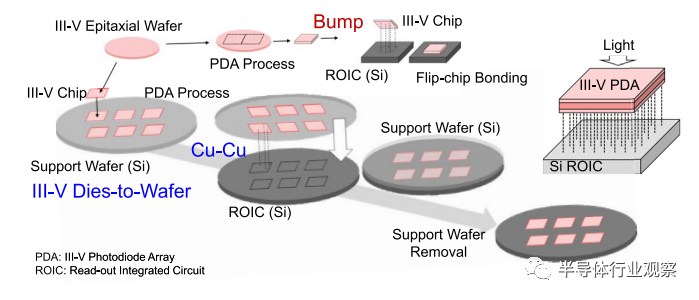

工业、科学、医疗和安全应用对短波红外 (SWIR) 范围(即 1000 到 2000 nm 之间的波长)成像的需求一直在增加。InGaAs 器件已用于 SWIR 传感器,因为它们在 SWIR 范围内的吸收特性是硅基器件无法覆盖的。在传统的 InGaAs 传感器中,光电二极管阵列 (PDA) 的每个像素通过使用凸块的倒装芯片混合连接到读出集成电路 (ROIC)。由于凸块的可扩展性有限,这种结构通常使细间距像素阵列的制造复杂化。2019 年,推出了一种 InGaAs 图像传感器,其中 PDA 的每个 5-µm 像素使用 Cu-Cu 键合连接到 ROIC。InGaAs/InP 异质结构在直径小于 4 的市售小型 InP 衬底上外延生长。如图 21 所示,外延 InGaAs/InP 晶圆被切割成芯片,并使用 III-V 裸片到硅晶圆工艺转移到大型硅晶圆上。在制造 Cu 焊盘后,III-V/Si 异质晶片使用 Cu-Cu 键合将每个 III-V 像素连接到 ROIC 与 ROIC 混合。图 22 显示了倒装芯片凸块的接触间距趋势和 InGaAs 传感器的 Cu-Cu 键合。使用凸块的倒装芯片混合是制造 InGaAs 传感器的传统方法,由于工艺裕度窄且可重复性差,不适合按比例缩小像素间距。然而,自 2016 年以来,Cu-Cu 杂化已用于 CMOS 图像传感器的大规模生产并具有高产量,是缩放互连到 InGaAs 传感器的关键技术。图 22 还显示了在有雾的场景中涉及检查和安全监控的应用示例。因此,InGaAs 图像传感器通过像素级 Cu-Cu 连接为 HD SWIR 成像创造了条件。

图 21. InGaAs 图像传感器制造的工艺流程图。

图 22. 倒装凸块接触间距趋势和 Cu-Cu 键合以及 InGaAs 传感器的应用实例。

05、智能视觉传感器

在物联网 (IoT) 市场、零售、智慧城市和类似应用中,对具有 AI 处理能力的相机产品的需求正在增长。此类边缘设备上的 AI 处理能力可以解决与纯云计算系统相关的一些问题,例如延迟、云通信、处理成本和隐私问题。具有AI处理能力的智能相机的市场需求包括小尺寸、低成本、低功耗和易于安装。然而,传统的 CMOS 图像传感器仅输出捕获图像的原始数据。因此,在开发具有AI处理能力的智能相机时,需要使用包含图像信号处理器(ISP)、卷积神经网络(CNN)处理、DRAM等能力的IC。

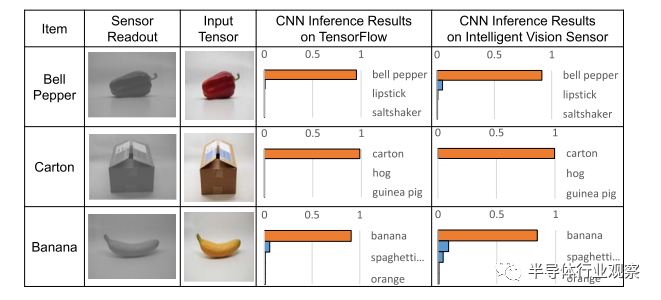

2021 年报道了一种由 1230 万像素和一个专用于 CNN 计算的 DSP 组成的堆叠 CMOS 图像传感器。如图 23 所示,该传感器包含一个集成解决方案,该解决方案具有完整的图像捕获传输到 CNN 推理处理器,并且可以以 120 fps 的速度处理,包括使用 4.97 TOPS/W DSP 的图像捕获和片上 CNN 处理。处理模块有一个用于 CNN 输入预处理的 ISP、一个为 CNN 处理优化的 DSP 子系统,以及一个用于存储 CNN 权重和运行时内存的 8-MB L2 SRAM。图 24 显示了使用 MobileNet v1 的 CNN 推理结果的一些示例。DSP 子系统展示了与 TensorFlow 类似的推理结果。智能视觉传感器能够在传感器上运行完整的 CNN 推理过程,可以通过 MIPI 接口将捕获的图像作为原始数据和 CNN 推理结果输出在同一帧中。该传感器还支持仅从 SPI 接口输出 CNN 推理结果,以启用小型相机,降低系统功耗和成本。传感器上的 CNN 推理处理器允许用户将他们喜欢的 AI 模型编程到嵌入式存储器中,并根据系统使用位置的要求或条件对其进行重新编程。例如,安装在设施入口处时,可用于统计进入设施的访客人数;安装在商店货架上,可用于检测缺货情况;当在天花板上时,它可以用于热图(heat mapping)商店访客。智能视觉传感器有望使用灵活的 AI 模型为各种应用提供低成本的边缘 AI 系统。

图 23. 智能视觉传感器系统框图。

图 24. CNN 推理的测量结果。

06 、结论

本文回顾了具有堆叠器件结构的图像传感器架构的最新成果。通过采用传感器像素和 CMOS 电路优化工艺技术实现的高度并行 ADC,堆叠器件结构极大地提高了图像传感器性能,特别是在高帧速率和高像素分辨率下。在最近的工作中,已经使用像素并行堆叠电路和/或更智能的处理单元提出了一些建议,并取得了一些成果。这些新挑战需要更高的可扩展性、针对每个功能的工艺技术的更多优化以及更高的面积效率。光电探测器、像素前端电路、模拟混合信号和数字处理器以及存储器可以更有效地集成,如图 25 所示,未来图像传感器架构通过器件堆叠技术扩展功能将获得进一步的发展。

图 25.堆叠式 CMOS 图像传感器的演进与未来展望。

的用法)

的使用说明)