前言

AD9528是ADI的一款时钟芯片,由2-stage PLL组成,并且集成JESD204B/JESD204C SYSREF信号发生器,SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,从而可以实现多器件之间的同步。

AD9528总共有14路输出,6路输出(Output 0 - Output 3,Output 12, Output 13)最高可达1.25 GHz, 其余8路输出最高可达1 GHz。每一路输出均可配置为从PLL1,PLL2或内部SYSREF发生器输出。每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟精调相位延迟模块,可以灵活分配14路输出为 device clock/ SYSREF信号的组合。

Functional Block Diagram:

PLL1

PLL1 Block Diagram

PLL1 支持外部压控晶体振荡器(VCXO),外部REFA和REFB参考时钟。VCXO和参考时钟支持LVDS和COMS两种可选的输入电平。两路参考时钟输入和VCXO输入路径上分别有数字时钟分频器( R A R_A RA, R B R_B RB, N 1 N1 N1) 。

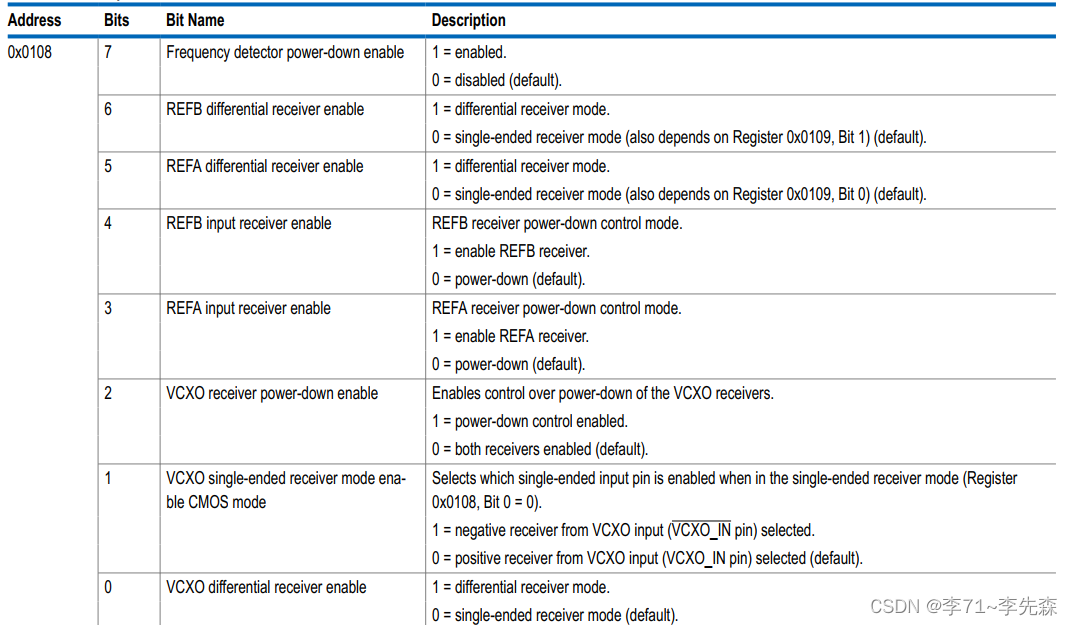

参考输入的选择可以通过寄存器0x0108进行控制:

REFA和REFB参考时钟输入的选择支持引脚控制和软件控制两种模式,通过寄存器0x010A进行控制:

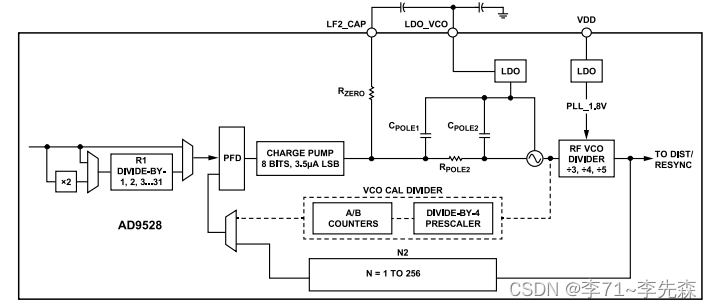

PLL2

PLL2 Block Diagram

输入的reference来自VCXO,内部有一个内置的VCO(压控振荡器),输出频率范围为:3.45GHz - 4.025 GHz。

Clock Distribution

14路输出可以选择配置为PLL1 output, PLL2 output或者SYSREF。

Clock Distribution Control regster地址从0x0300到0x0329,以Output 0为例子,0x0300寄存器比特[7:5]来配置输出信号的来源:

结语

最后附上AD9528裸机驱动程序地址:https://github.com/analogdevicesinc/no-OS/tree/master/drivers/frequency/ad9528

![11.与JavaScript深入交流-[js一篇通]](http://pic.xiahunao.cn/11.与JavaScript深入交流-[js一篇通])

)