1、时钟相移

时钟相移对应于延迟时钟波形 , 此波形与因时钟路径内的特殊硬件所导致的参考时钟相关。在 AMD FPGA 中 , 时钟相移通常是由 MMCM 或 PLL 原语引入的 , 前提是这些原语的输出时钟属性 CLKOUT*_PHASE 为非零值。

时序分析期间 , 可通过设置 MMCM/PLL PHASESHIFT_MODE 属性以两种不同方式对时钟相移进行建模 ,

2、时序报告中的相移

正相移将源时钟沿向前移动 , 导致时钟沿延迟。负相移将源时钟沿向后移动。修改时钟波形导致静态时序分析可能对源时钟和捕获时钟使用不同的时钟沿。

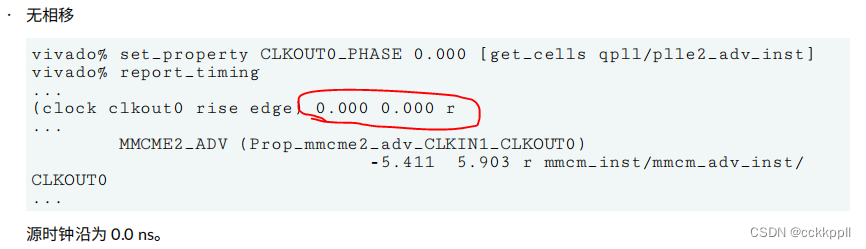

红色圈内为相移时间。

3、时钟偏差和不确定性

偏差和不确定性都会影响建立和保持时间的计算和裕量。

时钟偏差表示目标时钟路径与源时钟路径之间 : (1) 从设计中两条路径的公共点 ; (2) 分别到端点和起点时序单元时钟管脚的插入延迟。

典型时序路径报告可显示源时钟路径和目标时钟路径从时钟根到时序单元时钟管脚的延迟详情。

时钟不确定性表示任意成对时钟沿之间可能存在的时间变化总量。不确定性由如下部分组成 : 计算所得时钟抖动 ( 系统抖动、输入抖动和离散抖动) 、某些硬件原语引入的相位误差以及用户在设计约束中指定的任意时钟不确定性 (set_clock_uncertainty ) 。

对于基准时钟 , 抖动由 set_input_jitter 和 set_system_jitter 定义。对于时钟生成器 ( 如 MMCM 和

PLL ), 该工具会基于其源时钟及其配置上的用户指定的抖动来计算抖动。对于其他生成时钟 ( 例如 , 基于触发器的时钟分频器), 抖动与其源时钟的抖动相同。用户指定的时钟不确定性将与 AMD Vivado ™ Design Suite 时序引擎计算所得不确定性相加。对于生成的时钟 ( 例如 ,从 MMCM 、 PLL 和基于触发器的时钟分频器生成的时钟 ), 用户在源时钟上指定的不确定性不会通过时钟生成器传输。

时钟不确定性有如下 2 个用途 :

• 在裕量数值中保留一定量的裕度 , 用于表示时钟上可能影响硬件功能的任何噪声。由于延迟和抖动数值为保守估值, AMD 不建议额外增加不确定性以确保硬件功能正常。

• 在 1 个或多个实现步骤内 , 可对时钟或时钟对相关路径进行过约束。这样可增加 QoR 裕度 , 以便用于帮助后续步骤在这些路径上达成时序收敛。使用时钟不确定性时, 不会修改时钟波形及其关系 , 因此仍可正确应用其余时序约束。

4、脉冲宽度检查

脉冲宽度检查属于针对信号波形的规则检查 , 在波形传输穿越器件并到达硬件原语时执行。这些检查通常对应于原语内部电路所规定的功能限制。例如, DSP 时钟管脚上的最小周期检查可确保驱动 DSP 实例的时钟的运行频率不高于内部DSP 可承受的频率。

脉冲宽度检查不影响综合或实现。其分析必须在生成比特流之前执行一次 , 就像 Vivado Design Suite 所提供的所有其他设计规则检查一样。发生脉冲宽度违例时, 原因可能是时钟定义错误 ( 脉冲宽度和周期检查 ), 或者因时钟拓扑错误而导致偏差过大 (max_skew 检查 )。