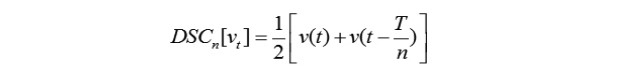

微❤关注“电气仔推送”获得资料(专享优惠)

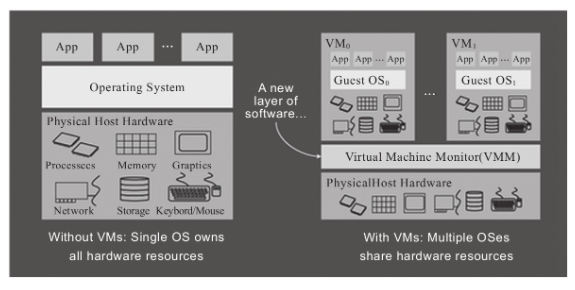

基于级联型延迟信号消除(CDSC)的锁相环技术(CDSC-PLL),该锁相环克服了传统dq 锁相环在电网电压畸变或不对称时存在较大稳态误差的缺点。CDSC-PLL是在传统dq锁相环的控制环节中加入了一个 CDSC环节,即dqCDSCPLL。

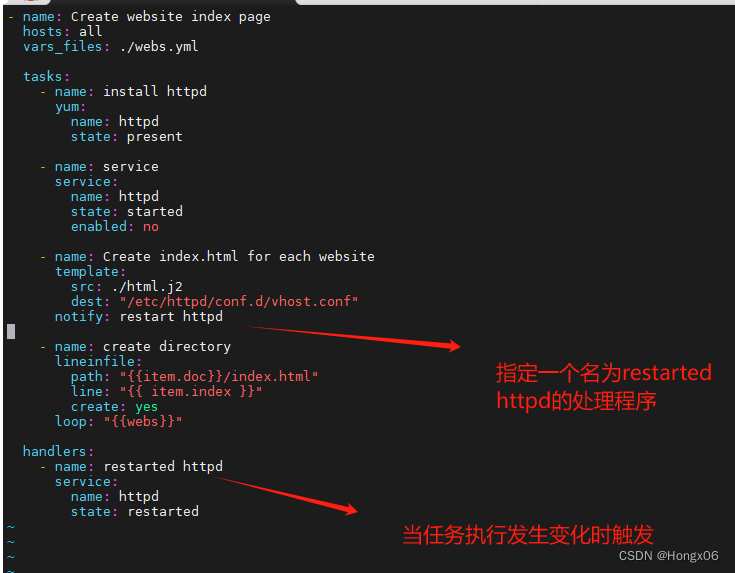

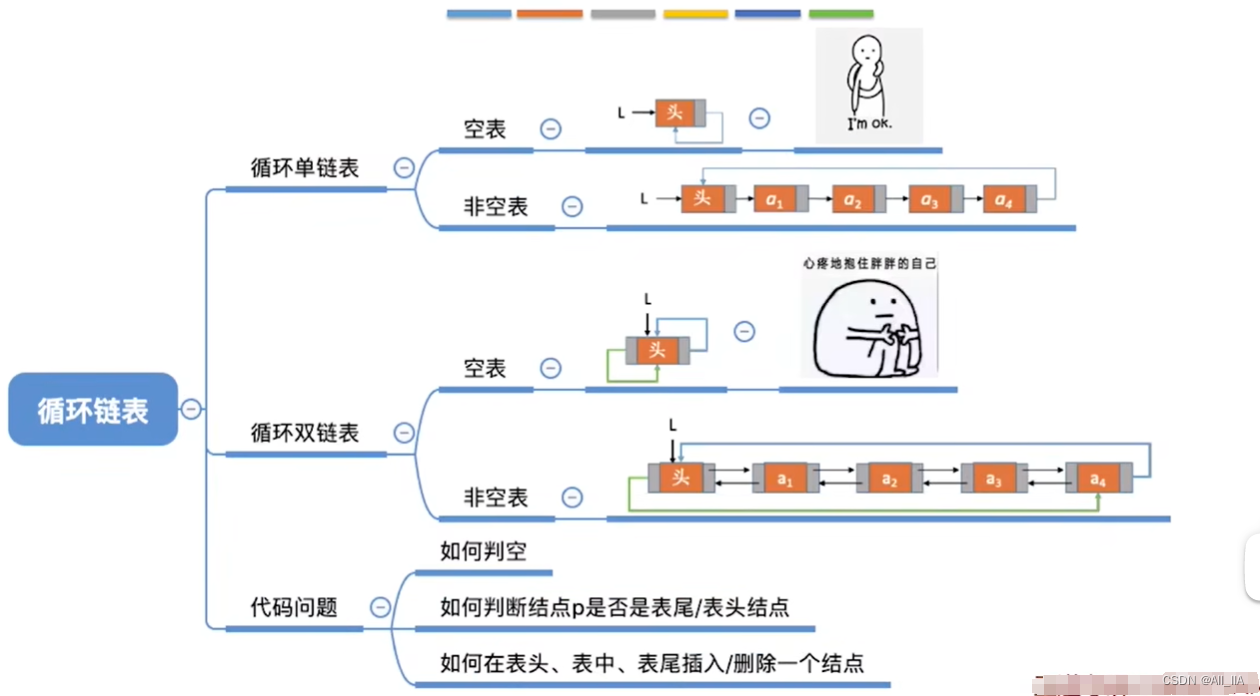

基于延迟信号消除的锁相环原理

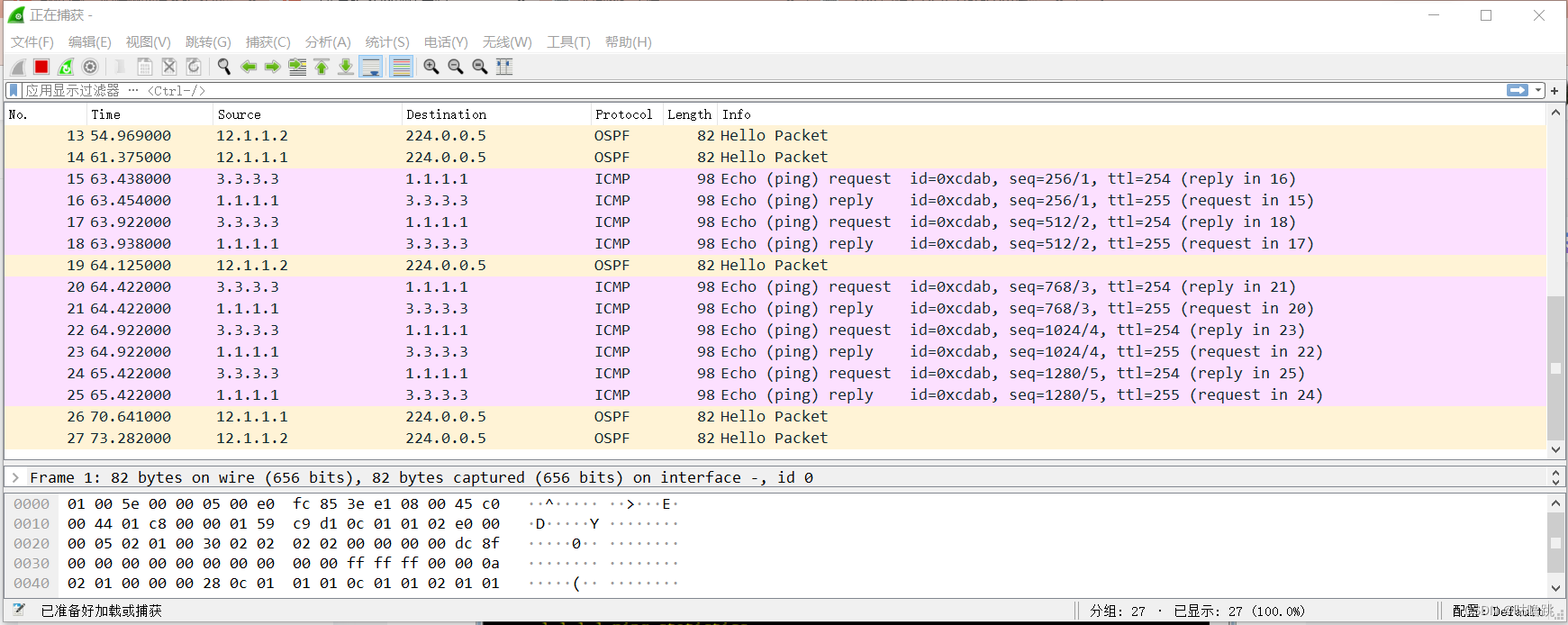

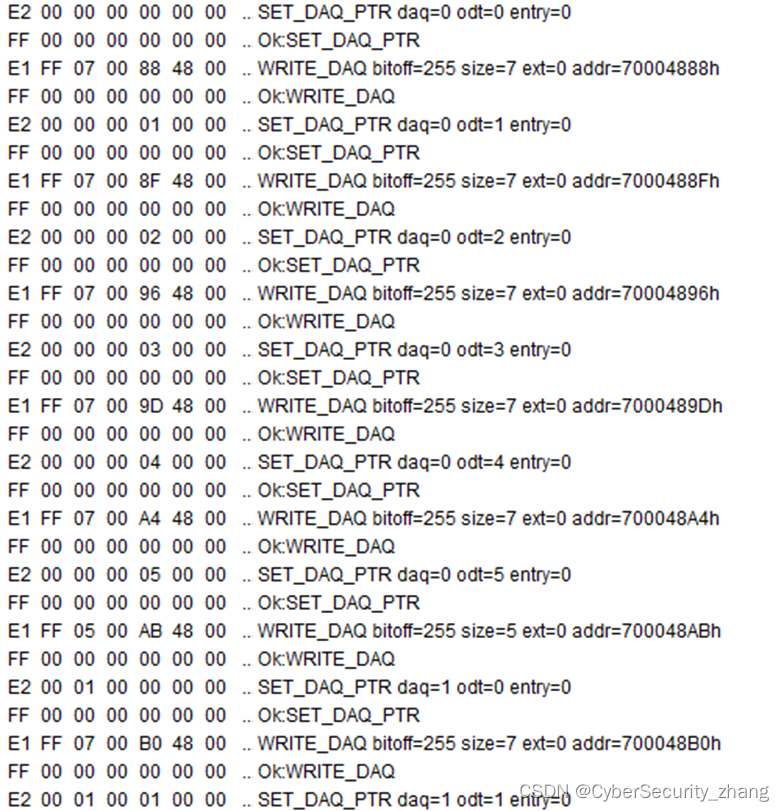

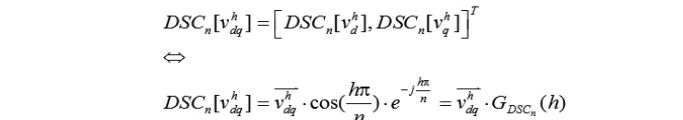

通过谐波的半波对称性在dq坐标系中将谐波消除, 也即延迟信号消除(DSC)法,将输入的谐波信号延迟 正序基波信号周期T的1/n倍,然后取原信号和延迟信号 和的平均值作为输出,其数学表达式如下:

T表示正序几波分量的周期。

在dq坐标系中延迟信号消除(DSC)的具体过程以及 在dq坐标系中d轴的h次谐波在时域内的表达式如下所示:

![]()

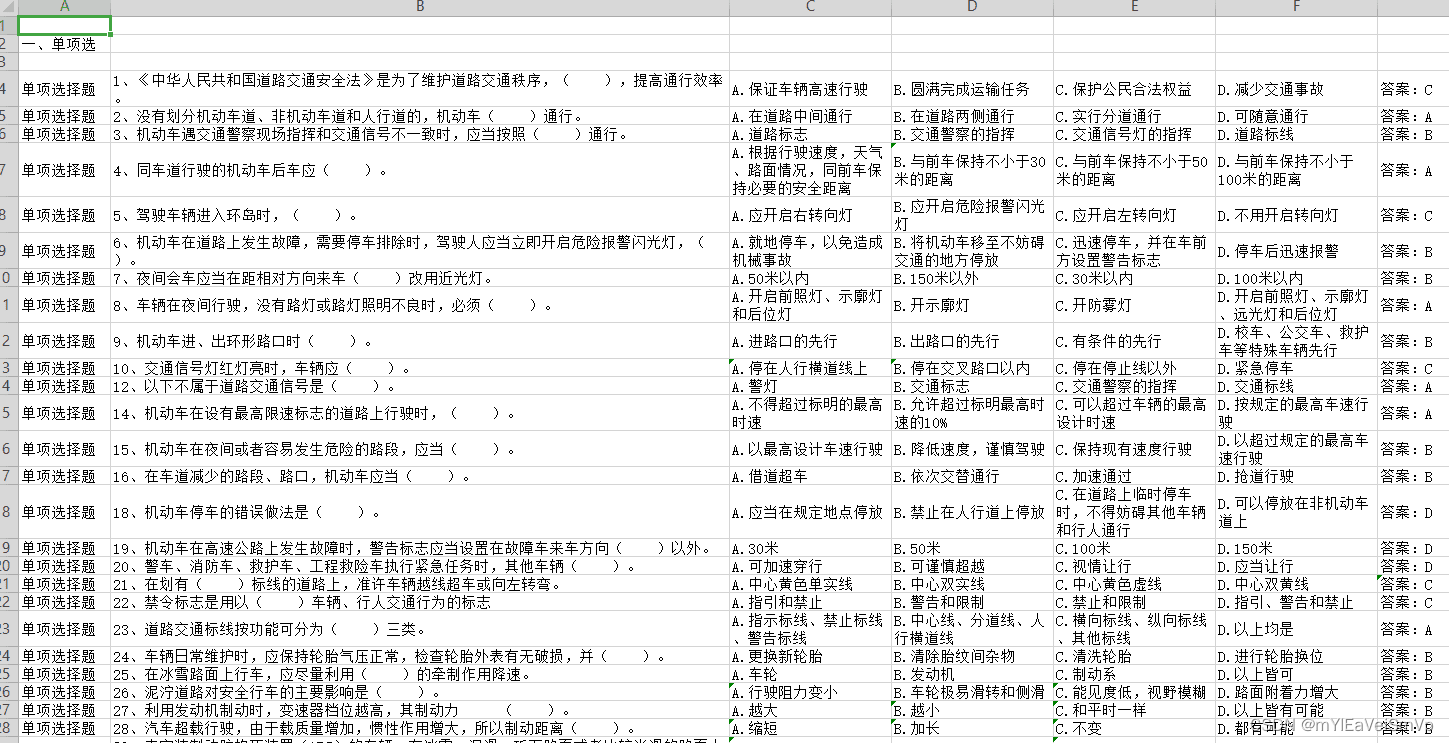

则可得:

同理,在dq坐标系中q轴的h次谐波也作类似的运 算,则dq坐标系的h次谐波经过延迟信号消除后,其表达 式(1)如下:

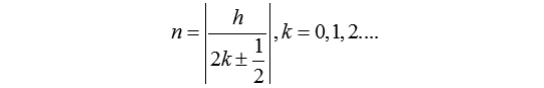

因此,只需将增益|GDSCn(h)|=0,即可在dq坐标 系中消除h次谐波,此时可求得谐波次数h和相应n之间的 关系式:

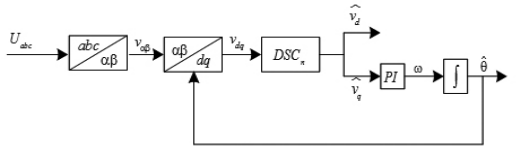

由此可得基于延迟信号消除的锁相环(dq -DSC-PLL) 原理图如下所示:

对d轴 和q轴信号延迟1/4个正序基波周期,仅能消除三相系统中 部分正序谐波分量和负序谐波分量,因此,当电网电压 畸变时,仅有一个信号延迟消除模块,并不能够消除全 部谐波,锁相环仍然存在稳态误差。

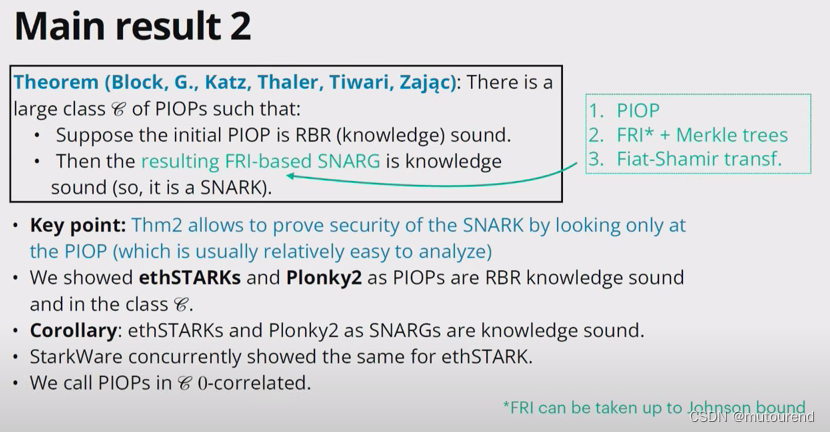

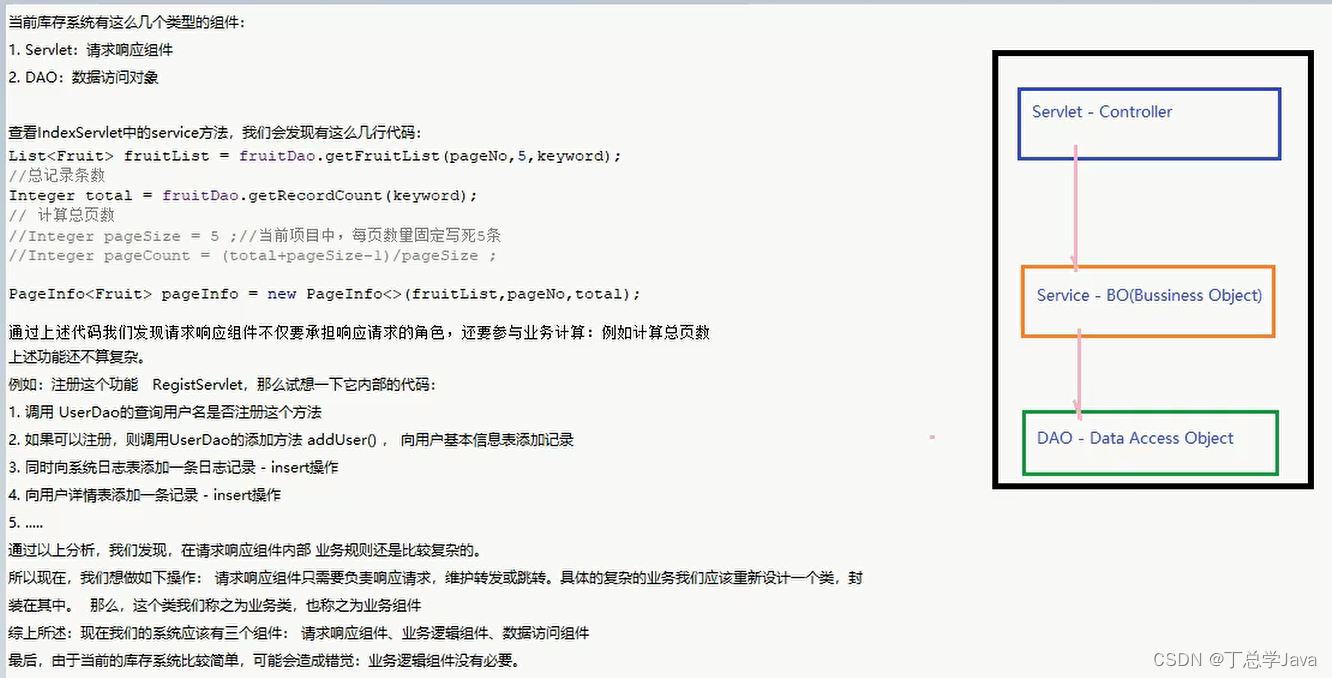

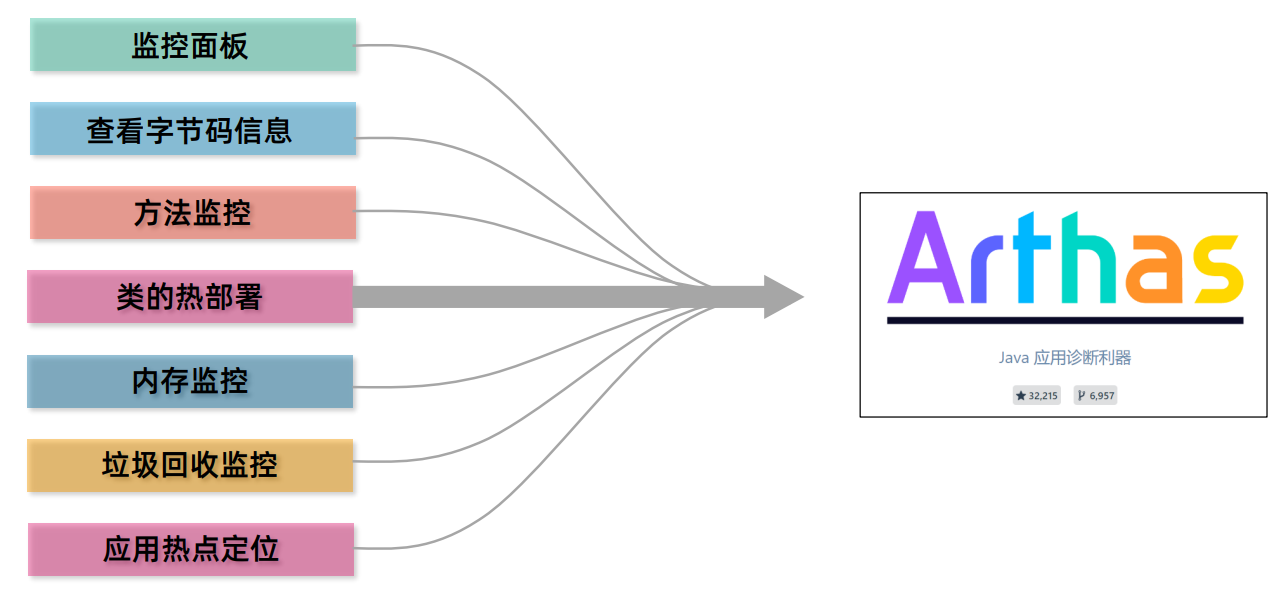

基于级联延迟信号消除的锁相环(dq_CDSC_PLL)技术

虽然k的取值多样,但是一个n值 只对应有限个h值,同时,由式(1)可以得出这样一个结 论,延迟信号消除模块的增益和信号频率无关,并且增益 总小于1,换言之,某一次谐波不能被完全消除时也会被 衰减,除此之外,延迟信号消除模块并不会改变信号的频 率,因此,可以将多个取不同n值的延迟信号消除模块串 联在一起,组成一个级联型延迟信号消除模块。

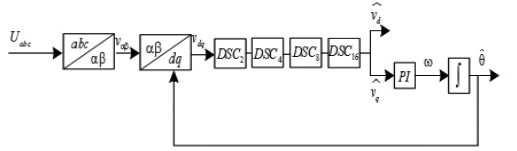

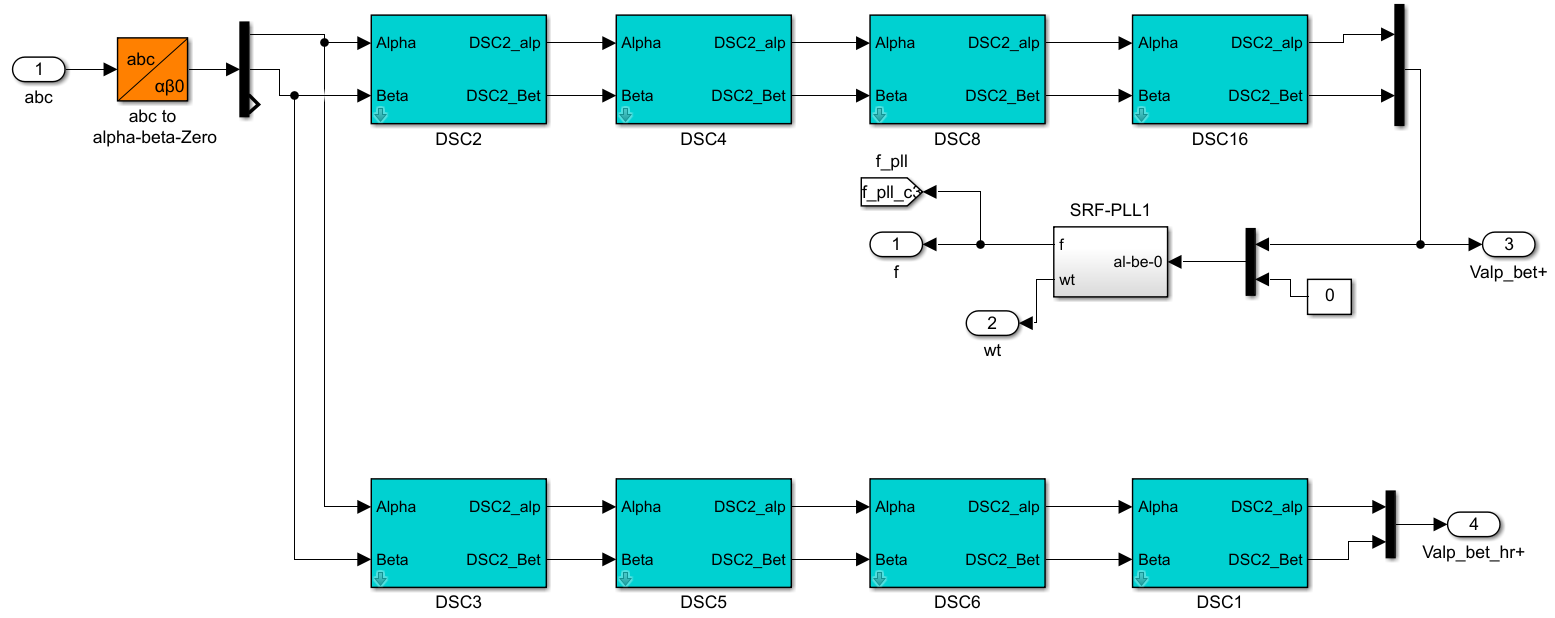

通过 选取不同的n值,将几个不同的延迟信号消除模块进行组 合级联,可以选择性的消除谐波,同时,间谐波也会被不 同程度的衰减,如果某一特定的间谐波需要消除,可以针 对该间谐波重新选取一个n值构造一个延迟信号消除模块, 并和原来的模块级联。基于级联延迟信号消除的锁相环 (dq_CDSC_PLL)(n取2,4,8,16)原理图如图4 所示:

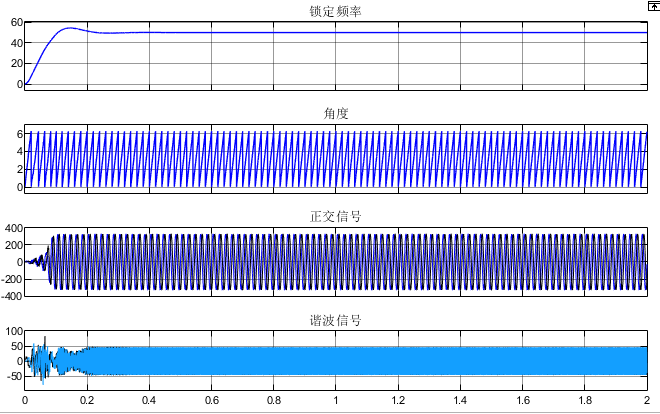

由上图,基于延迟信号消除的锁相环原理可知,每 个DSC模块都是在对原信号进行延迟1/n个正序基波信号 的基础上进行谐波消除的,每个模块都可以消除一定次 数的谐波,将模块级联在一起,即可将常见谐波基本消 除,从而提高锁相环的锁相精度以及动态响应速度。

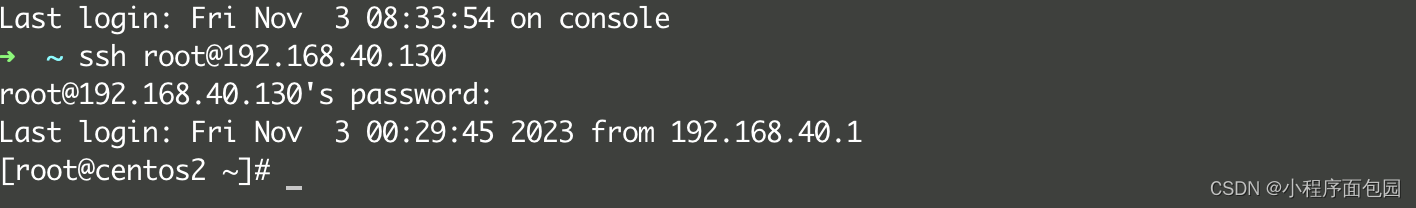

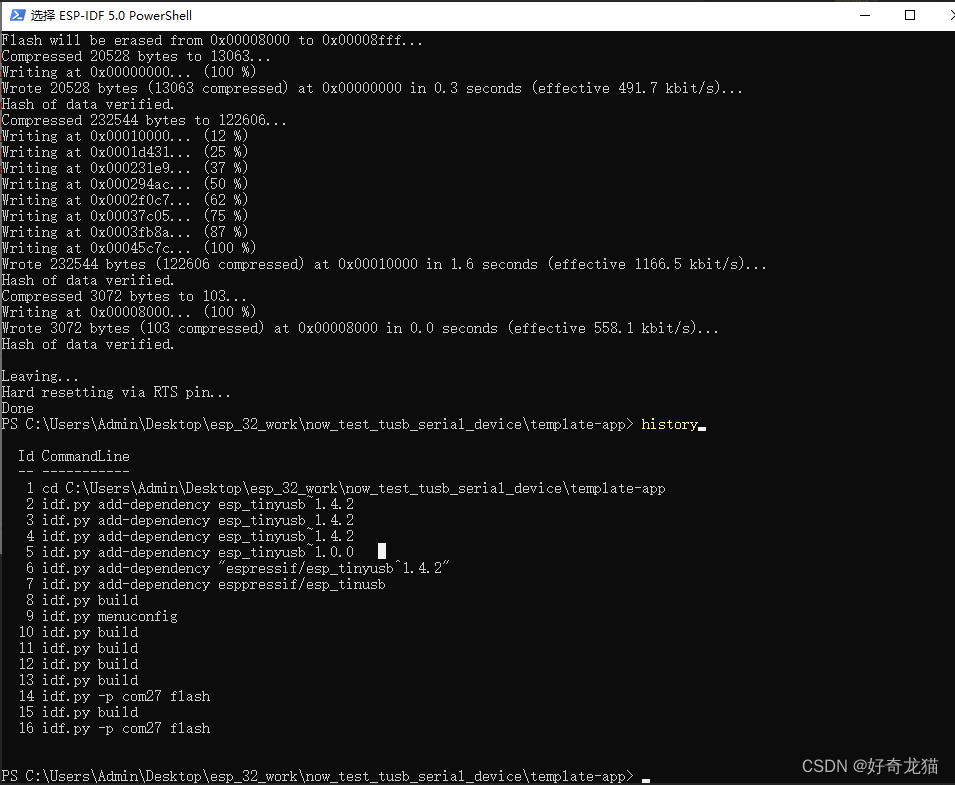

仿真模型:

参考文献:

基于CDSC的APF锁相环设计-温华生