一、 通过typedef来创建用户自定义类型

typedef语句可以用来创建新的类型。例如,你要求一个算术逻辑单元(ALU)在编译时可配置,以适应8比特、16比特,24比特或32比特等不同位宽的操作数。在Verilog中,你可以为操作数的位宽和类型分别定义一个宏(macro),如例2.32所示。

SV则提供了特性使得用户可以构建更高抽象层的数据类型。 就同C语言一样,用户可以利用已有的数据类型来定义新的数据 类型,一旦定义了新的数据类型,则此类型的变量则可以声明。

typedef int unsigned uint;

...

uint a, b; // two variables of type uint为了使代码更易读和维护,通常我们对于自定义的类型,都习惯 添加“_t”的后缀用来表示它是一个自定义类型(type)。

二、 通过enum来创建枚举类型

枚举类型(enum)提供方法来描述抽象变量的合法值范围,其每一个值都需要提供一个用户自定义的名。

Verilog语言自身不提供枚举类型,因此为了提供类似于枚举类型可实现的便利,我们不得不采用parameter常量来表示可取 的值范围,或者使用`define来定义各个合法值对应的宏名称。

默认的枚举类型是int,即32位的二值逻辑数据类型。

为了能够更准确地描述硬件,SV允许指明枚举类型的数据类型,例如:

enum bit {TRUE, FALSE} Boolean; enum logic [1:0] {WAITE, LOAD, READY} state;如果一个枚举类型数值被赋值,那么所赋的值必须符合其数据类型。

enum logic [2:0] {WAITE = 3’b001, LOAD = 3’b010, READY = 3’b100} state;如果枚举类型是四值逻辑数据类型,那么对枚举值赋为X或者Z也是合法的。

enum logic {ON=1’b1, OFF=1’bz} out; 枚举类型也可以声明为自定义类型,这就使得可以用同一个枚举类型来声明多个变量或者线网。

typedef enum {WAITE, LOAD, READY} states_t; states_t state, next_state;如果枚举类型并没有伴随着typedef,那么该枚举类型指的则是一个匿名枚举类型(anonymous enumerated type)。

多数的Verilog或者SV数据类型之间可以通过不同类型的赋值完成“隐式”的数据转换,所以Verilog/SV的数据类型转换是宽松的。

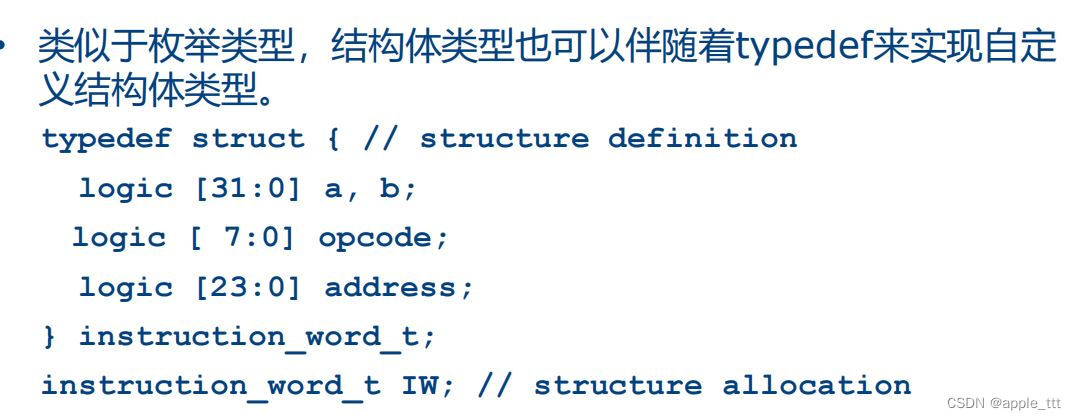

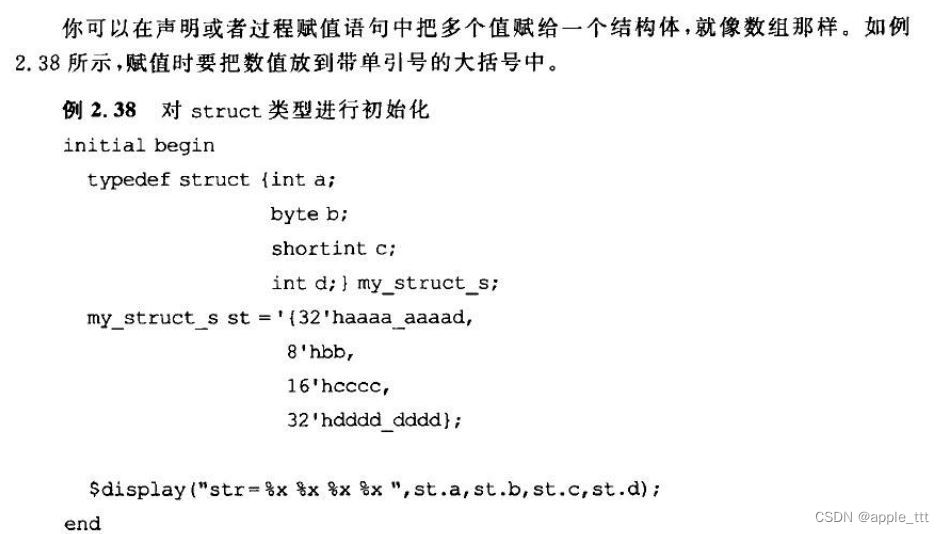

三、 通过struct来创建结构体类型

Verilog的最大缺陷之一是没有数据结构。在System Verilog中你可以使用struct语句创建结构,跟C语言类似。但struct的功能比类少,所以还不如直接在测试平台中使用类,这一点在第5章中会有详述。就像Verilog 的模块( module)中同时包括数据(信号)和代码( always/initial代码块及子程序)一样,类里面也包含数据和程序,以便于调试和重用。struct只是把数据组织到一起。如果缺少可以操作数据的程序,那么也只是解决了一半的问题。 设计或者验证的数据经常会有逻辑相关的数据信号组,例如一个总线协议的所有控制信号,或者在一个状态控制器中用到的所有的信号。所以验证语言对于结构体的支持是非常必要的。

SV添加了同C一样的结构体struct,而结构体的成员可以是任何变量类型,包括自定义类型或者其它常量类型。 结构体类型默认也是变量类型,用户也可以显示声明其为var或者wire类型。由于struct只是一个数据的集合,所以它是可综合的。如果你想在设计代码中对一个复杂的数据类型进行建模,例如像素,可以把它放到struct里。结构可以通过模块端口进行传递。

【MySQL】)

)

)

)

之nacos集群搭建)