一.FPGA内部结构

- 可编程I/O

- PLL锁相环(其作用为:分频,倍频,相位调节、占空比)

- 逻辑阵列块LAB(每个LAB由16个逻辑器件LE组成,每个LE包括一个查找表LUT和一个RAM构成。Cyclone IV EP4CE6F17C8中包含6272(392 * 16)个LE)

- 嵌入式存储单元(M9K)

- 嵌入式乘法单元(DSP:数字信号处理)

- 可编程物理连线

二.查找表结构&原理

- 结构:LUT本质是一种RAM。FPGA使用4输入LUT,所以每一个LUT可以视为是一个有4位地址线的RAM。

- 原理:通过真值表,将输入视为地址,通过查找地址找到对应计算结果输出。

三.建立时间、保持时间、亚稳态

- 建立时间:时钟上升沿来临前,输入值需要一段时间保持稳定。这段时间被称为建立时间

- 保持时间:时钟上升沿出现后一段时间,输入值不允许改变。这段时间称为保持时间

- 亚稳态:由于不满足建立时间和保持时间,触发器无法在某一个规定的时间段内达到一个可确认的状态。

消除亚稳态方式

- 1.降低系统时钟频率

- 2.使用反应更快的触发器

- 3.引用同步机制(多级触发器级联,FIFO桥接)

四.竞争和冒险

- 竞争:信号经过导线和门电路时,会产生时间延迟。当信号经过不同路径到达电路上某一点时,时间上有先后顺序

- 冒险:由于竞争引起电路输出信号中出现非预期信号,产生瞬间错误现象被称为冒险。表现为窄脉冲(毛刺)

消除毛刺的方法

- 1.修改逻辑

- 2.采用时序逻辑,时钟边沿采样

- 3.芯片外部并联电容(物理方法)

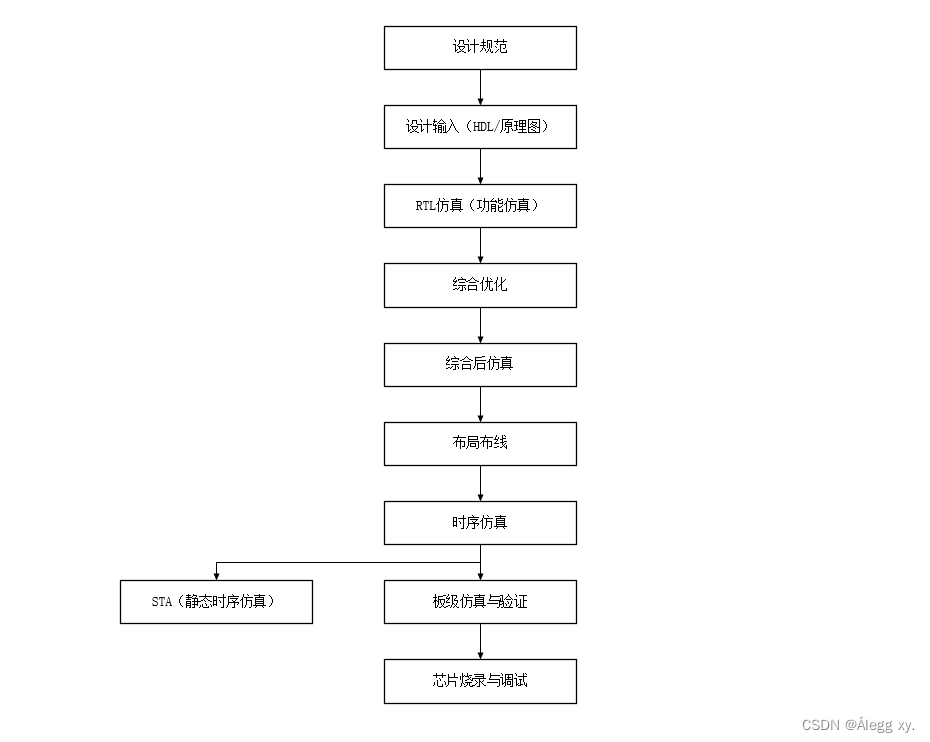

五.FPGA开发流程

- 原理图/HDL文本输入->功能仿真->综合->适配->时序仿真->编程下载->测试

- 详解如下

指针的进阶)

)